11

Изобретение относится к аналоговой и гибридной вычислительной технике и может быть использовано при построении автоматизированных сеточных интеграторов для моделирования уравнений математической физики и для решения задач управления объективами с распределенными параметрами

Цель изобретения - повьпиение точности.

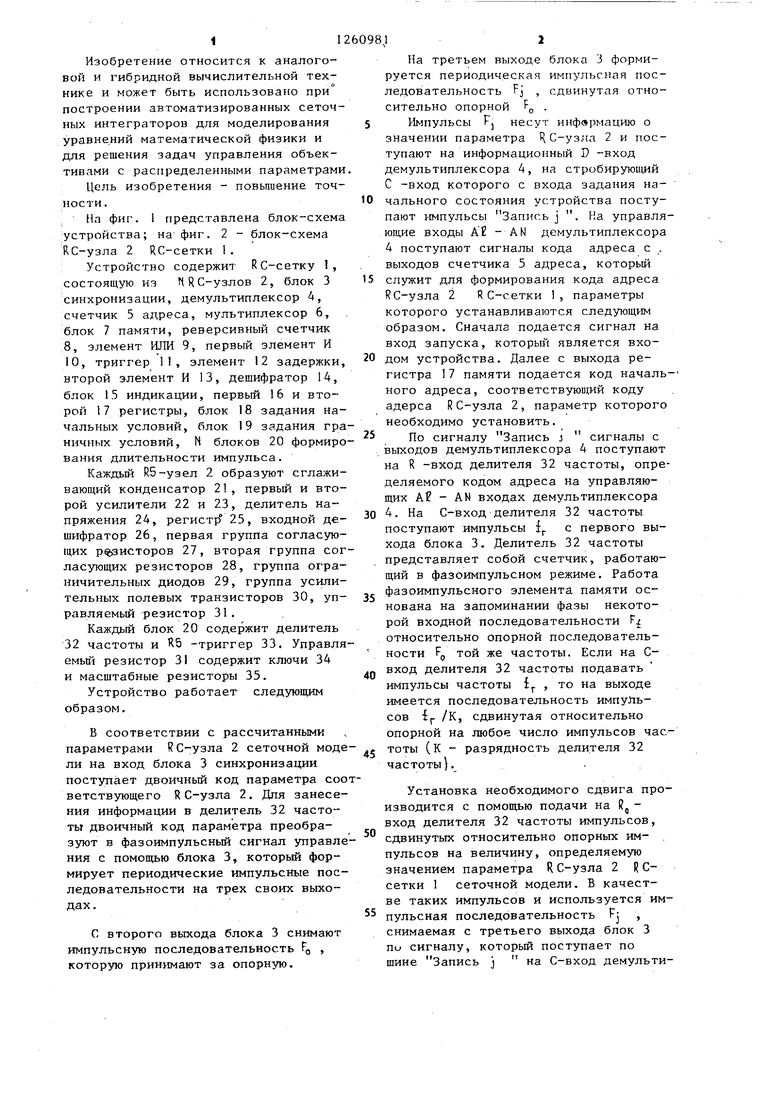

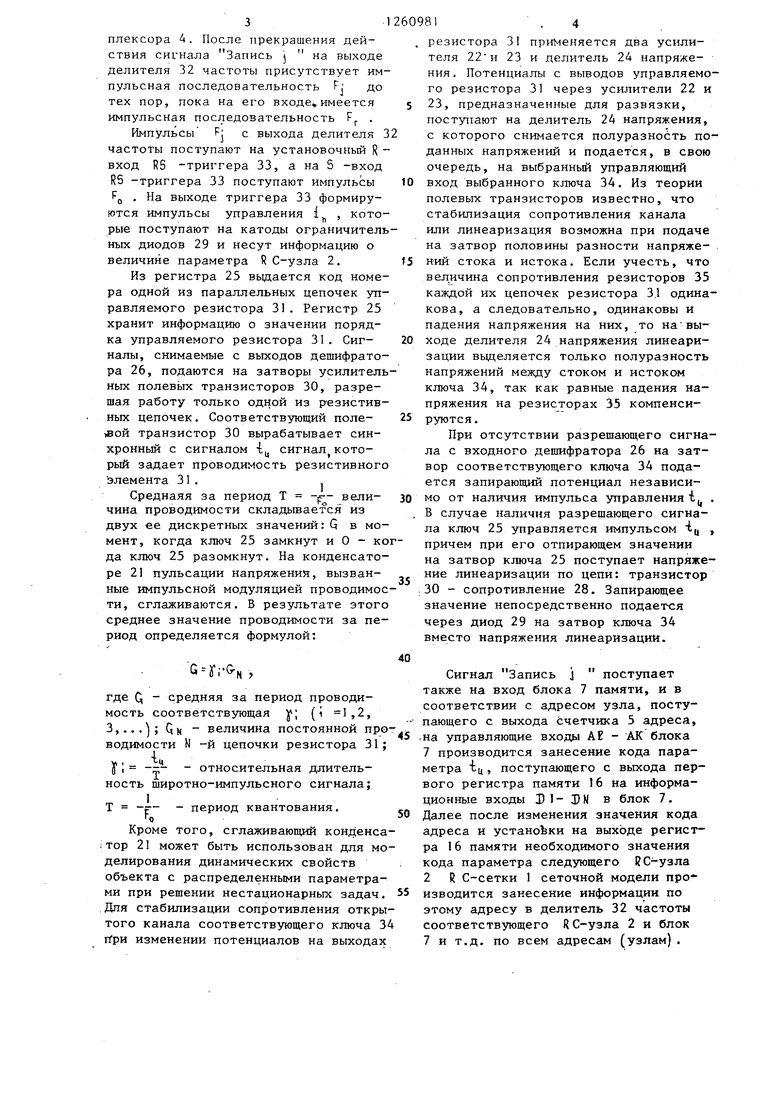

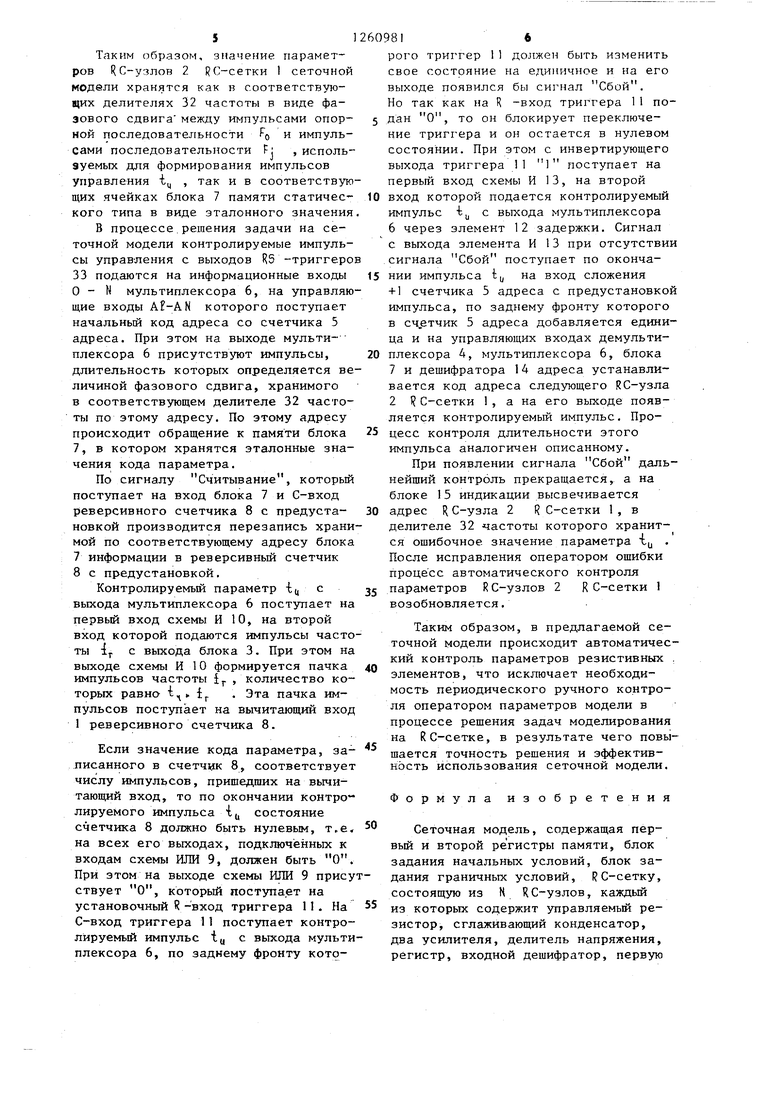

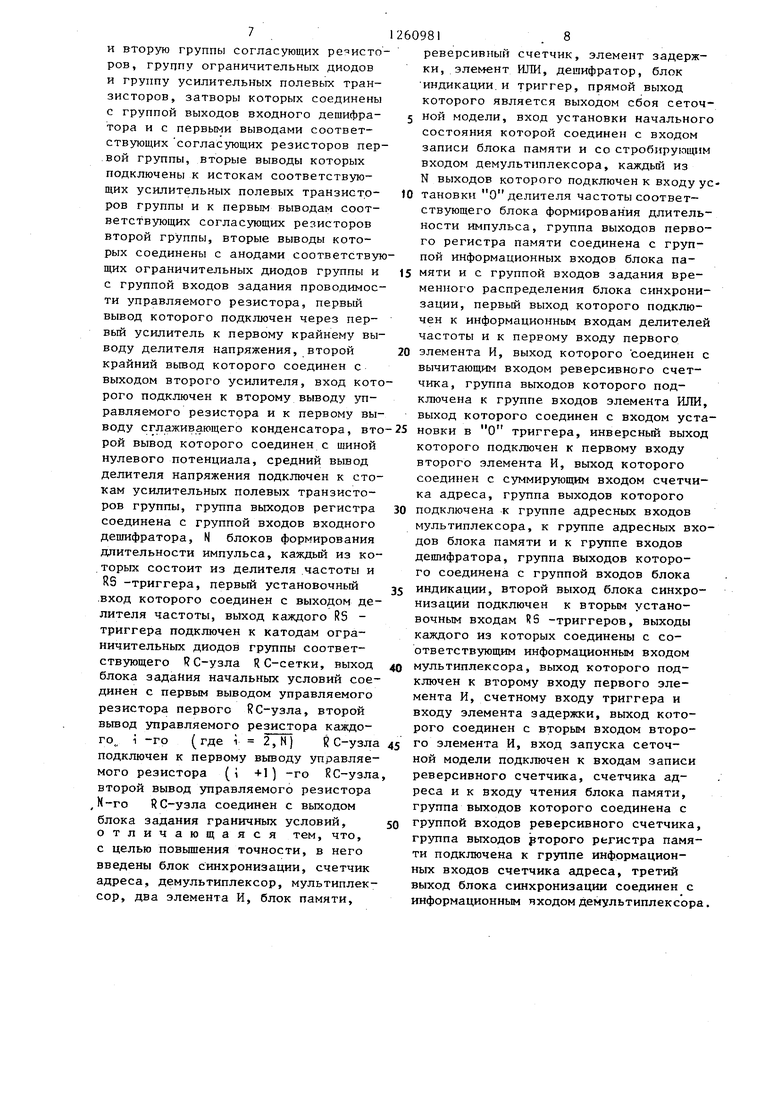

На фиг. 1 представлена блок-схема устройства; на фиг. 2 - блок-схема RC-узла 2 RC-сетки 1.

Устройство содержит RC-сетку 1, состоящую из lHRC-узлов 2, блок 3 синхронизации, демультиплексор 4, счетчик 5 адреса, мультиплексор 6, блок 7 памяти, реверсивный счетчик 8, элемент ИЛИ 9, первый элемент И 10, триггер II, элемент 12 задержки второй элемент И 13, дешифратор 14, блок 15 индикации, первый 16 и второй I7 регистры, блок 18 задания начальных условий, блок 19 задания граничных условий, N блоков 20 формирования длительности импульса.

Каждый Р5-узел 2 образуют сглаживающий конденсатор 21, первый и второй усилители 22 и 23, делитель напряжения 24, регистр 25, входной дешифратор 26, первая группа согласующих р исторов 27, вторая труппа согласующих резисторов 28, группа ограничительных диодов 29, группа усилительных полевых транзисторов 30, управляемый резистор 31.

Каждый блок 20 содержит делитель 32 частоты и Я5 -триггер 33, Управля емьв резистор 31 содержит ключи 34 и масштабные резисторы 35.

Устройство работает следующим образом.

В соответствии с рассчитанными параметрами RC-узла 2 сеточной модели на вход блока 3 синхронизации поступает двоичный код параметра соответствующего RC-узла 2, Для занесения информации в делитель 32 частоты двоичный код параметра преобразуют в фазоимпульсный сигнал управления с помощью блока 3, которьгй формирует периодические импульсные последовательности на трех своих выходах.

С второго выхода блока 3 снимают импульсную последовательность Гд которую принимают за опорную.

0

5

На третьем выходе блока 3 формируется периодическая импульсная последовательность Fj , сдвинутая относительно опорной FO .

Импульсы F) несут информацию о значении параметра R С-уз; а 2 и поступают на информационный D -вход демультиплексора 4, на стробирующий С -вход которого с входа задания начального состояния устройства поступают импульсы Запись . На управляющие входы А - AN демультиплексора 4 поступают сигналы кода адреса с , выходов счетчика 5 адреса, который

5 служит для формирования кода адреса RC-узла 2 RC-сетки 1, параметры которого устанавливаются следующим образом. Сначала подается сигнал на вход запуска, который является вхо20 дом устройства. Далее с выхода регистра 17 памяти подается код началь-- ного адреса, соответствуюишй коду адерса RC-узла 2, параметр которого необходимо установить.

5 По сигналу Запись j сигналы с выходов демультиплексора 4 поступают на R -вход делителя 32 частоты, определяемого кодом адреса на управляющих А2 - AN входах демультиплексора

0 4. На С-вход делителя 32 частоты поступают импульсы f с первого выхода блока 3. Делитель 32 частоты представляет собой счетчик, работающий в фазоимпульсном режиме. Работа фазоимпульсного элемента памяти основана на запоминании фазы некоторой входной последовательности Г относительно опорной последователь5

ности FQ той же частоты. Если на С

вход делителя 32 частоты подавать импульсы частоты i , то на выходе имеется последовательность импуЛь- сов Ij. /К, сдвинутая относительно опорной на любое число импульсов час- тоты (к - разрядность делителя 32 частоты)..

Установка необходимого сдвига производится с помощью подачи на R, - вход делителя 32 частоты импульсов, сдвинутых относительно опорных им- . пульсов на величину, определяемую значением параметра R С-узла 2 R С- сетки 1 сеточной модели. В качестве таких импульсов и используется импульсная последовательность FJ , снимаемая с третьего выхода блок 3 Пи сигналу, который поступает по шине Запись j на С-вход демульти

плексора А. После Прекращения действия сигнала Запись на выходе делителя 32 частоты присутствует импульсная последовательность

тех пор, пока на его входе,имеется импульсная последовательность F . Импульсы Fj с выхода делителя 32

резистора 3 пpи 1eняeтcя два усилителя 22 и 23 и делитель 24 напряжения . Потенциалы с выводов управляем го резистора 31 через усилители 22 5 23, предназначенные для развязки, поступают на делитель 24 напряжения с которого снимается полуразность по данных напряжений и подается, в свою очередь, на выбранный управляющий

частоты поступают на установочный Rвход RS -триггера 33, а на 5 -вход

R5 -триггера 33 поступают импульсы 10 вход выбранного ключа 34. Из теории

FO , На выходе триггера 33 формиру- полевых транзисторов известно, что

20

ются импульсы управления i , которые поступают на катоды ограничительных диодов 29 и несут информацию о величине параметра R С-узла 2. 15

Из регистра 25 вьщается код номера одной из параллельных цепочек управляемого резистора 31. Регистр 25 хранит информацию о значении порядка управляемого резистора 31. Сигналы, снимаемые с выходов дешифратора 26, подаются на затворы усилительных полевых транзисторов 30, разрешая работу только одной из р езистив- ных цепочек. Соответствзпощий полевой транзистор 30 вырабатывает синхронный с сигналом {ц сигнал который задает проводимость резистивного элемента 31.

Среднаяя за период Т -р- вели- зо чина проводимости складывается из двух ее дискретных значений: G в момент, когда ключ 25 замкнут и О - когда ключ 25 разомкнут. На конденсаторе 21 пульсации напряжения, вызванные импульсной модуляцией проводимости, сглаживаются. В результате этого среднее значение проводимости за период определяется формулой:

стабилизация сопротивления канала или линеаризация возможна при подаче на затвор половины разности напряжеНИИ стока и истока. Если учесть, что вел.ичина сопротивления резисторов 35 каждой их цепочек резистора 3.1 одина кова, а следовательно, одинаковы и падения напряжения на них, то на-выходе делителя 24 напряжения линеаризации выделяется только полуразность напряжений между стоком и истоком ключа 34, так как равные падения напряжения на резисторах 35 компенси- 25 руются.

При отсутствии разрешающего сигна ла с входного дешифратора 26 на затвор соответствующего ключа 34 подается запирающий потенциал независимо от наличия импульса управления i. В случае наличия разрешающего сигнала ключ 25 управляется импульсом ц причем при его отпирающем значении на затвор ключа 25 поступает напряже ние линеаризации по цепи: транзистор 30 - сопротивление 28, Запирающее значение непосредственно подается через диод 29 на затвор ключа 34 вместо напряжения линеаризации.

35

G ifi G- ,

где Q - средняя за период проводимость соответствующая yj (i 1,2,

3,...: GK - величина постоянной про-,.-с

, 01 5 На управляющие входы АЕ - АК блока

водимости N -и цепочки резистора 31;

Сигнал Запись J поступает также на вход блока 7 памяти, и в соответствии с адресом узла, поступающего с выхода счетчика 5 адреса

У I --- - относительная длительность широтно-импульсного сигнала;

Т -f- - период квантования.

о

Кроме того, сглаживающий конденса- iтор 21 может быть использован для моделирования динамических свойств

7 производится занесение кода пара метра ц, поступающего с выхода пе вого регистра памяти 16 на информа ционные входы D 1 - 3) N в блок 7 . 50 Далее после изменения значения код адреса и устаноЬки на выходе регис ра I6 памяти необходимого значения кода параметра следующего I С-узла 2 R С-сетки 1 сеточной модели про

7 производится занесение кода параметра ц, поступающего с выхода пер вого регистра памяти 16 на информационные входы D 1 - 3) N в блок 7 . 50 Далее после изменения значения кода адреса и устаноЬки на выходе регист ра I6 памяти необходимого значения кода параметра следующего I С-узла 2 R С-сетки 1 сеточной модели прообъекта с распределенными параметрами при решении нестационарных задач. 55 изводится занесение информация по .Для стабилизации сопротивления откры- этому адресу в делитель 32 частоты того канала соответствующего ключа 34 гГри изменении потенциалов на выходах

соответствующего RС-узла 2 и блок 7 и т.д. по всем адресам (узлам).

2

260981.4

резистора 3 пpи 1eняeтcя два усилителя 22 и 23 и делитель 24 напряжения . Потенциалы с выводов управляемого резистора 31 через усилители 22 и 5 23, предназначенные для развязки, поступают на делитель 24 напряжения, с которого снимается полуразность поданных напряжений и подается, в свою очередь, на выбранный управляющий

0

5

о стабилизация сопротивления канала или линеаризация возможна при подаче на затвор половины разности напряже . НИИ стока и истока. Если учесть, что вел.ичина сопротивления резисторов 35 каждой их цепочек резистора 3.1 одинакова, а следовательно, одинаковы и падения напряжения на них, то на-выходе делителя 24 напряжения линеаризации выделяется только полуразность напряжений между стоком и истоком ключа 34, так как равные падения напряжения на резисторах 35 компенси- 5 руются.

При отсутствии разрешающего сигнала с входного дешифратора 26 на затвор соответствующего ключа 34 подается запирающий потенциал независимо от наличия импульса управления i. . В случае наличия разрешающего сигнала ключ 25 управляется импульсом ц , причем при его отпирающем значении на затвор ключа 25 поступает напряжение линеаризации по цепи: транзистор 30 - сопротивление 28, Запирающее значение непосредственно подается через диод 29 на затвор ключа 34 вместо напряжения линеаризации.

5

40

-с

Сигнал Запись J поступает также на вход блока 7 памяти, и в соответствии с адресом узла, поступающего с выхода счетчика 5 адреса.

7 производится занесение кода параметра ц, поступающего с выхода первого регистра памяти 16 на информационные входы D 1 - 3) N в блок 7 . Далее после изменения значения кода адреса и устаноЬки на выходе регистра I6 памяти необходимого значения кода параметра следующего I С-узла 2 R С-сетки 1 сеточной модели производится занесение информация по этому адресу в делитель 32 частоты

изводится занесение информация по этому адресу в делитель 32 частоты

соответствующего RС-узла 2 и блок 7 и т.д. по всем адресам (узлам).

Таким образом, значение параметров RC-узлов 2 RC-сетки 1 сеточной модели хранятся как в соответствующих делителях 32 частоты в виде фазового сдвига между импульсами опорной последовательности TO сами последовательности F

и импуль- , используемых для формирования импульсов управления i, , так и в соответствующих ячейках блока 7 памяти статического типа в виде эталонного значения.

В процессе решения задачи на сеточной модели контролируемые импульсы управления с выходов R5 -триггеров 33 подаются на информационные входы О - N мультиплексора 6, на управляющие входы Af-AN которого поступает начальный код адреса со счетчика 5 адреса. При этом на выходе мульти- плексора 6 присутствуют импульсы, 20 плексора 4, мультиплексора 6, блока длительность которых определяется ве- 7 и дешифратора 14 адреса устанавли- личиной фазового сдвига, хранимого в соответствующем делителе 32 частоты по этому адресу. По этому адресу

25

происходит обращение к памяти блока 7, в котором хранятся эталонные значения кода параметра.

По сигналу Считывание, который поступает на вход блока 7 и С-вход реверсивного счетчика 8 с предуста- 30 новкой производится перезапись хранимой по соответствующему адресу блока

7информации в реверсивный счетчик

8с предустановкой.

Контролируемый параметр i;(, с 35 выхода мультиплексора 6 поступает на первый вход схемы И 10, на второй вход которой подаются импульсы частоты ip с выхода блока 3. При этом на выходе схемы И 10 формируется пачка 40 импульсов частоты , количество которых равна i i . Эта пачка импульсов поступает на вычитающий вход 1 реверсивного счетчика 8.

вается код адреса следующего RC-узла 2 1 С-сетки 1 , а на его выходе появляется контролируемый импульс. Процесс контроля длительности этого импульса аналогичен описанному.

При появлении сигнала Сбой дальнейший контроль прекращается, а на блоке 15 индикации высвечивается адрес RC-узла 2 R С-сетки 1, в

делителе 32 частоты которого хранитI I

ся ошибочное значение параметра x, . После исправления оператором ошибки процесс автоматического контроля параметров RC-узлов 2 RС-сетки 1 возобновляется.

Таким образом, в предлагаемой сеточной модели происходит автоматический контроль параметров резистивных . элементов, что исключает необходимость периодического ручного контроля оператором параметров модели в процессе решения задач моделирования

на RC-сетке, в результате чего повы- Если значение кода параметра, за- 5 дается точность решения и эффективписанного в счетчик 8, соответствует числу импульсов, пришедших на вычитающий вход, то по окончании контролируемого импульса i ц состояние счетчика 8 должно быть нулевым, Тпв. 50 на всех его выходах, подключённых к входам схемы ИЛИ 9, Должен быть О. При этом на выходе схемы ИЛИ 9 присутствует О, который поступает на установочный R-вход триггера II. На 55 С-вход триггера 11 поступает контролируемый импульс t(, с выхода мультиплексора 6, по заднему фронту котоность использования сеточной модели. Формула изобретения

Сеточная модель, содержащая первый и второй ре гистры памяти, блок задания начальных условий, блок задания граничных условий, RC-сетку, состоящую из N RC-узлов, каждый из которых содержит управляемый резистор, сглаживающий конденсатор, два усилителя, делитель напряжения, регистр, входной дешифратор, первую

609816

рого триггер 11 должен быть изменить свое состояние на единичное и на его выходе появился бы сигнал Сбой. Но так как на R -вход триггера 11 по- 5 дан О, то он блокирует переключение триггера и он остается в нулевом состоянии. При этом с инвертирующего выхода триггера П 1 поступает на первый вход схемы И 13, на второй 10 вход которой подается контролируемый

импульс , с выхода мультиплексора 6 через элемент 12 задержки. Сигнал с выхода элемента И 13 при отсутствии сигнала Сбой поступает по оконча- НИИ импульса t на вход сложения +1 счетчика 5 адреса с предустановкой импульса, по заднему фронту которого в сч.етчик 5 адреса добавляется единица и на управляющих входах демультиплексора 4, мультиплексора 6, блока 7 и дешифратора 14 адреса устанавли-

вается код адреса следующего RC-узла 2 1 С-сетки 1 , а на его выходе появляется контролируемый импульс. Процесс контроля длительности этого импульса аналогичен описанному.

При появлении сигнала Сбой дальнейший контроль прекращается, а на блоке 15 индикации высвечивается адрес RC-узла 2 R С-сетки 1, в

делителе 32 частоты которого хранитI

ся ошибочное значение параметра x, . После исправления оператором ошибки процесс автоматического контроля параметров RC-узлов 2 RС-сетки 1 возобновляется.

Таким образом, в предлагаемой сеточной модели происходит автоматический контроль параметров резистивных элементов, что исключает необходимость периодического ручного контроля оператором параметров модели в процессе решения задач моделирования

ность использования сеточной модели. Формула изобретения

Сеточная модель, содержащая первый и второй ре гистры памяти, блок задания начальных условий, блок задания граничных условий, RC-сетку, состоящую из N RC-узлов, каждый из которых содержит управляемый резистор, сглаживающий конденсатор, два усилителя, делитель напряжения, регистр, входной дешифратор, первую

7

и вторую группы согласующих ре исто ров, группу ограничительных диодов и группу усилительных полевых транзисторов, затворы которых соединены с группой выходов входного дешифратора и с первыми выводами соответствующих согласующих резисторов первой группы, вторые выводы которых подключены к истокам соответствующих усилительных полевых транзисторов группы и к первым выводам соответствующих согласующих резисторов второй группы, вторые выводы которых соединены с анодами соответствующих ограничительных диодов группы и с группой входов задания проводимости управляемого резистора, первый вывод которого подключен через первый усилитель к первому крайнему выводу делителя напряжения, второй крайний вьгоод которого соединен с выходом второго усилителя, вход которого подключен к второму выводу управляемого резистора и к первому выводу сглаживающего конденсатора, второй вывод которого соединен с шиной нулевого потенциала, средний вывод делителя напряжения подключен к стокам усилительных полевых транзисторов группы, группа выходов регистра соединена с группой входов входного дешифратора, N блоков формирования длительности импульса, каждьм из которых состоит из делителя .частоты и RS -триггера, первый установочный .вход которого соединен с выходом делителя частоты, выход каждого RS - триггера подключен к катодам ограничительных диодов группы соответствующего I С-узла RC-сетки, выход блока задания начальных условий соединен с первым выводом управляемого резистора первого RC-узла, второй вьгоод управляемого резистора каждого i -го (где i 2,N) RC-узла подключен к первому вьгооду управляемого резистора (i +1) -го UC-узла второй вывод управляемого резистора ,N-ro RG-узла соединен с выходом блока задания граничных условий, отличающаяся тем, что, с целью повьшения точности, в него введены блок синхронизации, счетчик адреса, демультиплексор, мультиплексор, два элемента И, блок памяти.

60981. 8

реверсивный счетчик, элемент задержки, элемент ИЛИ, дешифратор, блок индикации, и триггер, прямой выход которого является выходом сбоя сеточ- 5 Hofi модели, вход установки начального состояния которой соединен с входом записи блока памяти и со стробирующим входом демультиплексора, каждьщ из N выходов которого подключен к входу ус- 10 тановки О делителя частоты соответствующего блока формирования длительности импульса, группа выходов первого регистра памяти соединена с группой информационных входов блока па- 15 мяти и с группой входов задания временного распределения блока синхронизации, первый выход которого подключен к информационным входам делителей частоты и к первому входу первого

20 элемента И, выход которого соединен с вычитающим входом реверсивного счетчика, группа выходов которого подключена к группе входов элемента ИЛИ, выход которого соединен с входом уста5 новки в О триггера, инверсный выход которого подключен к первому входу второго элемента И, выход которого соединен с суммирующим входом счетчика адреса, группа выходов которого

0 подключена к группе адресных входов мультиплексора, к группе адресных входов блока памяти и к группе входов дешифратора, группа выходов которого соединена с группой входов блока

5 индикации, второй выход блока синхронизации подключен к вторым установочным входам R6 -триггеров, выходы каждого из которых соединены с соответствующим информационным входом

0 мультиплексора, выход которого подключен к второму входу первого элемента И, счетному входу триггера и входу элемента задержки, выход которого соединен с вторым входом второ5 го элемента И, вход запуска сеточной модели подключен к входам записи реверсивного счетчика, счетчика адреса и к входу чтения блока памяти, группа выходов которого соединена с

0 группой входов реверсивного счетчика, группа выходов рторого регистра памяти подключена к группе информационных входов счетчика адреса, третий выход блока синхронизации соединен с информационным входом демультиплексора.

га го

го

| название | год | авторы | номер документа |

|---|---|---|---|

| Сеточная модель | 1987 |

|

SU1483469A1 |

| Устройство для решения краевых задач | 1983 |

|

SU1149286A1 |

| Устройство для решения обратных задач теории поля | 1984 |

|

SU1164748A1 |

| СИСТЕМА ОХРАННОЙ СИГНАЛИЗАЦИИ | 1993 |

|

RU2092903C1 |

| Устройство для вывода информации | 1983 |

|

SU1124278A1 |

| Устройство для контроля и диагностики радиоэлектронной аппаратуры | 1986 |

|

SU1432463A1 |

| Устройство для решения задач оптимального управления | 1985 |

|

SU1327135A1 |

| Устройство для индикации | 1990 |

|

SU1795513A1 |

| Цифровой измеритель параметров комплексного сопротивления | 1989 |

|

SU1732292A1 |

| Устройство для измерения скорости перемещения | 1989 |

|

SU1732281A1 |

Изобретение относится к гибридной вычислительной технике и может быть использовано при построении автоматизированных сеточных интеграторов для моделирования уравнений математической физики и для решения задач управления объектами с распределенными параметрами. Целью изобретения является повьпнение точности. Устройство содержит RC-сетку, состоящую из RC-узлов, блок синхрониз.а- ции, демультиплексор, счетчик адреса, мультиплексор, блок памяти, реверсивный счетчик, элемент ИЛИ, эле- . менты И, элемент задержки, дешифратор, блок индикации, регистры памяти, блоки задания начальных и граничных условий. Устройство позволяет производить автоматический контроль параметров резистивных элементов, что исключает необходимость периодического ручного контроля параметров модели в процессе решения задач и тем самым повысить точность решения задач математической физики. 2 ил. i сл с

Редактор Л. Пчелинская

Составитель В. Рыбин Техред М.Ходанич

Заказ 5234/51Тираж 671

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская-наб., д. 4/5

Дроизводственно-пслиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректоре. Шекмар

Подписное

| Узловой элемент сеточной модели | 1979 |

|

SU781842A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Андриевский В.М | |||

| Узловой элемент дискретно-аналогового сеточного процессора | |||

| -Вкн.: Локальные АСУ и устройства вычислительной техники, вьт | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| - Киев: Наукова думка, 1981, с 47-51. | |||

Авторы

Даты

1986-09-30—Публикация

1984-07-06—Подача