1

Изобретение относится к вычислительной технике и может быть использовано при построении автоматизированных сеточных интеграторов для моделирования уравнений математической физики и для решения задач управления объектами с распределенными параметрами.

Известен узловой элемент сеточной модели, содержащий блок проводимости, входы которого соединены с выходами блока управления, первый вход которого подключен к выходу программного блока, блок аналоговой памяти, ключи блока слежения и блок развязки 1.

Недостатком устройства является необходимость применения большого количества цепочек, состоящих из прецизионного резистора и ключа, для получения малой дискретности величины проводимости в требуемом диапазоне. Это щэиводит к усложнению схемы управления ключами, возрастанию габаритов и стоимости узлового элемента что 1 имеет решающее значение при построении многомерных сеточных моделей с большим числом узлов.

Для поддержания постоянной разности потенциалов мелоду стоком и затвором МОП-ключа в целях исключения зависимости сопротивления открнятого канала полевого транзистора от потенциала узла требуется сложная схема управления, включающая четыре взаимосвязанных блока.

Зависимость сопротивления открытого канала транзистора от величины проходящего тока отрицательно сказывается на точности.

Кроме того, аналоговая память сложна в технической реализации и не обеспечивает высокой стабильности хранимого параметра, что снижает точность узлового элемента.

Наиболее близким техническим решением к изобретению является резистивный узел сеточной модели, содержаЕЦ-ш блок проводимости, состояшдй из параллельных цепочек с последовательно включенными резисторами и ключом на полевом транзисторе с управляющим р-П-переходом меж,цу ними, входы которого соединены с выходами блока управления, состоящего из трех идентичных каналов, каждый собран на полевом транзисторё, исток и затвор которого соединены резистором обрат203662

ной связи, через выходной резистор соединен с анодом ограничительного диода, катод которого является третьим входом блока управления, 5 анод - его выходом, сток полевого

транзистора - вторым, а затвор - первым входами блока управления, который подключен к выходу программного блока, блок формирования относительfO ной длительности ньшульса, состоящий из формирующего триггера, первого генератора опорной частоты и второго генератора опорной частоты с управляемым фазовым сдвигом, выход которого

15 подключен к первому входу формирующего триггера, второй вход которого непосредственно подключен к выходу первого генератора опорной частоты, сглаживающую емкость и блок линеари0 зации, включающий два усилителя,

выходы которых соединены с крайними выводами делителя напряжения, средний вывод которого подключен к второму входу блока управления, третий

5 вход которого соединен с выходом бло ка формирования относительной длительности импульса, первый и второй выходы блока проводимости подключены соответственно к входам-первого и

0 второго усилителей блока линеаризации, одна обкладка сглаживающей емкости соединена с первым выходом блока проводимости, а.другая - с шиной нулевого потенциала 2|.

5 Недостатком известного устройства является то, что сопротивление канала полевого транзистора сутцественно зависит от тe fflepaтypы, что снижает точность узлового элемента. Экспериментально установлено, что изменение температуры приводит к изменению величины сопротивления цепей блока про водимости на величину до 1% на каж дые .

Цель изобретения - повышение точности резистивного узла сеточной модели .

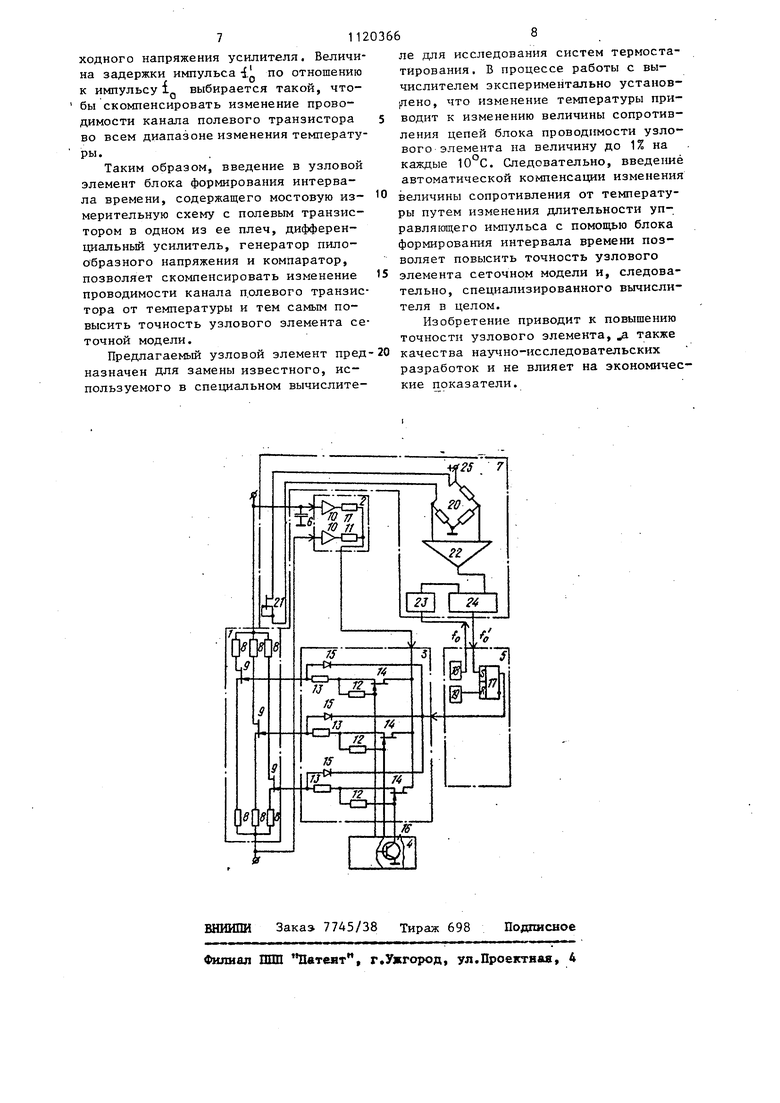

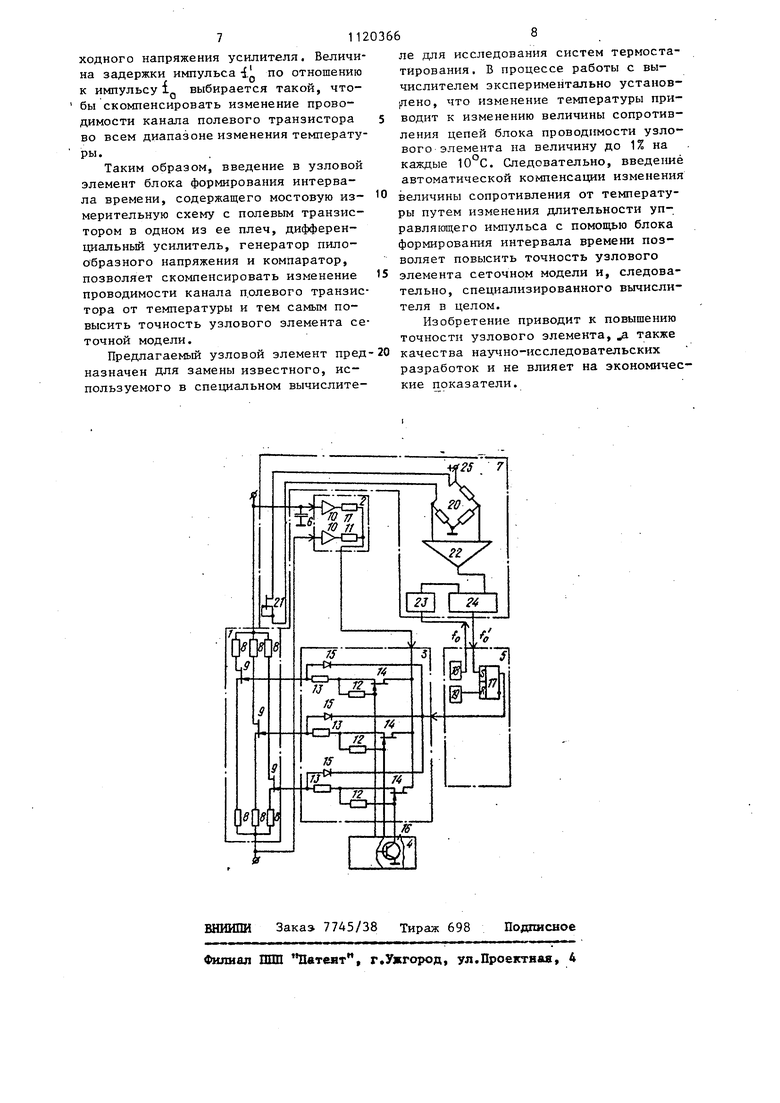

Поставленная цель достигается тем, что в узел, содержащий блок уп0 равления, блок проводимости, первый и второй выходы которого являются соответственно первым и вторым выводами устройства и подключены соответственно к первому и втором вхо5 дам блока линеаризации, выход которого соединен с первым информационным входом блока управления, первый, второй и третий управляющие входы которого подключены соответственно к первому, второму и третьему выходам программного блока, первый выход блока формирования относительной длительности импульса соединен с вторым информационным входом блока управления, первый, второй и третий выходы которого подключены соответс венно к первому, второму и третьему входам блока проводимости, первый выход которого соединен с первым вы водом сглаживающего конденсатора, второй вывод которого подключен к шине нулевого потенциала, введен бл формирования временного интервала, состоящий из полевого транзистора, трех эталонных резисторов, источник постоянного напряжения, дифференциального усилителя, генератора пилообразного напряжения и компаратора, выход которого подключен к вход блока формирования относительной длительности, второй выход которого соединен с входом генератора пилооб разного напряжения, выход которого подключен к первому входу компарато ра, второй вход которого соединен с выходом дифференциального усилителя первый вход которого подключен к пе вому выводу первого эталонного резистора и к затвору и истоку полево го транзистора, сток которого соеди нен с выходом источника постоянного напряжения и с первым выводом второ го эталонного резистора, второй вывод которого подключен к второму входу дифференциального усилителя и первому выводу третьего эталонного резистора, второй вывод которого соединен с вторым выводом первого эталонного резистора и шиной нулевого потенциала. Кроме того, блок формирования от носительной длительности импульса содержит генератор запускающих импульсов, триггер и генератор опорной частоты, выход которого додключен к первому установочному входу , триггера, выход которого является первым выходом блока, второй выход .которого соединен с выходом генератора запускающих импульсов, вход блока подключен к второму установоч ному входу триггеоа. На чертеже изображена функциональная схема предлагаемого узла. Устройство содержит блок 1 проводимости, блок 2 линеаризации, бло 3 управления, програ 1мный блок 4, блок 5 формирования относительной длительности импульса, сглаживающий конденсатор 6, блок 7 формирования временного интервала. Блок 1 проводимости содержит резисторы 8 и ключи 9. Блок 2 линеаризации содержит усилители 10 и резисторы 11. Блок 3 управления содержит резисторы 12 и 13, полевые транзисторы 14 и диоды 15. Программный блок 4 содержит транзисторы 16. Блок 5 формирования относительной длительности импульса содержит три1- гер 17, генератор 18 запускающих импульсов и генератор 19 опорной часто- ты с управляемым -фазовым сдвигом. Блок 7 формирова1П1я временного интервала содержит эталонные резисторы 20, полевой транзистор 21, дифференциальный усилитель 22, генератор 23 пгшообразного напряжения, компаратор 24 и источник 25 постоянного напряжения. Устройство работает следующим об- разом. В программном блоке 4 в цифровом коде записывается номер N одной из параллельных цепочек блока 1 проводимости. С его выхода на блок 3 уп,равления подается сигнал, разрешающий работу только одного выбранного ключа 9. На другой вход блока 3 управления с блока 5 формирования относительной длительности импульса поступает широтно-импульсный управляющий сигнал. Блок 3 управления вырабатывает сигнал, синхронный с сигналом Cf , которьй управляет ключом 9 на полевом транзисторе. Средняя за период величина проводимости складывается из двух ее дискретных значений: ; в момент, когда ключ 9 замкнут, и О, когда ключ 9 разош-снут. На конденсаторе 6 пульсации напряжения, вызванные импульсной модуляцией проводимости, сглаживаются, в результате чего среднее значение проводимости за rte- риод определяется формулой , где Q - средняя за период проводимость, -соответствующая (,2,3...); ч ц - величина постоянной проводимости, соответствующая К -му разряду. Средняя за период проводимость оказывается пропорциональной относительной длительности импульса имротнo-IIlvfflyльcнoгo сигнала Q if J где tц длительность импульсаj 1 - пе риод квантования, и величине постоян ной проводимости Q . Кроме TorOj сглаживающий конденса тор б может быть использован для моделирования динамических свойств объ екта с распределенными параметраьш при решении нестационарных задач. ;Дпя стабилизаидм сопротивления откры того канала полевого транзистора при ;изменении входного и выходного потен циалов блока 1 проводимости применяется блок 2 линеаризации. Потенциалы входа и выхода блока 1 проводимос ти через усилители 10, служащие для развязки, поступают на резнстивньй делитель напряжения на резисторах 11 с которого снимается полуразность ноданньк напряжений. Из теории полевых, транзисторов известно, что стабилизация сопротивления канала или ли -1еаризацки возможна при подаче на затвор половины разности напряжений стока и истока. Если учесть, что величина сопротивления резисторов 8 калсдой из цепочек блока 1 проводимости одинакова, а следовательно, одинаковы и падения напряжений на них, т на выходе делителя блока 2 линеаризации выделяется только полуразность напряжений мелсду стокоми истоком транзистора, так как ра.вные падения напрял ения па резисторах 8 ко1-шенсируются. Напряжение линеаризации с помоц(ью блока 3 управления подается на затвор выбран юго транзистора в моменты отпирания ключа. Блок управления работает следукгл щим образом. При сигнале Логическая 1 с выхода соответствующей схемы программного блока 4 закрывается выходной транзистор 16 логики. Исток и затвор транзистора 14 оказываются связаннЕями через резистор 12, и транзистор 14 открывается, при этом на истоке его присутствует напрялсение линеаризации. При подаче запирающего ишротноимпульсного управляющего сигнала с блока 5 формирования относительной длительности иьтульса диод 15 открывается и на затвор ключа 9 подается низкий запирающий потенциал. При отпирающем широтно-импульсном сигнале диод 15 закрыт и на затвор ключа 9 через транзистор 14 и резистор 13 подается напряжение линеариза1щи. При сигнале Логический О на выходе блока 4 на затвор транзистора 14 подается нулевор потенциал. Транзистор 14 и резистор 12 представляют собой генератор тока малой величины, поскольку резистор 12 выбирается высокоомным, включенный между источником напряжения линеариз.ации и шиной нулевого потенциала. Омическое сопротивление канала транзистора 14 практически равно дифферентдаальному сопротивлению стабилизатора тока. Поэтому напряжение линеаризации оказывается практически отключенным от затвора ключа 9. На резисторе 12 выделяется напряжение, примерно равное напряжению отсечки транзистора 14, которое закрывает ключ 9, Блок 7 формирования временного интервала для создания задерлСки на некоторое время поступления опорного импульса на формирующей триггер 17, Время задержки зависит от изменения величины сопротивления канала полевого транзистора 21, Поскольку транзисторы 9 находятся в тех же условиях, что и транзистор 21, изменение сопротивления канала транзисторов 9 связано функциональной- зависимостьро с временем задержки опорного импу.льса IQ . Задержка опорного импульса вызывает уменьшение длительности широтно-импульсного сигнала управления, что в свою очередь приводит к уменьшению средней за период проводимости блока 1 . Напряжение небаланса моста, состояп его из полевого транзистора и эталонных резисторов 20, вызванное изменением проводимости канала полевого транзистора 21 от температуры, усиливается усилителем 22 и поступает на один из входов компаратора 24. На второй вход поступает иьшульс пилообразного напряжения с генератора 23 напряжения пилообразной формы, запускаемого импульсом частоты генератора 18. В момент сравнбгшя усиленного напряжения небаланса и напряжеНИ.Я пилообразной формы на выходе схемы сравнения появляется сигнал . , задержка которого относительно импульсаопределяется уровнем выходного напряжения усилителя. Величина задержки импульса -f по отношению к импульсу выбирается такой, чтобы скомпенсировать изменение проводимости канала полевого транзистора во всем диапазоне изменения температуры .

Таким образом, введение в узловой элемент блока формирования интервала времени, содержащего мостовую из мерительную схему с полевым транзистором в одном из ее плеч, дифференциальный усилитель, генератор пилообразного напряжения и компаратор, позволяет скомпенсировать изменение проводимости канала долевого транзистора от температуры и тем самым повысить точность узлового элемента сеточной модели. Предлагаемый узловой элемент пред-20 назначен для замены известного, используемого в специальном вычислителе для исследования систем термостатирования. В процессе работы с вычислителем экспериментально установртено, что изменение температуры приводит к изменению величины сопротивления цепей блока проводимости узлового элемента на величину до 1% на каждые 10 С. Следовательно, введение автоматической компенсации изменения величины сопротивления от температуры путем изменения длительности управляющего импульса с помощью блока формирования интервала времени позволяет повысить точность узлового элемента сеточном модели и, следовательно, специализированного вычислителя в целом.

Изобретение приводит к повышению точности узлового элемента, также качества нау шо-исследовательских разработок и не влияет на экономические показатели.

| название | год | авторы | номер документа |

|---|---|---|---|

| Узловой элемент сеточной модели | 1979 |

|

SU781842A1 |

| Сеточная модель | 1984 |

|

SU1260981A1 |

| Сеточная модель | 1987 |

|

SU1483469A1 |

| Устройство для решения нелинейных задач теории поля | 1981 |

|

SU983722A1 |

| Устройство для моделирования объектов с распределительными параметрами | 1973 |

|

SU466518A1 |

| Устройство для моделирования распределенных объектов управления | 1974 |

|

SU491960A1 |

| Устройство для моделирования нелинейных процессов | 1973 |

|

SU479126A1 |

| Способ преобразования перемещения в длительность импульсов и устройство для его осуществления (его варианты) | 1984 |

|

SU1227939A1 |

| Устройство для моделированияСТАТичЕСКОгО МАгНиТНОгО пОля | 1979 |

|

SU805356A1 |

| Устройство для измерения пороговых напряжений моп-транзисторов | 1978 |

|

SU697937A1 |

1. РЕЗИСТИВНЫЙ УЗЕЛ СЕТОЧНОЙ МОДЕЛИ, содержащий блок управления, блок проводимости, первый и второй выходы которого являются соответственно первым и вторым выводами устройства и подключены соответственно к первому и второму входам блока линеаризации, выход которого соединен с первым информационным входом блока управления, первый, второй и третий управляющие входы которого подключены соответственно к первому, второьгу и третьему выходам программного блока, первый выход блока формирования относительной длительности импульса сое динен с вторым информационным входом блока управления, первый, второй и третий выходы которого подключены соответственно к первому, второму и третьему входам блока проводимости, первый выход которого соединен с первым выводом сглаживающего конденсатора, второй вывод которого подключен к шине нулевого потенциала, отличающийся тем, что, с целью повышения точности, в него введен блок формирования временного интерва- ла, состоящий из полевого транзистора, трех эталонных резисторов, источника постоянного напряжения, дифференциального усилителя, генератора пилообразного напряжения и компара-. тора, выход которого подключен к входу блока фop шpoвaния относительной длительности импульсов, второй выход которого соединен с входом генератора пилообразного напряжения, выход которого подключен к первому входу компаратора, второй вход котЬрого соединен с выходом дифференциального усилителя, первый вход которого подключен к первому выводу первого эталонного резистора и к затвору и истоку полевого транзистора, . сток которого соединен с выходом источника постоянного напряжения и первым выводом второго эталонного резистора, второй вывод которого под- ключен к второму входу дифференциального усилителя и первому выводу. третьего эталонного резистора, втою о рой вывод которого соединен с вторым выводом первого эталонного резистора и щиной нулевого потенциала. со 2. Узел ПОП.1, отличаюо щийся тем, что в нем блок фор,миаь рования относительной длительности импульса содержит генератор запускающих импульсов, триггер и генератор опорной частоты, выход которого подключен к первому установочному входу триггера, выход которого является первым выходом блока, второй выход которого соединен с вьосодом генератора запускающих импульсов, вход блока подключен к второму установочному входу триггера.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Кодоуправляемый элемент сеточной модели | 1975 |

|

SU547790A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Узловой элемент сеточной модели | 1979 |

|

SU781842A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-23—Публикация

1983-06-09—Подача