(,54) ЭЛЕКТРОННЫЙ ИМПУЛЬСНЫЙ КЛЮЧ

| название | год | авторы | номер документа |

|---|---|---|---|

| Транзисторный инвертор | 1991 |

|

SU1815775A1 |

| Транзисторный инвертор | 1988 |

|

SU1818673A1 |

| Источник вторичного электропитания для сети постоянного напряжения | 1990 |

|

SU1786476A1 |

| Ключ | 1985 |

|

SU1325682A1 |

| Транзисторный ключ | 1991 |

|

SU1780179A1 |

| Двухтактный ключ переменного напряжения | 1987 |

|

SU1448405A1 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ С ЗАЩИТОЙ ОТ ПЕРЕГРУЗКИ | 2002 |

|

RU2231213C2 |

| УСТРОЙСТВО ИМПУЛЬСНО-ФАЗОВОГО УПРАВЛЕНИЯ | 1999 |

|

RU2160957C2 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ | 2005 |

|

RU2287219C1 |

| СПОСОБ И УСТРОЙСТВО ЗАЩИТЫ МИКРОПРОЦЕССОРНЫХ СИСТЕМ ЖЕЛЕЗНОДОРОЖНОЙ АВТОМАТИКИ ОТ АППАРАТНЫХ И ПРОГРАММНЫХ НАРУШЕНИЙ В РАБОТЕ И УСТРОЙСТВО СРАВНЕНИЯ ПАРАФАЗНЫХ СИГНАЛОВ С ЗАЩИТОЙ ОТ ОПАСНЫХ ОТКАЗОВ | 2009 |

|

RU2385521C1 |

изобретение относится к импульсной и может быть использовано в мк кроэлсктронике при синтезе устройств эычислительной техники.

Известен электронный импульсный ключ, выполненный на транзисторах и туннельных диодах 1 .

Недостатком известного технического решения является низкая надежность.

Наиболее близким к предлагаемому по своей технической сущности является электронный импульсный ключ, содержащий триггер, схемы блокировки триггера и ключа 2 .

Недостатком известного ключа является ограниченные функциональные возможности, заключающиеся в отсутствии запоминания парафазного сигнала управления при изменении его в процессе коммутации.

Цель изобретения - расширение функциональных возможностей электронного импульсного ключа путем запоминания парафазного сигнала при изменении его в процессе комг утации. .

Поставленная цель достигается тем, что в электронный импульсный ключ, содержащий первый и второй транзисторы, эмиттеры которых объединены

между собой, а коллекторы подключены к первым эмиттерам соответственно третьего и четвертого транзисторов и через первый и второй резисторы к

5 шине питания, базы первого и второго транзисторов соединены с коллекторами соответственно четвертого и третьего транзисторов, базы третьего и четвертого транзисторов- соединены

10 с первыми выводами соответственно третьего и четвертого резисторов, вторые выводы которых объединены между собой, вторые эмиттеры третьего и четвертого транзисторов подключены

tS к коллекторам соответственно пятого и шестого транзисторов, базы которых подключены к первым выводам соответственно пятого и шестого резисторов, шину коммутации, первую и вторую шины управления, в него введены два транзистора и два резистора, причем коллектор седьмого транзистора подключен к вторым выводам третьего и четвертого резисторов, и через седьмой резистор к шине питания, эмиттер седьмого транзисторасоединен с общей шиной, а база - с коллектором восьмого трайзистора, эмиттер которого соединен с шиной коммутации, а база

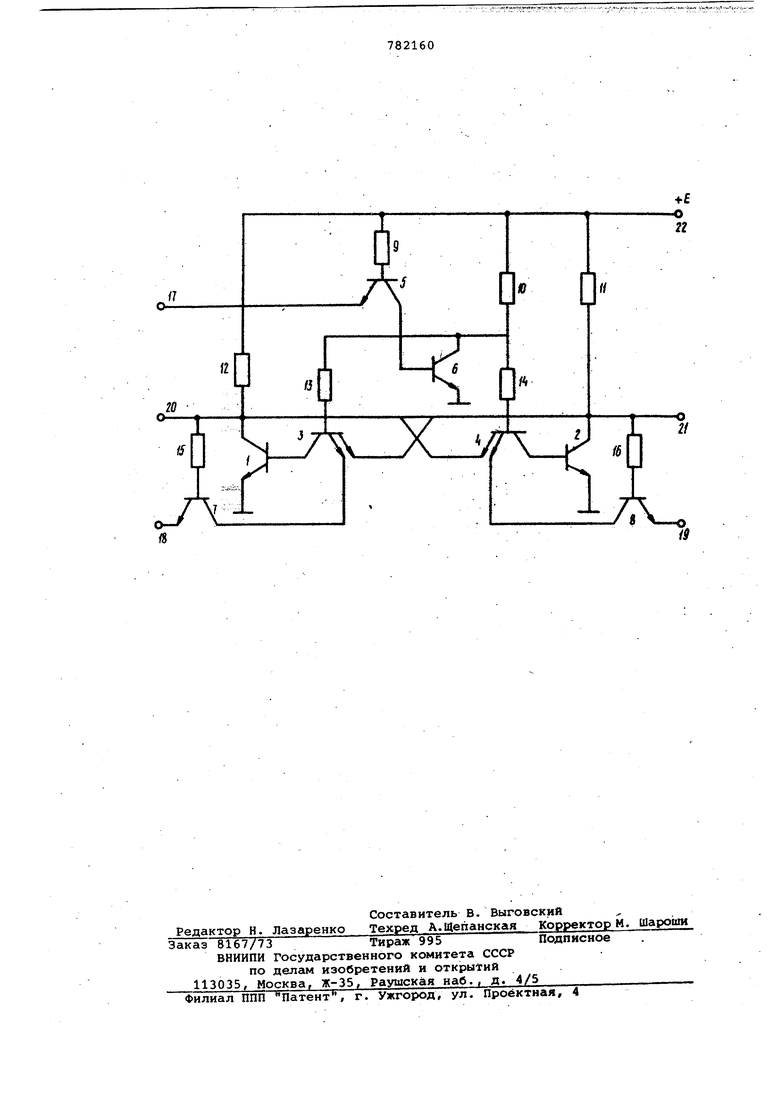

30 через восьмой резисторь - с шиной питания, эмиттеры пятого и шестого транзисторов соелинены соответственно с первой и второй шиной управлени вторые выводы пятого и шестого резис торов подключены к коллекторам соответственно второго и первого транзис торов, эмиттеры которых подключены к общей шине. На чертеже представлена принципиальная элЁктрическая схема электрюнного импульсного ключа. Электронный импульсный ключ содер жит транзисторы 1-8, резисторы 9-16, шину 17 коммутации, парафазные шины 18-19 управления, выходные шины 20-2 шину 22 питания. Электронный импульсный ключ работает следующим образом. В исходном состоянии на шине 17 . коммутации имеется уровень логическо единицы (высокий уровень напряжения) ток в цепи база-коллектор транзистора 5 открывает транзистор 6, который шунтирует переходы б.аза-эмиттер тран зисторов 3 и 4, в результате чего эти транзисторы заперты и, следовательно, заперты также транзисторы 1 и 2. На выходных шинах 20 и 21 присутствует уровень логической единицы Предположим, что на шине 18 управления уровень логической единицы, а на шине 19 управления - уровень ло гического нуля. Подача на шину 17 коммутации уров ня логического нуля приводит к откры ванию транзистора 5 и запиранию тран зистора б, т.е. базы транзисторов 3 и 4 подключаются к шине питания. При этом на обоиА эмиттерах транзистора имеется уровень логической единицы, транзистор 3 током перейода базаколлектор открывает транзистор 1,Сигйал логического нуля поступает на выходную шину 20. На обоих эмитте рах транзистора 4 присутствует уровень логического нуля, транзистор 4 открыт, т анзистор 2 закрыт за счет шунтирования его базо-эмиттерного перехода открытым транзистором 4. Изменение сигнала управления на шинах 18 и 19 управления во время действия импульса на шине 17 коммутации не оказывает-влияния на выходные шины 20 и 21, так как появление уровня логического нуля на шине 18 управления не изменяет состояние транзисторов 3 и 1, вследствие того, что тран зистор 7 закрыт уровнем логического нуля на его базе, а появление уровня логической единицы на шине 19 управления не изменяет состояния транзисторов 4 и 2, вследствие того, что транзистор 4 открыт уровнем логического нуля с коллектора транзис;- , тора 1 и, следовательно, транзистор 2 остается закрыты; и При появлении на шине 17 коммутации уровня логической единицы, схема возвращается в исходное состояние . Формула изобретения Электронный импульсный ключ, содержащий первый и второй транзисторы, эмиттеры которых объединены между собой, а коллекторы подключены к первым эмиттерам соответственно третьего и четвертого транзисторов и через первый и второй резисторы к шине питания, базы первого и второго транзисторов соединены с коллекторами соотБетственно четвертого и третьего транзисторов, базы третьего и четвертого транзисторой соединены с первыми выводами соответственно третьего и четвертого р езисторов, вторые выводы которых объединены между собой, вторые эмиттеры третьего и четвертого транзисторов подключены к коллектораил соответственно пятого и шестого транзисторов, базы которых подключены . к первым выводс1М соответственно пятого и шестого резисторов, шину коммутации, первую и вторую шины управления, отличаю щийс я тем, что, с целью расшир ения функциональных возможностей, путем запоминания парафазного сигнала при изменении его в процессе коммутации в него введены два транзистора и два резистора, причем коллектор седьмого транзистора подключен к, вторым .выводам третьего и четвертого резисторов, и через седьмой резистор к шине питания, эмиттер седьмого транзистора соединен с общей шиной, а база - с коллектором восьмого транзистора, эмиттер которого соединен с шиной коммутации, а база через восьмой резистор - с шиной питания, эмиттеры пятого и шестого транзисторов соединены соответственно с первой и второй шиной управления, вторые выводы пятого и шестого резисторов подключены к коллекторам соответственно второго и первого транзисторов, эмиттеры которых подключены к общей шине. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 371686, кл. Н 03 К 17/58, 1971. 2.Иагурин И. И. Транзисторнотранзисторные логические схемы. М., Сов. радио, 1974, -с. 128, рис. 4, 7 (прототип).

Авторы

Даты

1980-11-23—Публикация

1976-01-29—Подача