1

Изобретение относится к области вычислительной техники и может быть использовано в аналоговых вычислительных машинах и устройствах, где требуется определение частного от деления двух напряжений.

Известны устройства для деления двух аналоговых сигналов, в которых частное от деления входных сигналов определяется временем интегрирования напряжения знаменателя, до величины, соответствующей напряжению числителя .0-1 . Эти устройства содержат интеграторы, блоки сравнения, разрядные ключи, блоки запоминания (пиковые детекторы).

Такие устройства деления отличаются высокой точностью, малыми габаритами, высоким быстродействием, однако применение их ограничено тем, что эти устройства одноквадратного деления.

Наиболее близким техническим решением к изобретению является устройство, содержащее два интегрирующих усилителя с ключами в цепи обратной связи, нуль-орган, ключ, пиковый детектор и источник эталонного напряже нйя 2 .

Ука;занное устройство отличается высоким быстродействием и малыми габаритами, в нем величина отношения определяется временем интегрирования первым интегратором напряжения знаменателя до величины напряжения числителя. Сравнение выходного напряжения и напряжения числителя осуществляется нуль-органом. Второй интегратор

to в это время интегрирует напряжение эталонного источника, являющегося сомножителем. При срабатывании схемы сравнения прекращается процесс интегрирования в обоих интеграторах, и

15 напряжение на выходе пикового детектора, вход которого подклк1чен к выходу второго интегратора (при условии равенства постоянных йремени интегрирования) , равно отношению напряжения 20 числителя и знаменателя, умноженному на величину .напряжения эталонного сомножитедя,

Основным недостатком устройства 25 является маленький диапазон изменения входных сигналов, что вызывает невозможность осуществленияделения в четырех квадрантах.

Цель изобретения - расширение диапазона изменения входных сигналов

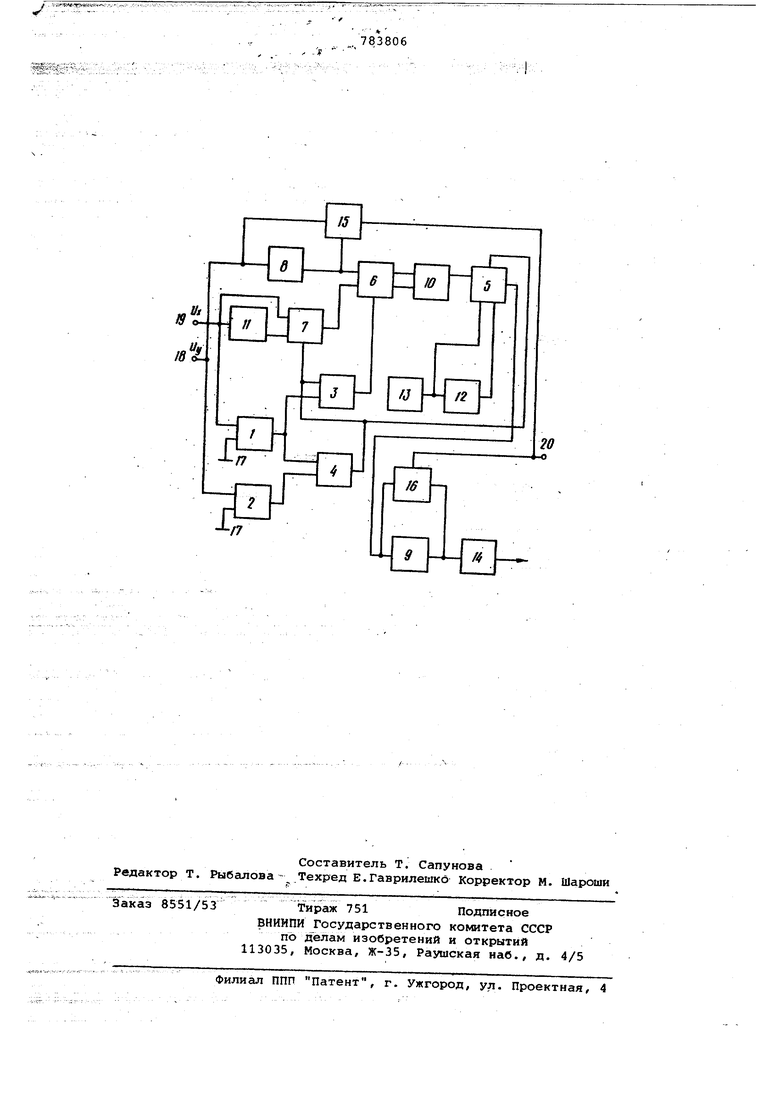

783806 при сохранении точности и быстродейст вия. Цель достигается тем, что в делительное устройство, содержащее первый интегрирующий усилитель с разрядным ключом в цег1и обратной связи, вход первого интегрирующего усилителя является входом устройства; первый нуль Ърган, первый вход которого, является вторым входом устройства, а второй вход подключен к шине нулевого потенциала, источник эталонного напряжения, второй интегрирующий усилитель с разрядньлм ключом в цепи обратной сЙяЗиГ пиковый Детектор и первый ключ первый информационный вход которого .подключен к выходу источника эталонного напряжения, а выход - к входу второго интегрирующего усилителя, выход которого подключен к входу пикового детектора, выход которого является выходом устройства, введены второй нуль-орган, первый вход которого является первым входом устройства, а второй ;вхбд подключен к шине нулевого потенциала, первый инвертирующий усилитель , вход которого подключен к в второму входу устройства и второй инвертирукйций усилитель, вход которого 11ОДКЛ1бчён -к выходу, источника эталонного напряжения, а выход подключен, к второму информационному входу первого ключа, второй и третий двухпозиционные ключи, первый и второй элементы Исключающее ИЛИ и блок сравне.ния. Выход первого интегрируклдего усилителя подключен к первому йнформационно. му входу второго двухпозиционного клю ча вьйходщ которого подключены к входам блЬка сравнения, выход которого подключен к первому управляющему вхо ду первого ключа. Первый информационный вход третьего двухпозиционного ключа подключен к второму входу устройсгва, а втйрой информационный вход TfJeTbero двухпоэиционного ключа - к выходу первого инвертирующего усилитеЛя. Управляющий вход третьего ключ подсоединен к первому входу первого элемента Исключающее ИЛИ, выход которого подключен к управлякяцему входу второго двухпозиционного ключа. Выход третьего двухпозиционного ключа подключен к второму информационного вхо ду второго двухпоэиционного ключа. Вы хоД первого нуль-органа подключен к BTQiJOMy входу первого элемен- -а Исклю ИЛИ и к первому входу второго элемента Исключаняцее ИЛИ, выход кото рого подключен к управляющему входу третьего, двухпоэиционного ключа и. к второму управляющему входу первого ключа. Выход второго нуль-органа под ключен к второму входу второго элеме та Искгаочающее ИЛИ. Управляющие вход разрядных ключей подключены к устано вочному входу устройства. Блок-схема делительного устройств представлена на чертеже. Делительное устройство содержит первый нуль-орган 1, второй нуль-орган 2, первый элемент Исключающее ИЛИ 3, второй элемент Исключающе.е ИЛИ 4, первый ключ 5, второй двухпоэиционный ключ б, третий двухпозиционный ключ 7, первый интегрирующий усилитель 8, второй интегрирующий усилитель 9, блок 10 сравнения, первый инвертирующий усилитель 11, второй«инвертирующий усилитель 12,источник 13 эталонного напряжения, пиковый детектор 14, первый разрядный ключ 15, второй разрядный ключ 16, шину 17 нулевого потенциала, первый вход 18, второй вход 19 и установочный вход 20 устройству. Делительное устройство работает следуклцим образом. Если напряжения числителя и знаменателя (DX, Ujj соответственно) имеют одинаковую полярность, то логический О на выходе элемента Исключающее ИЛИ 4 переводит ключи 7 и 5 в такое состояние, при котором на выход ключей поступают неинвертируемые входные напряжения (в ключе 7 - напряжение числителя U-)( , в ключе 5 напряжение UQ эталонного источника 13). В случае/ когда напряжения 1) и }у отрицательные выходы нуль-органов 1 и 2 находятся в состоянии логической 1), логическая 1, образующаяся на выходе элемента Исключающее ИЛИ 3 переводит ключ б в такое состояние, при котором выход интегрирующего усилителя 8 подсоединяется к инвертирующему входу блока 10 сравнения, а выход ключа 7 - к неинвертирующему входу этого блока., ; Если напряжения } и Ug положительные, то логический О на выходе элемента Исключакяцее ИЛИ 3 переводит ключ 6 в такое состояние, при котором выход интегрирующего усилителя 8 подсоединяется к неинвертирующему, а выход ключа 7 - к инвертирующему входу блока 10. сравнения. При поступлении команды, разрешающей измерение отнотиения (размьакаются кгаочи 15 и 16), на выходе Интегрирующего усилителя 8 (и соответствен.но на входе блока 10 сравнения) появляется. Напряжение U, определяемое формулой Us К и, .t (1). На второй вход блока сравнения поступает напряжение числителя. При равенстве UQ Ux Срабатывает блок 10 сравнения и закрывает ключ 5, и напряжение UQ эталонного источника 13 перестает поступать на второй интегрирующий усилитель 9 09 Kg- Upt; (2) так как U Ux - KY- и,, t Ux При Kg « К,, т. е. если равны постоянные времени интегрирования интегрирующих усилителей 8 и 9, то Up Ux. :/ Если напряжение числителя и знаме нателя раз нополярные, то логическая 1 на выходе элемента Исключающее ИЛИ 4 перводит ключи 7 и 5 в такое состояние, при котором на вход ключей поступают инвертированные входные напряжения с выходов инвертирующих усилителей 11 и 12 соответственно. Когда напряжение.числителя положительное, логическая 1 на выходе элемента Исключающее ИЛИ 3 переводит ключ 6 в положение, соответствующее отрицательным ВХОДНЕЛМ сигналам. При отрицательном напряжении числителя логический О на выходе элемента Исключающее ИЛИ 3 переводит ключ 6 в состояние, соответствующее положитель ным входным сигналам. Динамика работы схемы при этом не меняется. Таким образом, обеспечивается возможность деления напряжения в четырех квадрантах. Формула изобретения Делительное устройство, содержащее первый интегрирующий усилитель с разрядным ключом в цепи обратной связи, вход первого интегрирующего усилителя является первым входом устройства, первый нуль-орган, первый вход которого является вторым входом устройства, а второй вход подключен к шине ну левого потенциала, источник эталонног напряжения, второй интегрирующий усилитель с разрядным ключом в цепи обратной связи, пиковый детектор и первый ключ, первый информационный вход которого подключен к выходу источника эталонного напряжения, а выход - к входу второго интегрирующего усилителя, выход которого подключен к входу пикового детектора, выход которого яв ляется выходом устройства, отличающееся тем, что, fc целью расширения диапазона изменения входны сигналов при сохранении точности и бы стродействия, оно содержит второй нуль-орган, первый вход которого является первым входом устройства, а второй вход подключен к шине нулевого потенциала, первый инвертирующий усилитель, вход которого подключен к второму входу устройства и второй инвертирующий усилитель, вход которого подключен к выходу источника эталонного напряжения, а выход подключен К второму информационному входу первого ключа, второй и третий двухпозиционные ключи, первый и второй элементы Исключающее ИЛИ и блок сравнения , причем выход первого интегрирующего усилителя подключен к первому информационному входу второго двухпозиционного ключа, выходы которого подклю(Чены к входам блока сравнения, выход которого подключен к первому управляющему входу первого ключа, первый информационный вход третьего двухпозиционного ключа подключен к второму входу устройства, а второй информационный вход третьего двухпозиционного ключа подключен к выходу первого инвертирующего усилителя, управляющий вход третьего ключа подключен к первому входу первого элемента Исключающее ИЛИ, выход которого подключен к управлякнцему входу второго двухпозиционного ключа, выход третьего двухпозиционного ключа подключен к второму информационному входу второго двухпозиционного ключа, выход первого нуль-органа подключен к второму входу первого элемента Исключающее ИЛИ. и к первому входу второго элемента Исключающее ИЛИ, выход которого подключен к управляющему входу третьего двухпозиционного ключа и к второму управляющему входу первого ключа, выход второго нуль-органа подключен к второму входу второгчэ элемента Исклю чакхцее ИЛИ, управляющие входы разрядных ключей подключены к установочному входу устройства. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 594507, кл. G 06 G 7/16, 1976. 2.Авторское свидетельство СССР 456276, кл. С 06 G 7/16/ 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОЖИТЕЛЬНО-ДЕЛИТЕЛЬНОЕ УСТРОЙСТВО | 1993 |

|

RU2110091C1 |

| Устройство для контроля качества электрической изоляции | 2020 |

|

RU2730535C1 |

| ИЗМЕРИТЕЛЬ ВИБРАЦИИ | 2021 |

|

RU2783752C1 |

| Делительное устройство | 1978 |

|

SU742964A1 |

| Устройство для цифрового измерения частоты | 1989 |

|

SU1666965A2 |

| Интегратор | 1986 |

|

SU1401485A2 |

| ПОЛОСОВОЙ ФИЛЬТР С УПРАВЛЯЕМОЙ ПОЛОСОЙ ПРОПУСКАНИЯ | 2021 |

|

RU2758448C1 |

| ИЗМЕРИТЕЛЬ ВИБРАЦИИ | 2013 |

|

RU2536097C1 |

| Реле тока с зависимой характеристикой времени действия | 1982 |

|

SU1053203A2 |

| Устройство для измерения нелинейности пилообразного напряжения | 1983 |

|

SU1105830A1 |

Авторы

Даты

1980-11-30—Публикация

1979-01-12—Подача