Изобретение может использоваться в специализированных цифроаналоговых машинах с большим быстродействием и малыми массогабаритными характеристиками, в аналоговых машинах, в системах, где требуется производить одновременное умножение двух сомножителей с делением на третье входное напряжение или только вычисление произведения или деления двух входных величин.

Известны множительные устройства, основанные на использовании генераторов развертывающего типа (Темников Ф.Е., Славинский В.Л. Математические развертывающие системы. - М.: Энергия, 1970, с.87-102; а.с. N 200904, БИ N 17, 1967; а.с. N 218539, БИ N 17, 1968).

Известно делительное устройство, содержащее интегрирующий усилитель, вход которого соединен с выходной клеммой, а выход - с первым входом компаратора, вторая входная клемма соединена со вторым входом компаратора, выход которого соединен с управляющим входом модулирующего ключа, аналоговый вход модулирующего ключа соединен с выходом эталонного источника напряжения, выход моделирующего ключа соединен со входом второго интегрирующего усилителя, управляющие входы разрядных ключей подсоединены к третьей входной клемме, выход второго интегрирующего усилителя подсоединен к пиковому детектору (а. с. N 456276, кл. G 06 g 7/16).

Во всех подобных устройствах применяются в качестве интегратора или операционные усилители с конденсатором в обратной связи, что приводит к снижению быстродействия, или RC-звено, что приводит к большим погрешностям вычисления.

Использование микросхем серии 525 в качестве множительно-делительного устройства часто невозможно из-за невысокой полосы пропускания, особенно при выполнении операций над импульсными амплитудно-модулированными сигналами.

В качестве прототипа берется изобретение по а.с. 456276, кл. G 06 g 7/16.

Цель изобретения заключается в повышении быстродействия и увеличении точности множительно-делительного устройства.

Для этого в множительно-делительном устройстве знаменатель подается на один конец резистора, второй конец которого через второй резистор подключен к выходу масштабного усилителя с коэффициентом усиления K1 и через ключ к интегрирующей цепи, выход которой соединен с неинвертирующим входом масштабного усилителя и с одним из входов компаратора, на другой вход компаратора подается один из сомножителей числителя.

Выход компаратора через логическую схему И соединен с управляющим входом модулирующего ключа. Второй сомножитель числителя через резистор поступает на аналоговый вход модулирующего ключа. Общая точка резистора и модулирующего ключа через второй резистор подсоединена к выходу второго масштабного усилителя с коэффициентом усиления K1. Выход модулирующего ключа подсоединен к интегрирующей RC-цепи, выход которой подключен к пиковому детектору и к неинвертирующему входу масштабного усилителя.

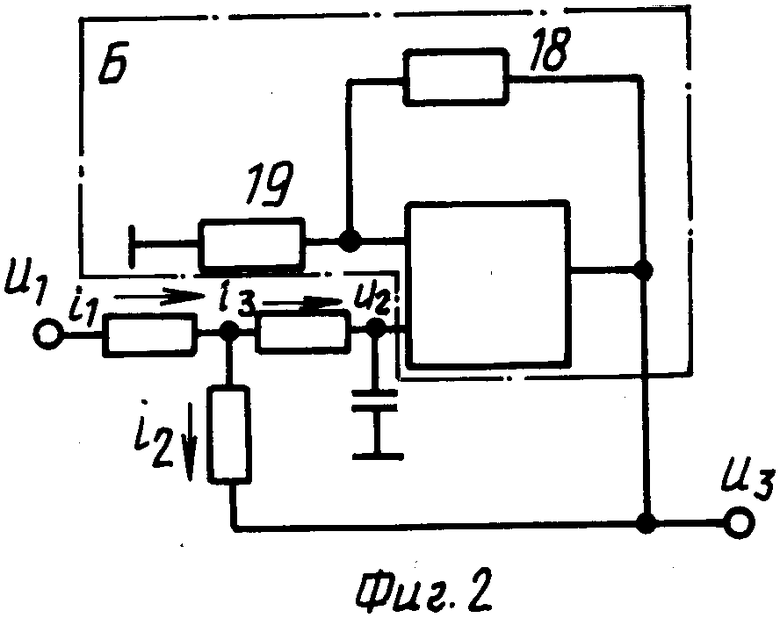

На фиг. 1, 2 приведена принципиальная электрическая схема предлагаемого множительно-делительного устройства.

Множительно-делительное устройство содержит два стабилизатора интегрирующего тока А, два интегрирующих RC-звена, компаратор 8, логическую схему И 9, управляющий ключ 6 и модулирующий ключ 10, пиковый детектор 16. Интегрирующее RC-звено содержит резистор 3 или (13), интегрирующий конденсатор 4 или (14), разрядный ключ 5 (15).

Стабилизатор интегрирующего выходного тока содержит два резистора 1 и 2 и масштабный усилитель 7.

Масштабный усилитель (фиг. 2) представляет операционный усилитель 7 (17) с коэффициентом усиления K, охваченный жесткой отрицательной обратной связью резисторами 18 и 19 с коэффициентом усиления по неинвертирующему входу  причем K1 << K.

причем K1 << K.

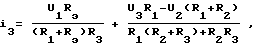

Ток через интегрирующий конденсатор i3 определяется выражением

где .

.

Для того чтобы интегрирующий ток был пропорционален только входному напряжению U1, второе слагаемое в уравнении должно обратиться в ноль.

U3R1 - U2(R1 + R2) = 0

При R1 = R2 = R имеем 2U2 = U3

Отсюда при коэффициенте усиления масштабного усилителя K1 = 2 второе слагаемое обращается в ноль, а интегрирующий ток i3 пропорционален входному напряжению.

Если входной ток компаратора 8 ( или пикового детектора) значителен, то интегрирующее напряжение можно снимать с масштабного усилителя (учтя соответственно его коэффициент усиления), при этом быстродействие устройства будет зависеть от быстродействия масштабного усилителя.

Множительно-делительное устройство работает следующим образом.

С приходом тактового импульса fт ключи управления 6 и 10 открываются, а разрядные ключи 5 и 15 закрываются, при этом предполагается, что входные напряжения Uзн на резисторе 1, Uсм2 на резисторе 11 и Uсм1 на входе компаратора 8 не равны нулю. Таким образом, на выходе конденсатора 4 появится напряжение

U4 = K1Uзн • t

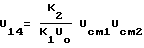

Это напряжение подается на вход компаратора 8, на второй вход которого подается один из сомножителей U см1. При равенстве U4 = Uсм1 закрывается модулирующий ключ 10 и напряжение перестает поступать на конденсатор 14, т. е.

U14 = K2Uсм2 • t ,

так как

U4 = Uсм1

Uсм1 = K1Uзн • t

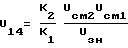

Следовательно, на выходе второго интегрирующего RC-звена будет напряжение U14, амплитуда которого равна искомому частному. При выполнении только операции деления вместо напряжения Uсм2 подается эталонное напряжение U0 и соответственно будет

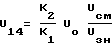

При выполнении операции умножения вместо напряжения Uзн подается эталонное напряжение U0 и

Предлагаемое множительно-делительное устройство имеет высокое быстродействие, малые габариты и небольшую потребляемую мощность.

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОЖИТЕЛЬНОЕ УСТРОЙСТВО | 1993 |

|

RU2082996C1 |

| АНАЛОГОВЫЙ ИНТЕГРАТОР | 1993 |

|

RU2088966C1 |

| Делительное устройство | 1979 |

|

SU783806A1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ (ЕГО ВАРИАНТЫ) | 1993 |

|

RU2088967C1 |

| УСТРОЙСТВО ДЛЯ АНАЛИЗА ГАЗОВЫХ, ЖИДКИХ И СЫПУЧИХ СРЕД | 1992 |

|

RU2069863C1 |

| Множительно-делительное устройство | 1978 |

|

SU1005081A1 |

| Множительно-делительное устройство | 1982 |

|

SU1030809A1 |

| МНОГОКАНАЛЬНЫЙ ФОРМИРОВАТЕЛЬ ИЗЛУЧЕНИЯ ИНЖЕКЦИОННЫХ ПОЛУПРОВОДНИКОВЫХ ЛАЗЕРОВ | 1996 |

|

RU2112198C1 |

| Широтно-импульсное множительное устройство | 1980 |

|

SU934493A1 |

| ФОТОМЕТР | 1990 |

|

RU2007050C1 |

Изобретение относится к вычислительной технике и может найти применение в аналоговых, цифроаналоговых, специализированных устройствах и вычислительных машинах. Целью изобретения является повышение быстродействия и увеличения точности. Устройство содержит два интегратора, каждый из которых содержит масштабный усилитель, конденсатор, усилитель, резисторы и разрядный ключ; устройство содержит также компаратор, элемент И, ключи; пиковый детектор и эталонный источник напряжения. 2 ил.

Множительно-делительное устройство, содержащее компаратор, пиковый детектор, источник эталонного напряжения, первый ключ и два интегратора, каждый из которых содержит масштабный усилитель, разрядный ключ, конденсатор и резистор, причем входом одного из сомножителей числителя и выходом устройства являются соответственно первый вход компаратора и выход пикового детектора, отличающееся тем, что в него введены второй ключ и элемент И, в каждый интегратор введены входной резистор и резистор положительной обратной связи, причем в каждом интеграторе первый вывод резистора соединен с входом масштабного усилителя, выходом разрядного ключа и через конденсатор - с шиной нулевого потенциала и аналоговым входом разрядного ключа, выход масштабного усилителя через резистор положительной обратной связи подключен к первому выводу входного резистора, входом знаменателя устройства является второй вывод входного резистора первого интегратора, первый вывод которого соединен с информационным входом первого ключа, выход которого подключен к второму выводу резистора первого интегратора, тактовый вход устройства соединен с управляющими входами разрядных ключей интеграторов, первого ключа и первым входом элемента И, второй вход которого подключен к выходу компаратора, второй вход которого соединен с выходом разрядного ключа первого интегратора, вход другого сомножителя числителя устройства соединен с вторым выводом входного резистора второго интегратора, первый вывод которого подключен к информационному входу второго ключа, управляющий вход которого соединен с выходом элемента И, а выход подключен к второму выводу резистора второго интегратора, первый вывод которого соединен с входом пикового детектора.

| SU, авторское свидетельство, 456276, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1998-04-27—Публикация

1993-06-15—Подача