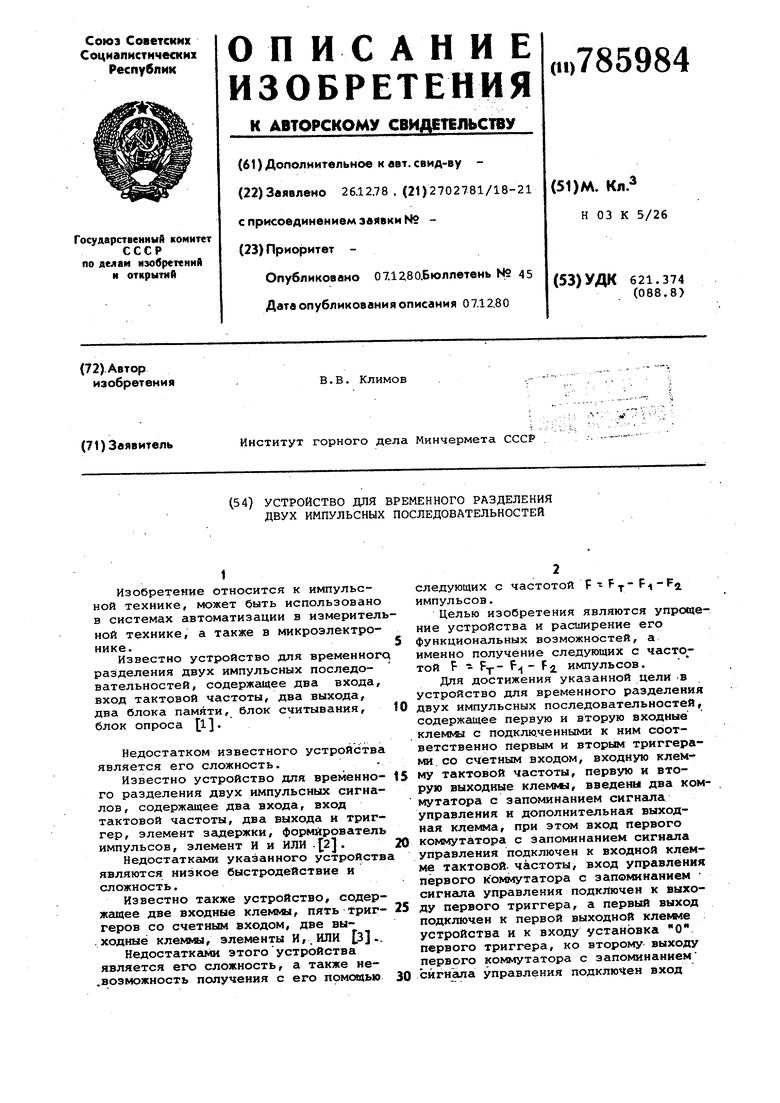

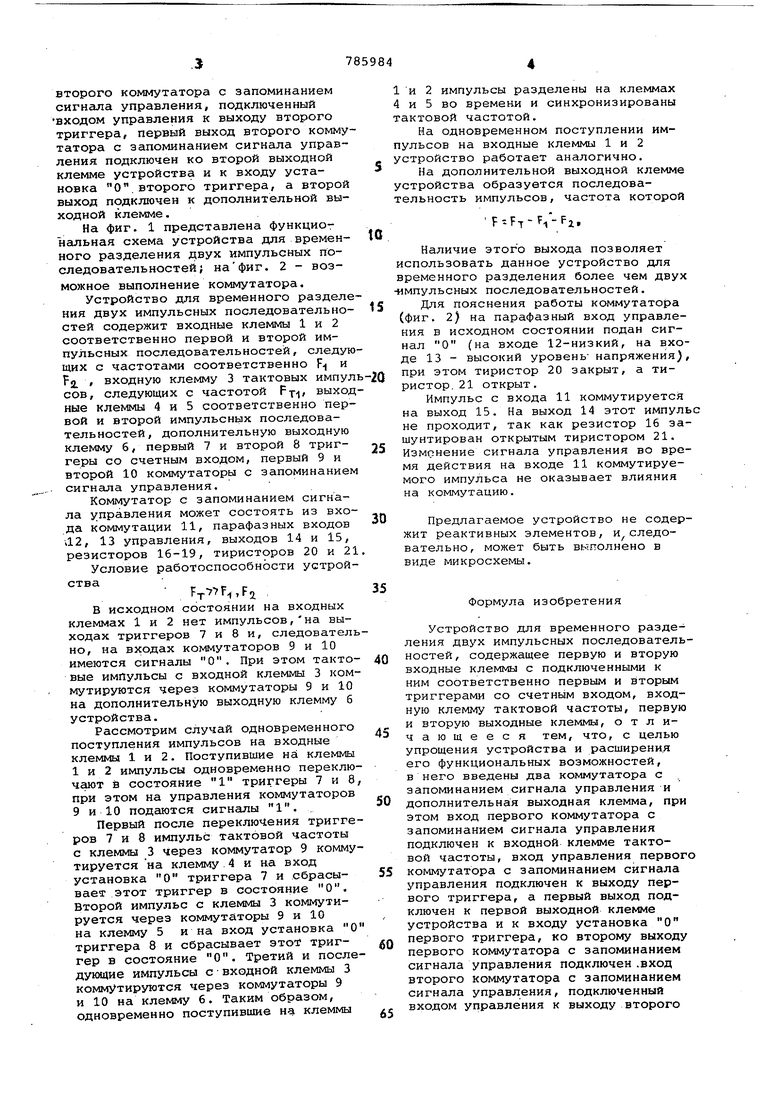

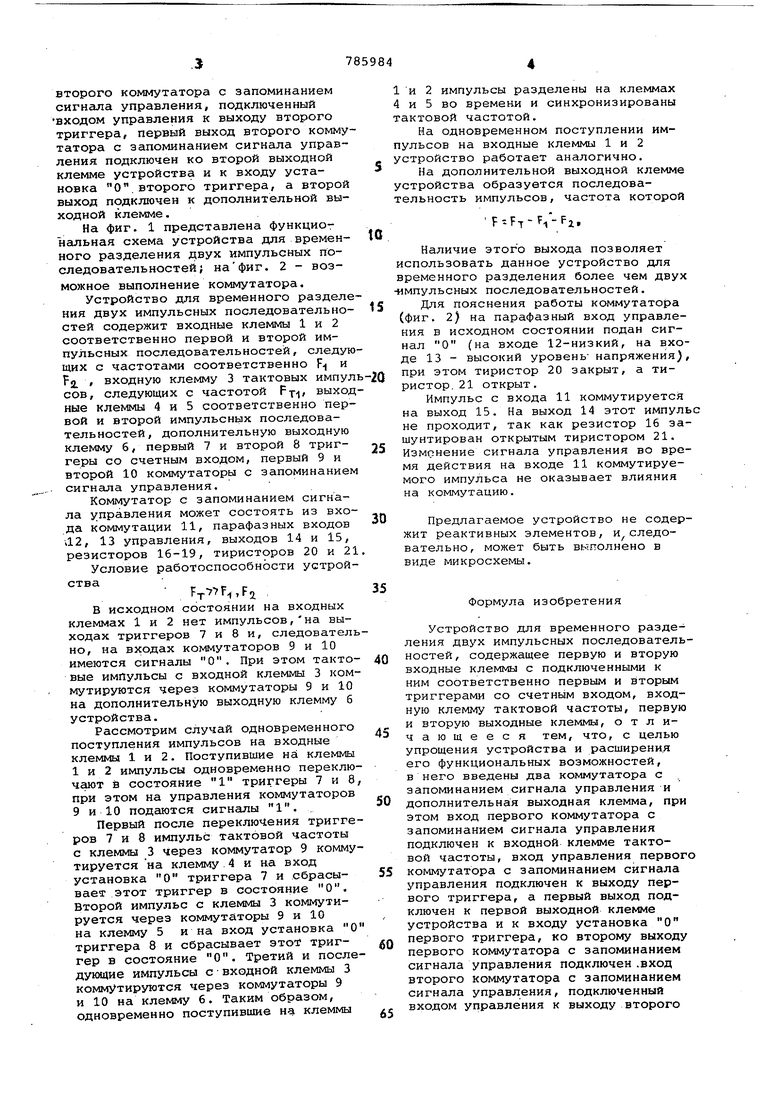

Изобретение относится к импульсной технике, может быть использовано в системах автоматизации в измерител ной технике, а также в микроэлектронике. Известно устройство для временног разделения двух импульсных последовательностей, содержащее два входа, вход тактовой частоты, два выхода, два блока памяти, блок считывания, блок опроса 1. Недостатком известного устройства является его сложность. Известно устройство для временного разделения двух импульсных сигналов, содержащее два входа, вход тактовой частоты, два выхода и триггер, элемент згщержки, формирователь импульсов, элемент И и ИЛИ . Недостатками указанного устройств являются низкое быстродействие и сложность. Известно также устройство, содержащее две входные клеммы, пять триггеров со счетным входом, две вы.ходныё клеммы, элементы И,. ИЛИ 3.. Недостаткгиад этого устройства является его сложность, а также не.возможность получения с его помощью следующих с частотой F FT импульсов. Целью изобретения являются упрощение устройства и расширение его функциональных возможностей, а именно получение следующих с частотой F - Fy- f а импульсов. Для достижения указанной цели -в устройство для временного разделения двух импульсных последовательностей, содержгидее первую и вторую входные клеммы с подключенными к ним соответственно первым и вторым триггерами, со счетным входом, входную клемму тактовой частоты, первую и вторую выходные клеммы, введены два коммутатора с запоминанием сигнгша управления и дополнительная выходная клемма, при этом вход первого коммутатора с запоминанием сигнала управления подключен к входной клемме тактовой, частоты/ вход управления первого коммутатора с запоминанием сигнала управления подключен к выходу первого триггера, а первый выход подключен к первой выходной клемме устройства и к входу установка О первого триггера, ко второму выходу первого кокплутатора с запоминанием сигнала управления подключен вход второго коммутатора с запоминанием сигнала управления, подключенный входом управления к выходу второго триггера, первый выход второго комму татора с запоминанием сигнала управления подключен ко второй выходной клемме устройства и к входу установка О, второго триггера, а второй выход подключен к дополнительной выходной клемме. На фиг. 1 представлена функциональная схема устройства для временного разделения двух импульсных последовательностей; нафиг. 2 - возможное выполнение коммутатора. Устройство для временного разделе ния двух импульсных последовательностей содержит входные клеммы 1 и 2 соответственно первой и второй импульсных последовательностей, следую щих с частотами соответственно F и РЗ. входную клемму 3 тактовых импул сов, следующих с частотой Ffi выход ные клеммы 4 и 5 соответственно первой и второй импульсных последовательностей, дополнительную выходную клемму 6, первый 7 и второй 8 триггеры со счетным входом, первый 9 и второй 10 коммутаторы с запоминанием сигнала управления. Коммутатор с запоминанием сигнала управления может состоять из входа коммутации 11, парафазных входов 12, 13 управления, выходов 14 и 15, резисторов 16-19, тиристоров 20 и 2 Условие работоспособности устройства F.,F.i В исходном состоянии на входных клеммах 1 и 2 нет импульсов,на выходах триггеров 7 и 8 и, следовател но, на входах коммутаторов 9 и 10 имеются сигналы О. При этом такто вые имяульсы с входной клеммы 3 ком мутируются через коммутаторы 9 и 10 на дополнительную выходную клемму б устройства. Рассмотрим случай одновременного поступления импульсов на входные клеммы 1 и 2. Поступившие на клеммы i VI 2 импульсы одновременно переклю чают в состояние 1 триггеры 7 и 8 при этом на управления коммутаторов 9 и10 подаются сигналы 1. , Первый после переключения тригге ров 7 и 8 импульс тактовой частоты с клеммы 3 через коммутатор 9 комму тируется на клемму . 4 и на вход установка О триггера 7 и сбрасывает этот триггер в состояние О. Второй импульс с клеммы 3 коммутируется через коммутаторы 9 и 10 на клемму 5 и на вход установка О триггера В и сбрасывает этот триггер в состояние О. Третий и после дующие импульсы свходной клеммы 3 коммутируются через коммутаторы 9 и 10 на клемму 6. Таким образом, одновременно поступившие на клеммы и 2 импульсы разделены на клеммах и 5 во времени и синхронизированы актовой частотой. На одновременном поступлении имульсов на входные клеммы 1 и 2 стройство работает аналогично. На дополнительной выходной клемме стройства образуется последоваельность импульсов, частота которой F--FT-FI-FI, Наличие этого выхода позволяет спользовать данное устройство для ременного разделения более чем двух мпульсных последовательностей. Для пояснения работы коммутатора (фиг. 2) на парафазный вход управления в исходном состоянии подан сигнал О (на входе 12-низкий, на входе 13 - высокий уровень напряжения), при этом тиристор 20 закрыт, а тиристор, 21 открыт. Импульс с входа 11 коммутируется на выход 15. На выход 14 этот импульс не проходит, так как резистор 16 зашунтирован открытым тиристором 21. Изменение сигнала управления во время действия на входе 11 коммутируемого импульса не оказывает влияния на коммутацию. Предлагаемое устройство не содержит реактивных элементов, и следовательно, может быть выполнено в виде микросхемы. Формула изобретения Устройство для временного разделения двух импульсных последовательностей , содержащее первую и вторую входные клеммы с подключенными к ним соответственно первым и вторым триггерами со счетнЫм входом, входную клемму тактовой частоты, первую и вторую выходные клеммы, отличающееся тем, что, с целью упрощения устройства и расширения его функциональных возможностей, в него введены два коммутатора с запоминанием сигнала управления и дополнительная выходная клемма, при этом вход первого коммутатора с запоминанием сигнала управления подключен к входной клемме тактовой частоты, вход управления первого коммутатора с запоминанием сигнала управления подключен к выходу первого триггера, а первый выход подключен к первой выходной клемме устройства и к входу установка О первого триггера, ко второму выходу первого коммутатора с запоминанием сигнала управления подключен .вход второго коммутатора с запоминанием сигнала управления, подключенный входом управления к выходу второго

триггера, первый выход второго коммутатора с запоминанием сигнала управления подключен ко второй выходной клемме устройства и к входу установка О втЬрого триггера, а второй выход подключен к дополнительной выходной клег.4ме,

Источники информации, принятые во внимание при экспертизе

свидетельство СССР 03 К 5/26,16.05.75.

свидетельство СССР 03 К 5/15,09.03.76.

свидетельство СССР 03 К 5/00,02.01.74

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для получения разностной частоты импульсов | 1980 |

|

SU924845A2 |

| Устройство для временного разделения импульсных сигналов | 1981 |

|

SU1007189A1 |

| Устройство для управления двухфазным асинхронным электродвигателем | 1980 |

|

SU868962A1 |

| Устройство для получения разностнойчАСТОТы иМпульСОВ | 1979 |

|

SU847504A1 |

| Каскадный коммутатор | 1989 |

|

SU1608792A1 |

| Устройство для управления тиристором | 1977 |

|

SU683020A1 |

| Устройство для управления двухфазным асинхронным электродвигателем | 1981 |

|

SU997221A2 |

| Способ регулирования частоты вращения трехфазного асинхронного электродвигателя | 1985 |

|

SU1376209A1 |

| Цифровой следящий электропривод | 1981 |

|

SU1008703A1 |

| Статический преобразователь частоты | 1988 |

|

SU1552313A1 |

IB

/Jo

Авторы

Даты

1980-12-07—Публикация

1978-12-26—Подача