рител

TopaN

систеи

к

телЮ

лей.

И5обретение относится к электроизме- ной технике, в частности к коммута- измерительных информационных предназначенным для подключения одному аналого-цифровому преобразова- мескольких первичных преобразоватеЦзлью

изобретения является расшире- использования путем введения одновременного фиксирования значений вхо,н Ь1х сигналов во всех каналах и исполь зования незадействованных каналов для пения верхней граничной частоты коммутируемых входных сигналов и коммутание области

ции импульсных сигналов с высокой скоростью нарастания.

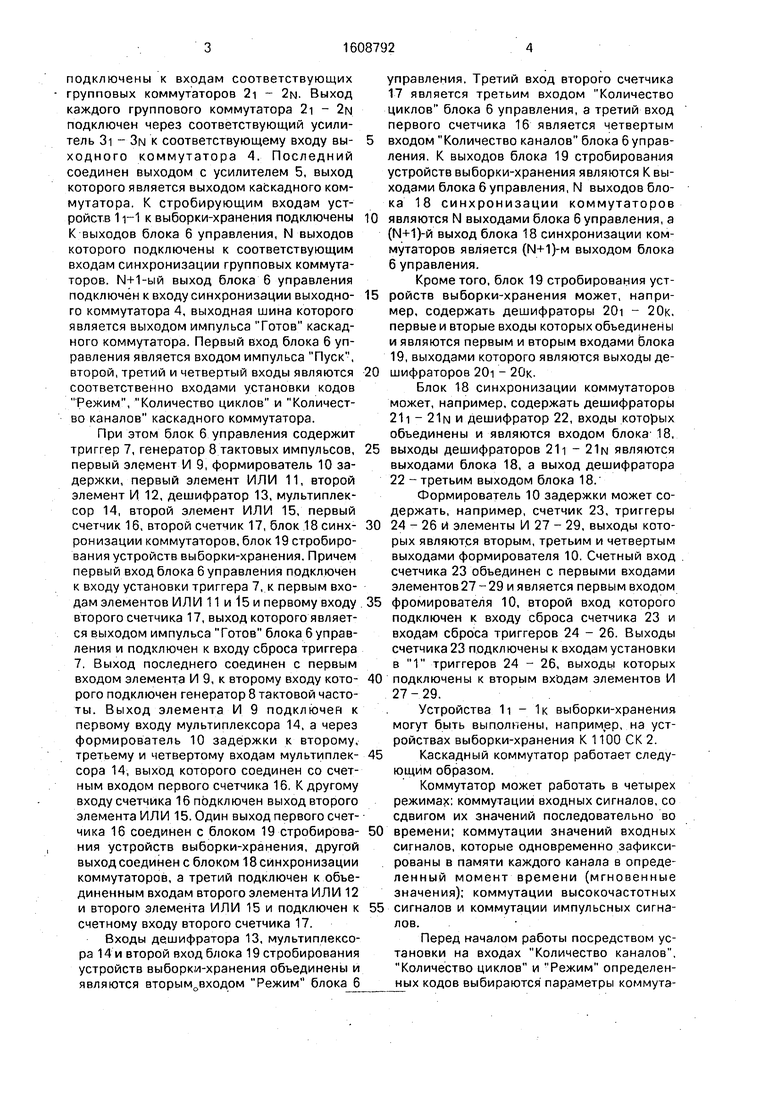

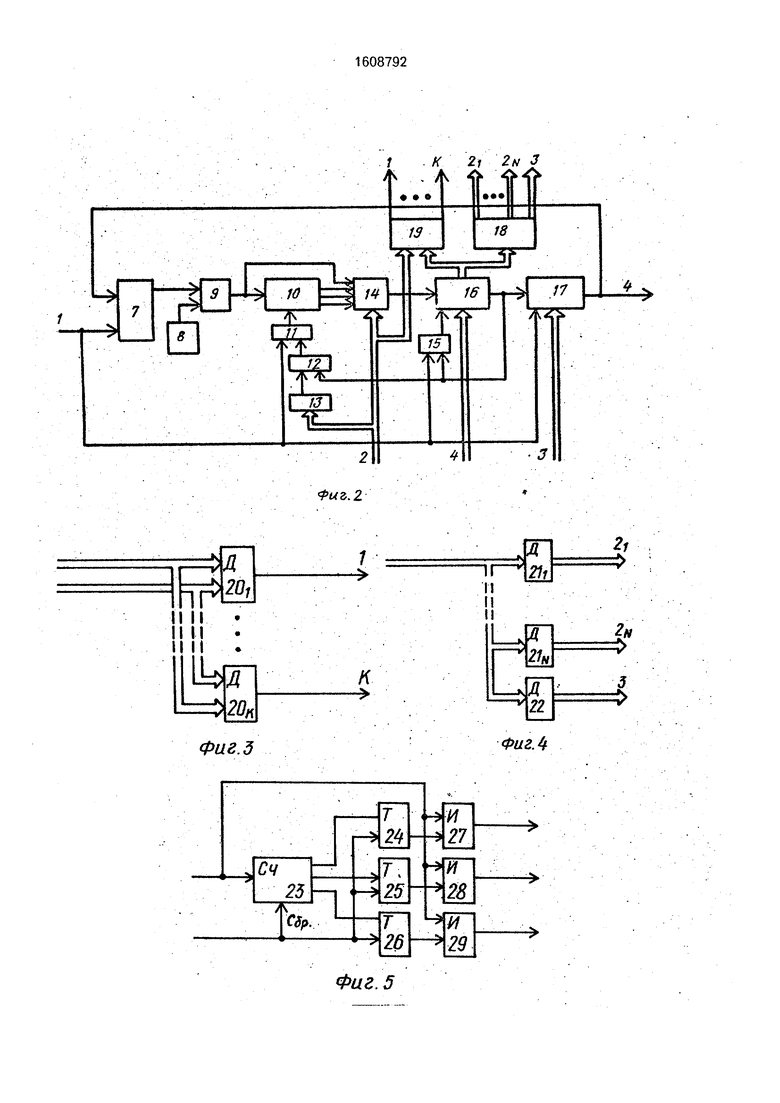

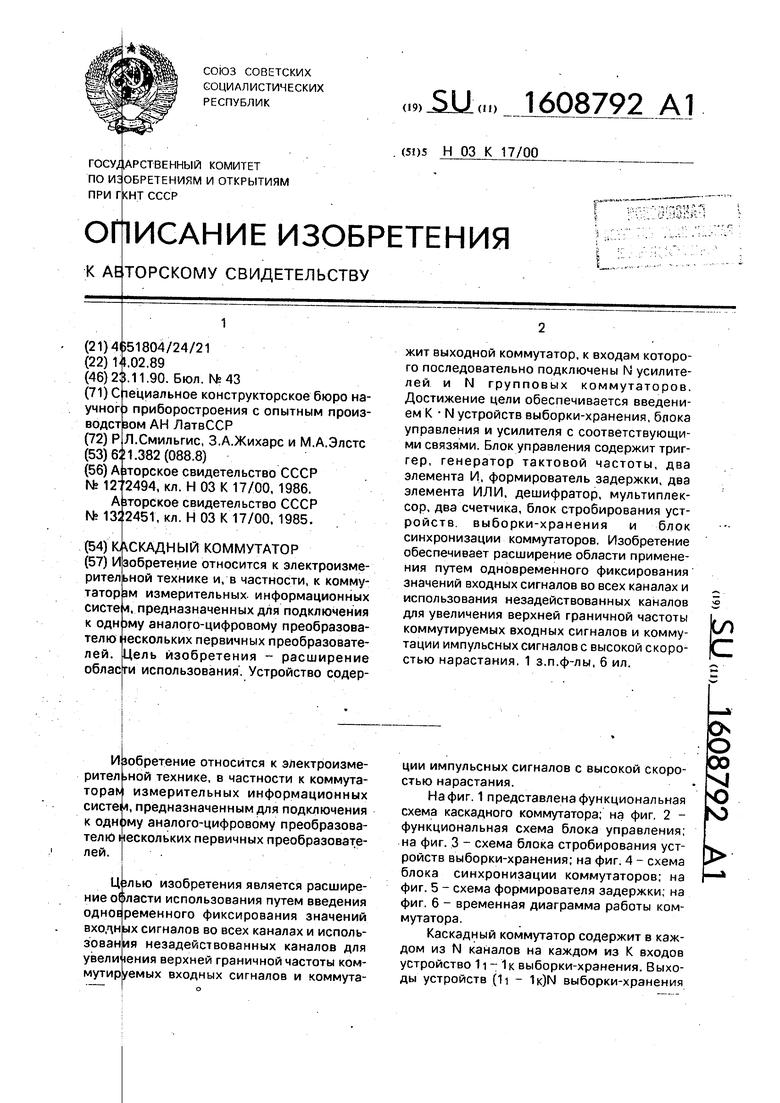

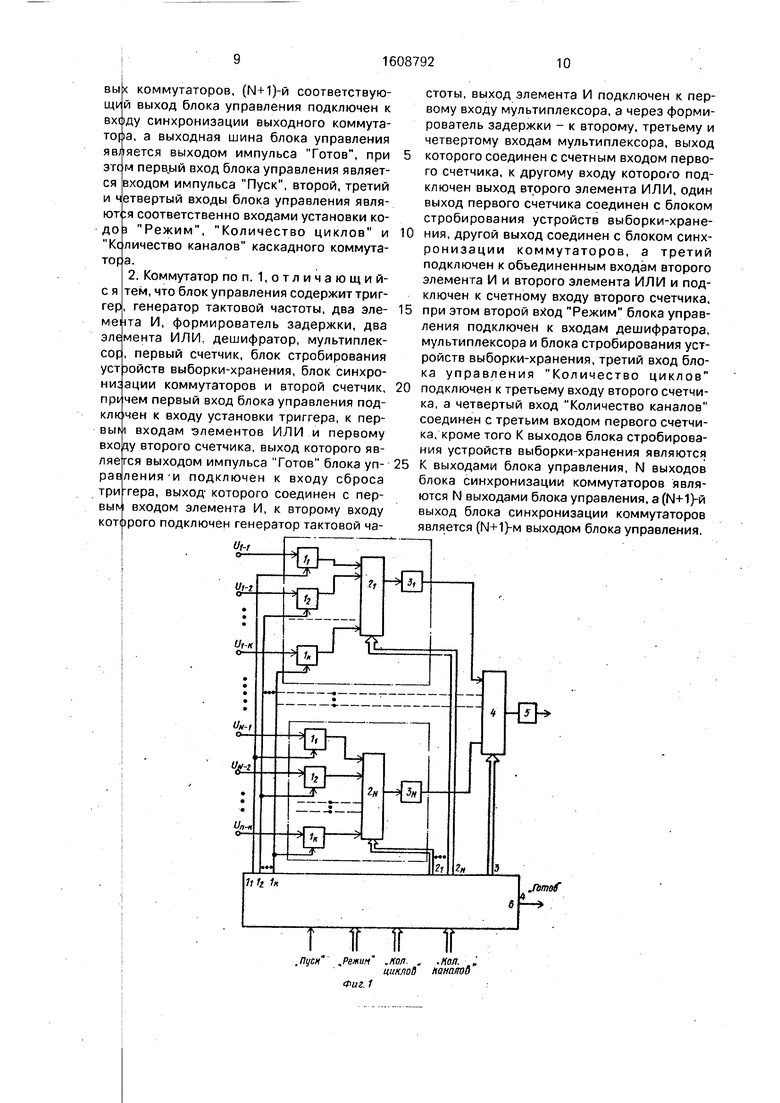

На фиг. 1 представлена функциональная схема каскадного коммутатора; на фиг. 2 - функциональная схема блока управления; на фиг. 3 - схема блока стробирования устройств выборки-хранения; на фиг. 4 - схема блока синхронизации коммутаторов; на фиг. 5 - схема формирователя задержки; на фиг. 6 - временная диаграмма работы коммутатора.

Каскадный коммутатор содержит в каждом из N каналов на каждом из К входов устройство 11 -: 1 к выборки-хранения. Выходы устройств (1i - IK)N выборки-хранения

О

о

00

ч ю

4D

подключены к входам соответствующих групповых коммутаторов 2i - 2N. Выход каждого группового коммутатора 2i - 2N подключен через соответствующий усилитель 3i - SN к соответствующему входу выходного коммутатора 4. Последний соединен выходом с усилителем 5, выход которого является выходом каскадного коммутатора. К стробирующим входам устройств 11-1 к выборки-хранения подключены К выходов блока 6 управления, N выходов которого подключены к соответствующим входам синхронизации групповых коммутаторов. N+1-ый выход блока 6 управления подключён к входу синхронизации выходного коммутатора 4, выходная шина которого является выходом импульса Готов каскадного коммутатора. Первый вход блока 6 управления является входом импульса Пуск, второй, третий и четвертый входы являются соответственно входами установки кодов Режим, Количество циклов и Количество каналов каскадного коммутатора.

При этом блок 6 управления содержит триггер 7, генератор 8 тактовых импульсов, первый элемент И 9, формирователь 10 задержки, первый элемент ИЛИ 11, второй элемент И 12, дешифратор 13, мультиплексор 14, второй элемент ИЛИ 15, первый счетчик 16, второй счетчик 17, блок 18 синх- ронизации коммутаторов, блок 19 стробиро- вания устройств выборки-хранения. Причем первый вход блока 6 управления подключен к входу установки триггера 7, к первым входам элементов ИЛ И 11 и 15 и первому входу второго счетчика 17, выход которого является выходом импульса Готов блока 6 управления и подключен к входу сброса триггера 7. Выход последнего соединен с первым входом элемента И 9, к второму входу которого подключен генератор 8 тактовой частоты. Выход элемента И 9 подключен к первому входу мультиплексора 14, а через формирователь 10 задержки к второму, третьему и четвертому входам мультиплек сора 14, выход которого соединен со счетным входом первого счетчика 16. К другому входу счетчика 16 подключен выход второго элемента ИЛИ 15. Один выход первого счетчика 16 соединен с блоком 19 стробирова- ния устройств выборки-хранения, другой выход соединен с блоком 1В синхронизации коммутаторов, а третий подключен к объединенным входам второго элемента ИЛИ 12 и второго элемента ИЛИ 15 и подключен к счетному входу второго счетчика 17.

Входы дешифратора 13, мультиплексора 14 и второй вход блока 19стробирования устройств выборюл-хранения объединены и являются вторым входом Режим блока 6

-

.

управления. Третий вход второго счетчика 17 является третьим входом Количество циклов блока 6 управления, а третий вход первого счетчика 16 является четвертым 5 входом Количество каналов блока 6 управления. К выходов блока 19 стробированмя устройств выборки-хранения являются К выходами блока 6 управления, N выходов блока 18 синхронизации коммутаторов 10 являются N выходами блока 6 управления, а (М+1)-й выход блока 18 синхронизации коммутаторов является (N+1)-M выходом блока 6 управления.

Кроме того, блок 19 стробирования уст- 15 ройств выборки-хранения может, например, содержать дешифраторы 20i - 20к, первые и вторые входы которых объединены и являются первым и вторым входами блока 19, выходами которого являются выходы де- 20 шифраторов 20i - 20к.

Блок 18 синхронизации коммутаторов может, например, содержать дешифраторы 21i - 21м и дешифратор 22, входы которых объединены и являются входом блока 18, 25 выходы дешифраторов 211 - 21ы являются выходами блока 18, а выход дешифратора 22 - третьим выходом блока 18.

Формирователь 10 задержки может содержать, например, счетчик 23, триггеры 30 24 - 26 И элементы И 27 - 29, выходы которых являются вторым, третьим и четвертым выходами формирователя 10. Счетный вход счетчика 23 объединен с первыми входами элементов27-29 и является первым входом 35 фромирователя 10, второй вход которого подключен к входу сброса счетчика 23 и входам сброса триггеров 24 - 26. Выходы счетчика 23 подключены к входам установки в 1 триггеров 24 - 26, выходы которых 40 подключены к вторым входам элементов И 27-29.

Устройства 1i - IK выборки-хранения могут быть выполнены, например, на устройствах выборки-хранения К 1100 СК 2. 45Каскадный коммутатор работает следующим образом.

Коммутатор может работать в четырех режима): коммутации входных сигналов, со сдвигом их значений последовательно во 50 времени: коммутации значений входных сигналов, которые одновременно зафиксированы в памяти каждого канала в определенный момент времени (мгновенные значения): коммутации высокочастотных 55 сигналов и коммутации импульсных сигналов.

Перед началом работы посредством установки на входах Количество каналов. Количество циклов и Режим определенных кодов выбираются параметры коммутации

каналов

К 15 19и

а именно количество коммутируемых в цикле коммутации и количество та их циклов, а также режим работы каскадного коммутатора.

Каскадный коммутатор осуществляет двухступенчатую коммутацию с возможно- стзю запоминания мгновенных значений вхэдных сигналов. Запоминание мгновен- ньх значений входных непрерывных сигна- -лов осуществляется устройствами 1i - 1к вфорки-хранения, содержащимися в каж- канале. Двухступенчатая коммутация ; ществляется N групповыми коммутаторами 2i - 2м и выходным коммутатором 4. При этом групповые коммутаторы 2i - 2ы и выходной коммутатор 4 коммутируются со сд зигом во времени (фиг. 6). Со сдвигом во времени происходит коммутация групповых коммутаторов 2i - 2м между отдельными /ппами.

В исходном состоянии в блоке 6 управ- триггер 7 и формирователь 10 задер- : 1 находятся в состоянии логического О, I 1ходы блока 19стробирования устройств ВЫ1 юрки-хранения находятся в состоянии логической 1.

По приходу импульса Пуск, триггер 7 пе еходит в состояние логической Г, а в счетчики 16 и 17 записываются установлен- ны на входах коды, определяющие количеств о каналов и количество циклов, соСтветственно. При этом триггер 7 разру- ша JT проход через логический элемент И 9 от генератора 8 тактовых импульсов. Начинается первый цикл коммутации.

При первом режиме работы входные Ui-i - Un-K проходят через устрой- 11 - 1 к выборки-хранения и последовательно один з а другим через групповые ко1« мутаторы 2i - 2ы, усилители 3. выходной KON мутатор4 на выход усилителя 5, который выходом каскадного коммутатора, t этом тактовые импульсы генератора 8 овой частоты, проходя через логический иент 9 и мультиплексор 14, поступают на ный вход,счетчика 16. Текущий код чика 16 дешифрируется дешифратора- - 2lN и дешифратором 22 блока 18 синрсронизации коммутаторов. Одновре- в блоке 19 стробирования устройств выборки-хранения дешифраторами 20i - : дешифрируется код режима, поступаю- на вход Режим блока 6 управления. 1ифраторы201-20к,211-21н и 22 могут выполнены, например, на постоянном запоминающем устройстве - микросхемах 5РЕЗ, К 556РТ5, К 556РТ7 и т.д. Блоки 18 вырабатывают сигналы управления устройством (1.1 - 1.K)N выборки-хранения, гругповым и выходным коммутаторами.

дом

ос

Ф

ле1ния жк

ав

сигналы

ствз

является

npt,

так

эле

сче

сче

ми

СИ1

менно

выС

20к

щий

Дет

бЫТ1

10

20

При первом режиме работы на входы стробимпульса устройств (1i - IK)N выборки-хранения поступает логическая 1, Что обеспечивает проход входных сигналов через устройство 1i - 1к выборки-хранения в течение времени коммутации входных сигналов. К выходу первого группового коммутатора 2 подключается первый канал Ui-i. С задержкой времени (I тактовых импульсов, где 1 1, 2.... е) к выходу второго группового коммутатора подключается второй канал (U2-i). С такой же задержкой поочередно подключаются к выходам других N групповых коммутаторов последующие N входов 15 (UN-I). С задержкой времени (I тактовых импульсов, где I 1,2е) относительно группового коммутатора 2 включается выходной коммутатор 4, подключая на определенное время к выходу коммутатора соответствующий входной сигнал, проходящий через групповой коммутатор 2. После подключения первого канала каждой N группы (Ui-i, U2-1UN-I) к выходу коммутатора коммутируются аналогично вторые и последующие каналы каждой группы.

Таким образом коммутация продолжается до тех пор, пока счетчик 16 подсчитает заданное количество импульсов, соответствующее выбранному числу каналов Мвыбр. При переполнении счетчик 16 формирует импульс, который с выхода счетчика 16 поступает через логический элемент ИЛИ 15 на его вход, при этом записывая в счетчик 16 новый код вь1бранного количества каналов. Сформированный счетчиком 16 импульс поступает также на счетный вход счетчика 17, который подсчитывает количество циклов. Коммутация входных сигналов, согласно выбранному количеству каналов, продолжается до тех по р, пока счетчик 17 подсчитает заданное количество циклов. Затем счетчик 17 формирует сигнал окончания коммутации, который поступает на вход сброса триггера 7, чем запрещается проход 5 импульсов генератора 8 тактовых импульсов через логический элемент 9, и режим коммутации Г1рекращается. Сигнал окончания коммутации является одновременно сигналом Готов. Следующий режим коммутации начинается с приходом следующего импульса Пуск.

Во втором режиме работы мгновенные значения входного сигнала запоминаются одновременно во всех каналах устройством 1i - 1к выборки-хранения, после чего каждый канал последовательно один за другим подключается к выходу каскадного коммутатора аналогично, как и в первом режиме работы. Одновременная синхронизация всех устройств 1i - IK выборки-хранения

25

30

35

40

0

5

(перевод в состояние хранения) организуется блоком 19 стробирования устройств выборки-хранения перед каждым циклом коммутации. Для этого после поступления сигнала Пуск цикл коммутации начинается с заданной задержкой, соответствующей осуществляемому режиму и определяемой формирователем 10 задержки.

По истечении времени задержки этого режима блок 19 стробирования устройств выборки-хранения формирует на выходах(1 - К) логический О, и устройства (11 - IK)N выборки-хранения переходят в состояние хранения. Следующее состояние - слежения устройств (11 - IK)N выборки-хранения организуется после коммутации всех выбранных каналов. Для этого сигнал, сформированный счетчиком 16 через логические элементы И 12 и ИЛИ 11, сбрасывает формирователь 10 задержки, в результате чего организуется пауза для стробирования устройств (1i - IK)N выборки-хранения. После окончания коммутации, сброса триггера 7 блок 19 стробирования устройств выборки- хранения формирует на всех выходах логическую 1 и переводит устройства (11 - 1 K)N выборки-хранения в состояние слежения.

В формирователе 10 задержки тактовые импульсы генератора В тактовой частоты поступают на входы логических элементов И 27 - 29 с задержкой (через определенное количество импульсов), которая определяется счетчиком 23. По истечении времени задержки, т.е. когда происходит переполнение счетчика 23 на одном из его выходов формируется сигнал. Этот сигнал переводит в состояние единицы соответствующий триггер 24 - 26, который разрешает дальнейший проход импульсов тактовой частоты через логический элемент.

В третьем режиме каскадный коммутатор для увеличения частоты коммутации (т.е. частоты входных сигналов) запоминание мгновенных значений и их коммутацию осуществляет для каждого входного сигнала всеми группами каналов, где каждый канал группы работает со сдвигом во времени. При этом каждый входной сигнал подключается на соответствующий вход каждой груп- пы каналов, например первый коммутируемый сигнал поступает на Ui-i,...,

UN-I каналы, второй - Ui-2UN-2 каналы и

так далее до U i-к, UN-K. После сигнала Пуск одновременно запоминаются мгновенные значения всех входных сигналов. По прохождении времени, необходимого для стробирования устройств выборки-хранения, которое определяется формирователем 10 задержки и формируется на втором его выходе, начинается сцикл коммутации, выполняющийся аналогично, как в первом режиме работы. С соответствующим сдвигом относительно момента стробирования устройств 1l - IK выборки-хранения первых каналов

каждой группы Ui-i, U2-iUN-I стробируются вторые и последующие каналы каждой группы. Причем стробируются так, что частота коммутации fK определяется только параметрами быстродействия коммутаторов,

а не параметрами быстродействия устройств (1i - IK)N выборки-хранения.

В четвертом режиме работы (коммутация импульсных сигналов) каждый коммутируемый сигнал подключается на несколько

соответствующих входов каждой группы каналов, аналогично как и в третьем режиме. Отличие от третьего режима заключается в том, что уменьшается интервал времени между мгновенными значениями входного

сигнала, которые запоминаются в устройствах (1i - IK)N выборки-хранения за счет их стробирования со сдвигом во времени для каждого входного импульсного сигнала. После каждого такого запоминания устройствами (1i - IK)N выборки-хранения, далее коммутация входных сигналов организуется аналогично, как в первом режиме работы каскадного коммутатора.

Использование предлагаемого каскадного коммутатора позволяет получить в необходимый момент времени значения всех входных сигналов и создать многоканальные системы для комплексного исследования динамики контролируемых процессов.

Такие системы характеризуются простотой реализации и небольшой стоимостью, так как требуют только одного аналого-цифрового преобразователя или цифрового регистратора.

Формула изобретения

1. Каскадный коммутатор, содержащий выходной коммутатор, к входам которого подключены соединенные последовательно N усилителей и N групповых коммутаторов.

отличающийся тем. что, с целью расширения области использования, введены К N устройств выборки-хранения, блок управления и дополнительный усилитель, причем выход выходного .коммутатора подключен к входу дополнительного усилителя, выход которого является выходом каскадного коммутатора, К входов каждого из N групповых коммутаторов подключены к выходам устройств выборки-хранения, входы которых являются входами каскадного коммутатора, стробирую щие входы устройств выборки-хранения подключены к К соответствующим выходам блока управления. N соответствующих выходов которого подвключены к входам синхронизации N групповых коммутаторов. (М+1)-й соответствующей выход блока управления подключен к входу синхронизации выходного коммута- TOfia, а выходная шина блока управления является выходом импульса Готов, при этс м вход блока управления является входом импульса Пуск, второй, третий и четвертый входы блока управления явля- ютоя соответственно входами установки ко- до 3 Режим, Количество циклов и Количество каналов каскадного коммутатора.

2. Коммутатор по п. 1, о т л и ч а ю щ и й- с я тем, что блок управления содержит триггер, генератор тактовой частоты, два элемента И, формирователь задержки, два элемента ИЛИ, дешифратор, мультиплексор, первый счетчик, блок стробирования устройств выборки-хранения, блок синхро- ни;ации коммутаторов и второй счетчик, npi/чем первый вход блока управления под- клк чен к входу установки триггера, к первым входам элементов ИЛИ и первому вхоцу второго счетчика, выход которого яв- ляегся выходом импульса Готов блока управления-и подключен к входу сброса тритера, выход- которого соединен с пер- BbiN входом элемента И, к второму входу которого подключен генератор тактовой ча

,Пусн ..f ,коп. . .коп. , циклов каната

10

стоты, выход элемента И подключен к первому входу мультиплексора, а через формирователь задержки - к второму, третьему и четвертому входам мультиплексора, выход которого соединен с счетным входом первого счетчика, к другому входу которого подключен выход второго элемента ИЛИ, один выход первого счетчика соединен с блоком стробирования устройств выборки-хранения, другой выход соединен с блоком синхронизации коммутаторов, а третий подключен к объединенным входам второго элемента И и второго элемента ИЛИ и подключен к счетному входу второго счетчика. 5 при этом второй вход Режим блока управления подключен к входам дешифратора, мультиплексора и блока стробирования устройств выборки-хранения, третий вход блока управления Количество циклов 0 подключен к третьему входу второго счетчика, а четвертый вход Количество каналов соединен с третьим входом первого счетчика, кроме того К выходов блока стробирования устройств выборки-хранения являются 5 К выходами блока управления, N выходов блока синхронизации коммутаторов являются N выходами блока управления, а (N+1}-й выход блока синхронизации коммутаторов является (N+1)-M выходом блока управления.

jbmef

/ .К 2i 2ы 3

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1683015A1 |

| Устройство для тестового контроля и диагностики цифровых модулей | 1989 |

|

SU1700557A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для сопряжения ЭВМ с разноскоростными группами внешних устройств | 1990 |

|

SU1837302A1 |

| Многофункциональный цифровой коррелометр | 1986 |

|

SU1363246A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

| Статистический анализатор конечной разности фазы | 1987 |

|

SU1422182A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с периферийными устройствами | 1985 |

|

SU1285484A1 |

| Устройство для синхронизации многоканальных равнодоступных систем связи | 1977 |

|

SU681566A2 |

| Трехканальное резервированное устройство для синхронизации сигналов | 1988 |

|

SU1709316A1 |

Изобретение относится к электроизмерительной технике и, в частности, к коммутаторам измерительных информационных систем, предназначенным для подключения к одному аналого-цифровому преобразователю нескольких первичных преобразователей. Цель изобретения - расширение области использования. Устройство содержит выходной коммутатор, к входам которого последовательно подключены N усилителей и N групповых коммутаторов. Достижение цели обеспечивается введением K.N устройств выборки-хранения, блока управления и усилителя с соответствующими связями. Блок управления содержит триггер, генератор тактовой частоты, два элемента И, формирователь задержки, два элемента ИЛИ, дешифратор, мультиплексор, два счетчика, блок стробирования устройств выборки-хранения и блок синхронизации коммутаторов. Изобретение обеспечивает расширение области применения путем одновременного фиксирования значений входных сигналов во всех каналах и использования незадействованных каналов для увеличения верхней граничной частоты коммутируемых входных сигналов и коммутации импульсных сигналов с высокой скоростью нарастания. 1 з.п. ф-лы, 6 ил.

Фиг.5

Фиг. 5

ФигЛ

| Способ гальванического снятия позолоты с серебряных изделий без заметного изменения их формы | 1923 |

|

SU12A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Пневматический водоподъемный аппарат-двигатель | 1917 |

|

SU1986A1 |

| Насос | 1917 |

|

SU13A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| .СКАДНЫЙ КОММУТАТОР юбретение относится к электроизме- .ной технике и | |||

| в частности, к комму- м измерительных, информационных предназначенных для подключения |му аналого-цифровому преобразова- 1ескольких первичных преобразовате- ,ель изобретения - расширение и использования | |||

| Устройство содержит выходной коммутатор, к входам которого последовательно подключены N усилителей и N групповых коммутаторов | |||

| Достижение цели обеспечивается введением К -N устройств выборки-хранения, блока управления и усилителя с соответствующими связями | |||

| Блок управления содержит триггер, генератор тактовой частоты, два элемента И, формирователь задержки, два элемента ИЛИ | |||

| дешифратор, мультиплексор, два счетчика, блок стробирования устройств, выборки-хранения и блок синхронизации коммутаторов | |||

| Иэобретение обеспечивает расширение области применения путем одновременного фиксирования значений входных сигналов во всех каналах и использования незадействованных каналов для увеличения верхней граничной частоты коммутируемых входных сигналов и коммутации импульсных сигналов с высокой скоростью нарастания | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-11-23—Публикация

1989-02-14—Подача