дами упомянутых формирователей импульсов , выход распределителя через третий формирователь импульсов соединен с информационным входом триггера памяти, выходы которого соединены с первыми входами логических ,- ,элементов И, вторые входы которых соединены с выходом второго упомянутого формирователя импульсов, выход одного из логических элементов И соединен со входом счетчика посылок, вход сброса которого подключен к выходу второго логического элемента ИЛИ, один вход которого соединен с выходом второго логического элемента И, зведен дополнительный логический элемент ИЛИ, выход которого соединен со входом сброса триггера памяти, и два дополнительных формирователя импульсов, входы которых соединены С выходами распределителя, а выходы со входами каждого из упомянутых логических элементов ИЛИ, при этом третий вход дополнительного логического элемента ИЛИ соединен с выходом первого формирователя импульсов.

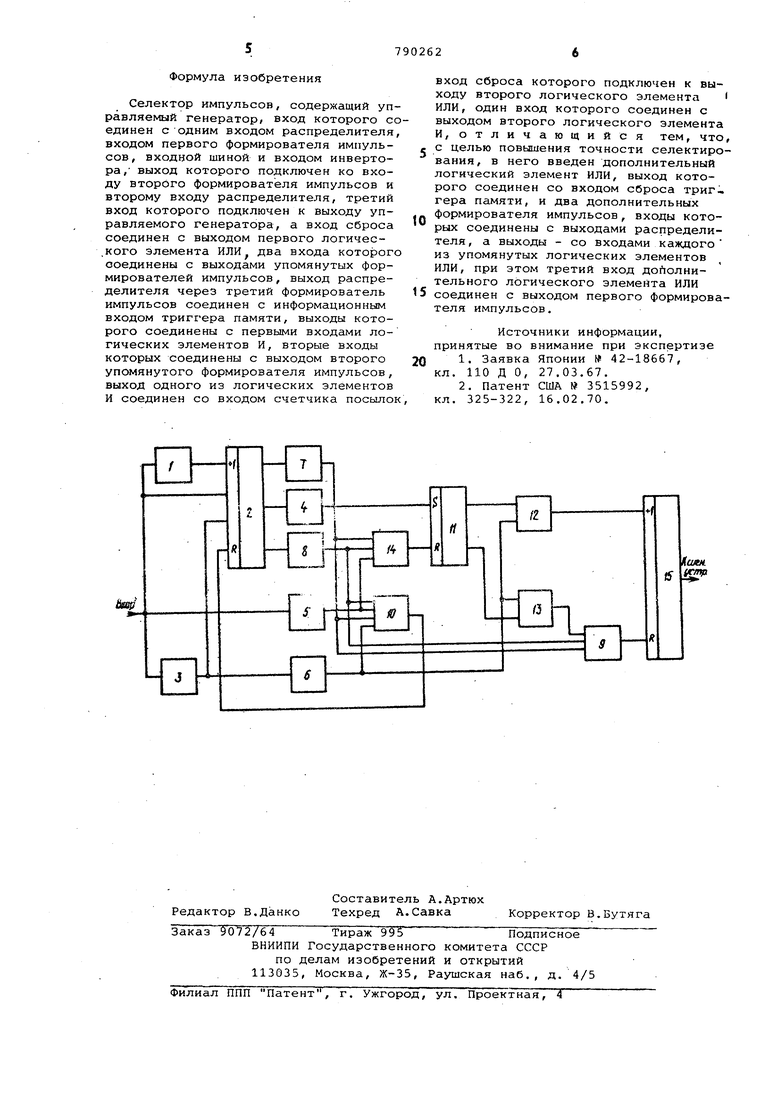

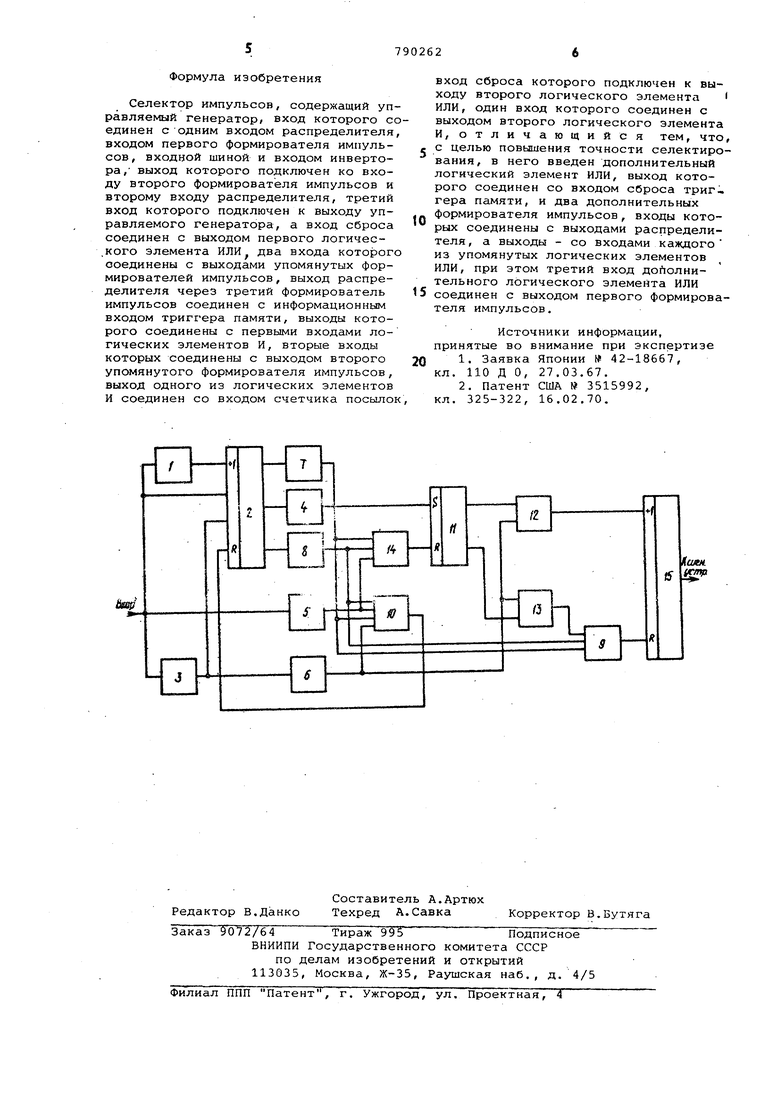

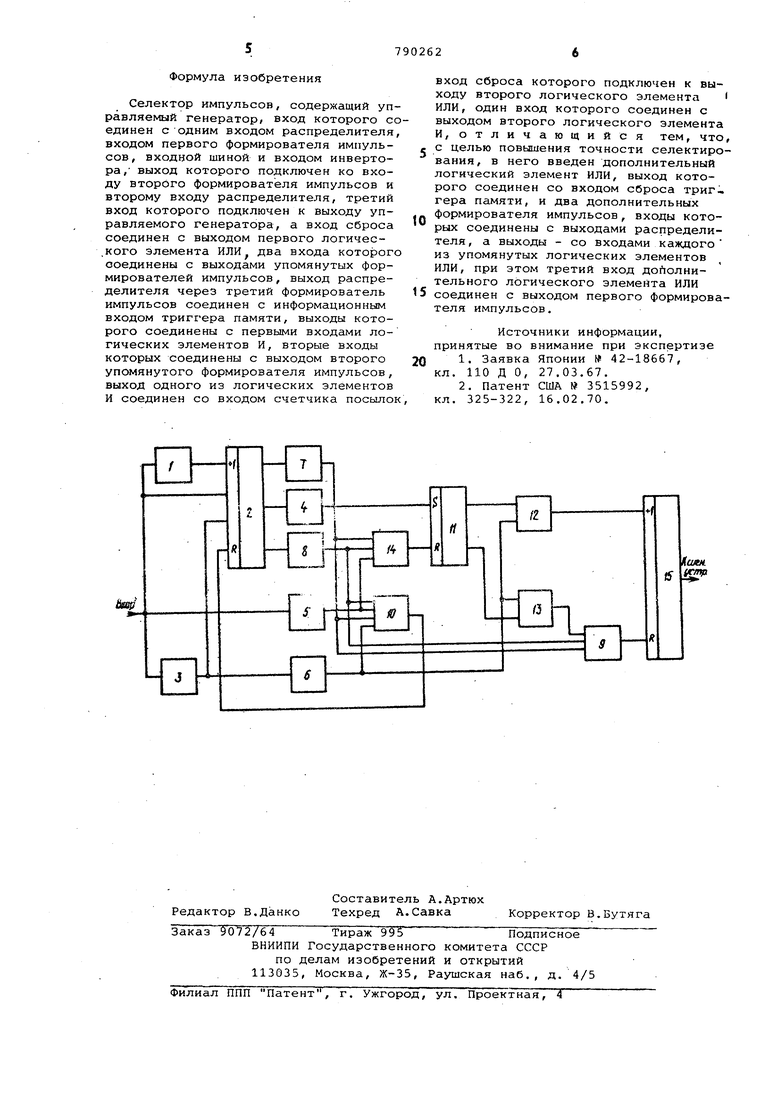

Структурная электрическая схема предлагаемого селектора приведена на чертеже.

Селектор содержит управляемый генератор 1, распределитель импульсов 2,состоящий из двоичного счетчика и дешифратора (не показан), инвертор 3, формирователи импульсов 4-6, дополнительные Формирователи импульсор 7 и 8, j-огические элементы ИЛИ 9 и 10, триггер памяти 11, логические элементы И 11 и 13, дополнительный логический элемент ИЛИ 14, счетчик посылок 15.

Селектируегиый сигнал подается на ВХОДНУЮ шину 16, выходной сигнал снимается с выхода 17.

Принцип работы селектора заключается в следующем.

С приходом заднего фронта сигнала паузы формирователем 5 вырабатывается короткий импульс, который через элементы ИЛИ 10 и 14 устанавливает в нуль соответственно запоминающий триггер 11, распределитель 2, а такж выходным сигналом синхронизируется уравляемый генератор импульсов 1 таким образом, чтобы начиналось формирование нового периода оклебаний, к тому же подается разрешающий потенциал на дешифратор распределителя 2 для выделения на его выходах отметок предельных значений длительности посылки. Начинается цикл селектировани посылки.

В случае посылки длительностью менее минимального предела при ее окончании формирователем б вырабатываетс .короткий импульс, который устанавливает, в нуль двоичный счетчик распределителя 2 через логический элемент ИЛИ 10. и счетчик посылок 15 через логические элементы И 13 и ИЛИ 9. Одновременно синхронизируется генератор импульсов.1, и с инвертора 3 подается разрешающий потенциал на дешифратор распределителя 2 для выделения на его выходе отметки предельного значения паузы. Селектор готов к началу цикла селектирования паузы

В случае посылки в пределах заданной длительности селектирование продолжается до ее окончания. В момент достижения минимума от переднего фронта импульса, вьщеленного дешифратором распределителя 2, формирователем 4 вырабатывается короткий импульс, который поступает на запоминающий вход триггера 11 и устанавливает его в состояние, при котором с прямого выхода подается потенциал на логический элемент И 12, разрешающий прохождение импульсов. Если посылка закончится в интервале времени между минимумом и максимумом предельных значений, то короткий импульс с формирователя б, образовавшийся от конца посылки, проходит через логический элемент И 12 на счетный вход двоичного счетчика посылок и запоминается. Процесс установки селектора в исходное состояние готовности к селектированию паузы происходит в соответствии с описанным.

В случае посылки длительностью более максимального лредела процесс селектирования продолжается в соответствии с описанным. В момент достижения максимума от переднего фронта импульса, выделенного дешифратором распределителя 2, формирователем 8 вырабатывается короткий импульс, который поступает через логические элементы ИЛИ на установочные входы соответственно запоминающего триггера 11, распределителя 2 и счетчика посылок 15 для сброса их в исходное состояние. Далее цикл селектирования продолжающейся посылки повторяется.

В случае паузы в пределах заданной длительности ее селектирование начинается в соответствий с описанием. При окончании паузы процесс начала селектирования посылки соответствует описанному.

в случае паузы длительностью более максимального-предела процесс селектирования соответствует описанию до момента достижения максимума. В момент максимума предела паузы от переднего фронта импульса, выделенного дешифратором распределителя 2, формирователем 7 вырабатывается короткий импульс, который поступает через логические элементы ИЛИ на установочные входы соответственно запоминающего триггера, распределителя 2 и счетчика посылок 15 для сброса Их в исходное (нулевое) состояние. Далее цикл селекции продолжающейся паузы повторяется.

Формула изобретения

Селектор импульсов, содержащий управляемый генератор/ вход которого соединен с одним входом распределителя, входом первого формирователя импульсов, входной шиной и входом инвертора, выход которого подключен ко входу второго формирователя импульсов и второму входу распределителя, третий вход которого подключен к выходу управляемого генератора, а вход сброса соединен с выходом первого логичес.кого элемента ИЛИ два входа которого соединены с выходами упомянутых формирователей импульсов, выход распределителя через третий формирователь импульсов соединен с информационным входом триггера памяти, выходы которого соединены с первыми входами логических элементов И, вторые входы которых соединены с выходом второго упомянутого формирователя импульсов, выход одного из логических элементов И соединен со входом счетчика посылок

вход сброса которого подключен к выходу второго логического элемента ИЛИ, один вход которого соединен с выходом второго логического элемента И, отличающийся тем, что, с целью повышения точности селектирования, в него введен дополнительный логический элемент ИЛИ, выход которого соединен со входом сброса триггера памяти, и два дополнительных формирователя импульсов, входы которых соединены с выходами распределителя, а выходы - со входами каждого из упомянутых логических элементов ИЛИ, при этом третий вход дополнительного логического элемента ИЛИ

s соединен с выходом первого формирователя импульсов.

Источники информации, принятые во внимание при экспертизе

1.Заявка Японии № 42-18667,

0 кл. 110 Д О, 27.03.67.

2.Патент США 3515992, кл. 325-322, 16.02.70.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения скорости телеграфирования | 1982 |

|

SU1059691A1 |

| Цифровой частотный демодулятор | 1991 |

|

SU1817249A1 |

| СИСТЕМА ДЛЯ ШИФРАЦИИ И ДЕШИФРАЦИИ КОМАНД | 1991 |

|

RU2043699C1 |

| Устройство для ввода-вывода информации | 1989 |

|

SU1686432A1 |

| Селектор кодовых посылок | 1983 |

|

SU1091328A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Селектор последовательности заданной длительности, содержащей импульсы заданной длительности | 1988 |

|

SU1555842A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Селектор импульсных сигналов | 1978 |

|

SU741446A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

Авторы

Даты

1980-12-23—Публикация

1977-10-14—Подача