Изобретение относится к вычислительной технике и может быть использовано в составе командного пункта многоадресной системы радиотелеуправления-телесигнализации для организации обмена информацией управляющей вычислительной системы с каналом связи.

Цель изобретения - повышение достоверности ввода информации.

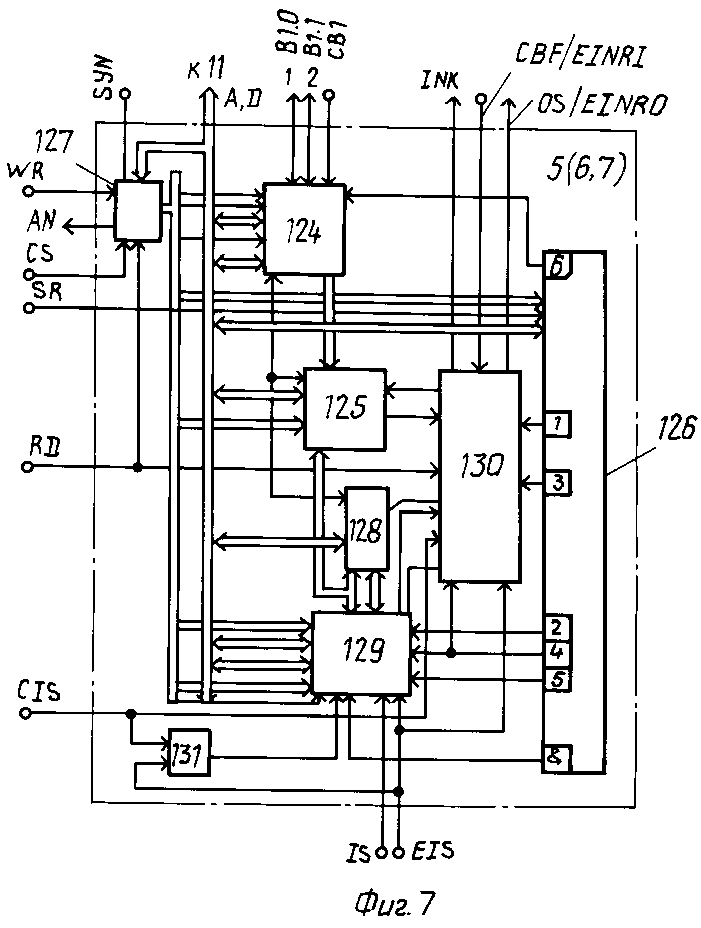

На фиг. 1 показано предложенное устройство; на фиг. 2 - временная диаграмма, поясняющая работу устройства в последовательном канале; на фиг. 3 - блок интерфейса; на фиг. 4 - схема блока синхронизации; на фиг. 5 и 6 - временные диаграммы блока синхронизации; на фиг. 7 - адаптер (М 1809ВВ1).

Устройство содержит блок 1 интерфейса, многоразрядный коммутатор 2-1, блок 3 синхронизации, выход 4 "Запрос прерывания", блок 5 приема, блок 6 передачи, блок 7 формирования сигналов прерывания, блок 8 памяти, шину 9 адреса данных, шину "0" 10 питания устройства, шину 11 уставки адреса устройства, вход 12 "Разрешение прерывания", выход 13 "Разрешение прерывания".

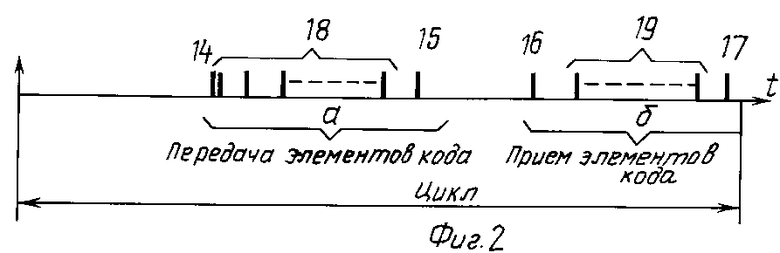

Временная диаграмма иллюстрирующая работу устройства в последовательном канале (циклограмма), приведена на фиг. 2, где обозначены: 14-17 - сигналы, соответствующие границам частей циклограммы, на выходах 1. . . 4 дешифратора 132 блока 3, 18 - запросы прерывания, соответствующие загрузке буферного регистра блока 6 передачи, 19 - запросы прерывания, соответствующие чтению буферного регистра блока 5 приема.

Блок 1 интерфейса обеспечивает связь устройства с процессором ЦВМ, имеющим магистральный параллельный интерфейс (МПИ) по ГОСТ 26.765.51-86, и выработку управляющих сигналов для обмена информацией с адресуемыми регистрами устройства.

Блок 1 интерфейса содержит адресный селектор 20, магистральные однонаправленные буферы 21, элемент НЕ 23, резистор 24, элемент И 25, блок 26 сравнения, дешифратор 27 адреса, D-триггеры 281-284, элемент НЕ 29, элементы И-НЕ 301 и 302.

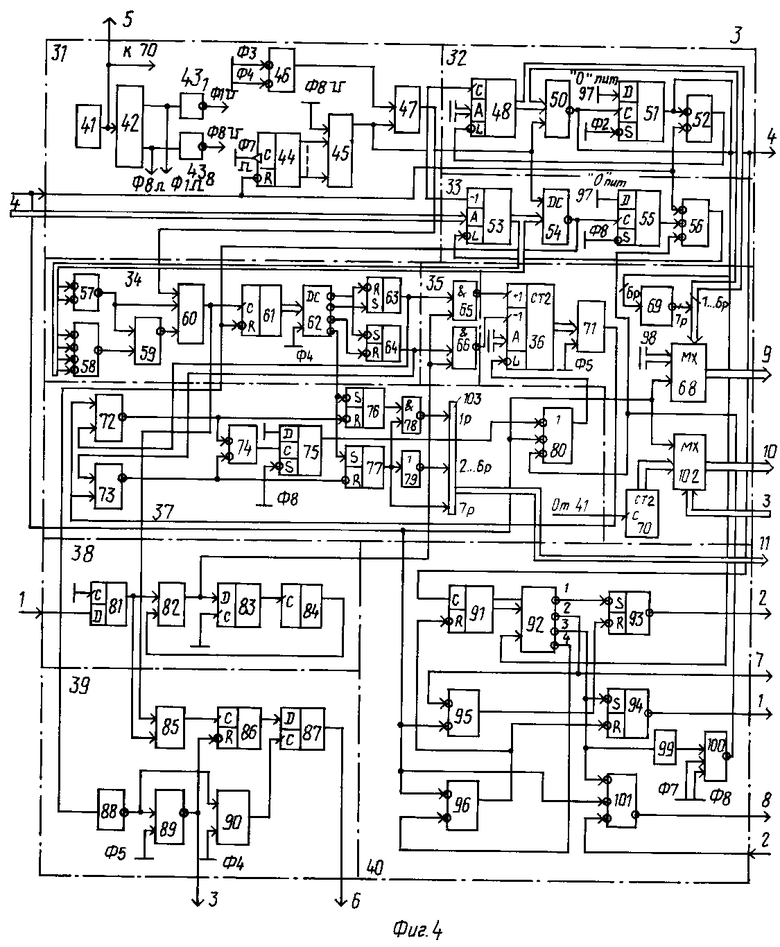

Блок 3 осуществляет подстройку фазы тактовых импульсов по фронтам информационных посылок, поступающих с выхода радиоприемного устройства линии связи, обеспечивает интегрированный прием информационных посылок, а также обеспечивает формирование циклограммы работы устройства в последовательном канале и сигналов начальной установки блока 8 памяти.

Блок 3 содержит задающий генератор 31, эталонный счетчик-делитель 32, управляемый счетчик-делитель 33, формирователь 34 сигналов фазовых зон; умножитель 35 сигналов, интегратор 36, пороговый блок 37, формирователь 38 сигналов, соответствующих фронтам посылок, интегратор 39 информационных посылок, формирователь 40 циклограммы и сигналов начальной установки блока 6 памяти, генератор 41 импульсов, распределитель 42 импульсов, элементы НЕ 431-438, счетчик-делитель 44, элемент И 45 (формирователь импульсов дискретизации фазы (ИДФ), элемент ИЛИ 46, элемент И 47, эталонный счетчик-делитель 48 (коэффициент пересчета Ко = 64), шину 49 ввода числа, дешифратор 50 нулевого кода, D-триггер 51 (формирователь отрицательного импульса предварительной записи в счетчик 48), элемент ИЛИ 52, вычитающий счетчик-делитель 53, дешифратор 54 нулевого кода, D-триггер 55 (формирователь отрицательного импульса предварительной записи в счетчик-делитель 53), элемент ИЛИ 56, элементы И 57-60, счетчик 61, дешифратор 62, триггеры 63 и 64 фазовых зон, элементы И 65 и 66, шину 67 ввода числа, коммутатор 2-1 68, элемент НЕ 69, счетчик 70, дешифратор 71 нулевого кода, элементы И 72 и 73, элемент ИЛИ 74, D-триггер 75 (формирователь отрицательного импульса предварительной записи в реверсивный счетчик 36) триггеры 76 и 77, элемент И 78, элемент НЕ 79, элемент ИЛИ 80, D-триггер 81, сумматор 82 по модулю два, D-триггер 83, триггер 84 со счетным входом, элемент И 85, счетчик 86, D-триггер 87, элемент НЕ 88, элементы И 89 и 90, счетчик 91, дешифратор 92, триггеры 93 и 94, элементы ИЛИ 95 и 96, шину "0" 97 питания устройства, шину 98 ввода числа Kо, элемент НЕ 99, элемент И 100, элемент ИЛИ 101, многоразрядный коммутатор 2-1 102, выходную шину 103 шифратора порогового блока 37.

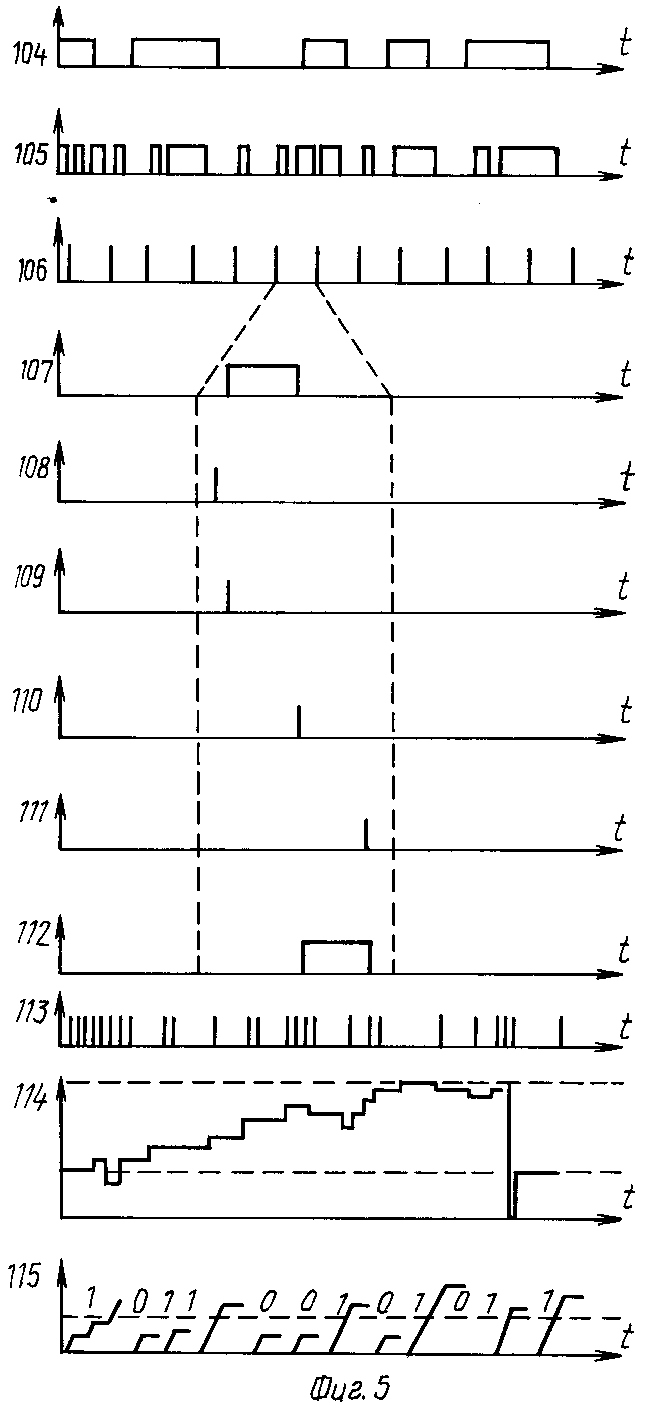

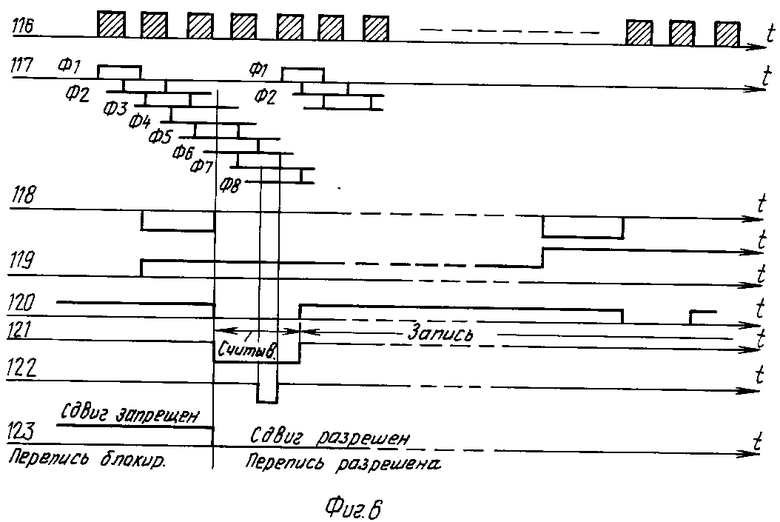

Временная диаграмма, иллюстрирующая работу блока 3, приведена на фиг. 5, 6.

На фиг. 5 обозначены: 104 - кодовая посылка, 105 - смесь кодовой посылки и помехи, 106 - сигнал на выходе дешифратора 54, 107 - сигнал на выходе триггера 63, 108-111 - сигнал на первом-четвертом выходах дешифратора 62, 112 - сигнал на выходе триггера 64, 113 - сигнал на выходе сумматора 82 по модулю два, 114 - сигнал на выходе интегратора 36, 115 - сигнал на выходе счетчика 86.

На фиг. 6 обозначены: 116 - сигнал на выходе генератора импульсов (F = 2,5 МГц), 117 - сигналы на первом-восьмом выходах распределителя импульсов Ф1, Ф2, . . . , Ф8 (T = 1,6 мкс), 118 - сигнал на четвертом выходе блока 3 (F = 300 Гц), 119 - сигнал на выходе счетчик 91, 120 - сигнал на выходе D-триггера 51, 121 - сигнал на выходе дешифратора 92, 122 - сигнал на выходе элемента И 100, 123 - сигнал на выходе триггера 94.

Из информационных посылок, поступающих из канала связи на выходе сумматора 82 по модулю два формирователя 38 формируются короткие импульсы, длительность которых (0,4 мкс) определяется величиной разности фаз сигналов на синхровходах D-триггера 81 (Ф1) и D-триггера 83 (Ф3), совпадающие по фронту с моментом перехода через нуль информационных посылок. Для осуществления привязки асинхронного сигнала, поступающего с выхода радиоприемного устройства линии связи к временной диаграмме работы блока 3 управления, используется D-триггер 81, с помощью которого осуществляется опрос входного информационного сигнала сигналом с первого выхода распределителя 42 импульсов, частота которого (T = 1,6 мкс) значительно превышает скорость работы в последовательном канале (F = 300 Гц) и, следовательно, при этом практически отсутствуют искажения входного сигнала, связанные с его временной дискретизацией.

При изменении значения сигнала, поступающего с выхода D-триггера 81 на вход сумматора 82 по модулю два, на выходе последнего возникает единичный сигнал, который поступает через D-триггер 83 на счетный вход триггера 84 и положительным фронтом перебрасывает его в противоположное состояние.

Изменившийся на выходе триггера 84 сигнал, введенный на вход сумматора 82 по модулю два, восстанавливает на выходе сумматора по модулю два сигнала "0".

Умножитель 35 сигналов контролирует попадание сигналов, соответствующих фронтам посылок, в одну из трех зон тактового интервала (интеpвал между соседними тактовыми импульсами): зоны отставания, зоны опережения и зоны синхронного приема. Формирователь обеспечивает деление тактового интервала на пятнадцать частей. Сигнал с выхода элемента 57 разрешает прохождение каждого четвертого импульса с первого входа на выход элемента 60, так как входы элемента 57 соединены с выходами младших разрядов счетчика-делителя 53. Выходной сигнал элемента 59 запрещает прохождение каждого 64-го импульса с первого входа на выход элемента 60. На входы элемента 85 поступают импульсы с выходов формирователя 34 (выход элемента 60) и D-триггера 81. Выходной сигнал элемента И 85 подсчитывается четырехразрядным счетчиком 86, сигнал с выхода старшего разряда которого в конце каждого такта считывается D-триггером 87. Если с выхода элемента И 85 снимается за такт восемь или больше импульсов, то с выхода D-триггера 87 снимается единичный уровень сигнала, в противном случае нулевой сигнал. Сигнал ИДФ с выхода элемента И 45 поступает на счетные входы эталонного 48 и управляемого 53 счетчиков-делителей, осуществляющих циклический счет импульсов ИДФ. Эталонный счетчик-делитель 48 настроен на номинальный коэффициент деления Ko (Ko = 64), а управляемый счетчик-делитель 53 работает в режиме вычитания, считая импульсы ИДФ от Kо или другого, устанавливаемого на него коэффициента K, равного (Kо + 1) или (Kо - 1), до 0. В нулевом состоянии на выходе дешифратора 54 управляемого счетчика-делителя 53 вырабатывается импульс, используемый для формирования тактового импульса. Коррекция фазы тактовых импульсов производится, если фронты принимаемых сигналов попадают в зону опережения или отставания. Для обеспечения достаточной помехоустойчивости синхронизации фазовое рассогласование интегрируется реверсивным счетчиком 36. Коррекция фазы производится, если пороговым блоком 37 зафиксировано определенное число импульсов рассогласования. Предварительно в реверсивный счетчик 36 выходным сигналом элемента ИЛИ 80 записывается число, равное половине его емкости. На выходе дешифратора 71 сигнал появляется при нулевом состоянии реверсивного счетчика 36, т. е. когда разность числа отстающих и опережающих импульсов равна числу, введенному в реверсивный счетчик 36 при его предварительной установке. Сигнал разности фаз между тактовым импульсом и границей кодовой посылки накапливается в интеграторе 36 и сравнивается с заданными порогами в пороговом блоке 37, выходной сигнал которого устанавливает на шине 103 код, равный (Kо + 1) ил (Kо - 1). Если содержимое интегратора 36 не превышает заданных порогов, на шине 103 устанавливается номинальный коэффициент деления Kо, и длина очередного такта является номинальной. В случае, если границы кодовых посылок опережают тактовые импульсы и сигнал положительной разности фаз накапливается в интеграторе 36 до величины, превышающей положительный порог, на управляемый счетчик-делитель устанавливается уменьшенный коэффициент деления Kо - 1 и очередной такт укорачивается на один интервал счетных импульсов. Одновременно сигнал порогового блока 37 в случае превышения порога устанавливает интегратор 36 в исходное состояние, после чего накопление сигнала возможной разности фаз в интеграторе 36 начинается сначала. В случае отставания границ кодовых посылок от тактовых импульсов при превышении содержимым интегратора 36 отрицательного порога на управляемый счетчик-делитель 53 устанавливается увеличенный коэффициент деления Kо + 1, и очередной такт удлиняется на один интервал счетных импульсов. Так происходит приближение тактовых импульсов к границам информационных посылок i-того источника. При этом фаза тактовых импульсов для i-того источника информационных посылок определяется состоянием Ф эталонного счетчика-делителя 48 в момент возникновения тактовых импульсов. Счетчик 91 осуществляет циклический счет эталонных тактовых импульсов с коэффициентом пересчета, равным числу тактов в цикле. При этом с выходов дешифратора 92 снимаются сигналы, соответствующие границам частей циклограммы работы устройства в последовательном канале (см. поз. 14. . . 17, фиг. 2). На выходе дешифратора 92 формируется сигнал, определяющий режим работы блока 8 памяти (запись-чтение).

На выходе элемента ИЛИ 101 формируется сигнал строба выборки блока 8 памяти в режимах записи и считывания. Триггеры 93 и 94 используются для формирования сигналов разрешения последовательного канала в блоках 6 передачи и 5 приема. С помощью счетчика 70 и многоразрядных коммутаторов 68 и 102 осуществляется начальная запись в блок 8 памяти, при этом в ячейках по всем адресам источников информации записывается в виде исходного значения номинальный коэффициент деления Kо. Во время действия сигнала начальной установки со счетчика 70 на адресный вход блока 8 памяти поступают последовательно адреса всех источников ввода последовательной информации. Блоки 5-7 конструктивно могут быть выполнены на основе программируемого параллельно-последовательно адаптера, предназначенного для использования в качестве базового элемента устройства ввода-вывода быстродействующих микроЭВМ.

Адаптер содержит блок 124 формирования сигналов обмена информацией, блок 125 формирования сигналов прерывания, регистр 126 программного управления, дешифратор 127, буферный регистр 128, блок 129 преобразования кодов, блок 130 управления, элемент И 131.

Регистр 128 может использоваться как буферный регистр обмена с регистром сдвига блока 129, если регистр сдвига служит преобразователем параллельного кода в последовательный, либо последовательного кода в параллельный. Схема обмена в составе блока 130 управления включает в себя трехразрядный счетчик для отсчета восьми сдвигов информации в регистре сдвига блока 129 преобразования кодов и схему формирования импульса переписи кода из регистра сдвига блока преобразования кодов в буферный регистр или из буферного регистра в регистр сдвига блока преобразования кодов. Импульс переписи формируется либо по внешнему стробу СВГ, либо по сдвигу байта. Импульс, свидетельствующий о состоявшемся обмене, выдается с выхода INR. Длительность импульса такая же, как у импульса сдвига на входном контакте CIS. Начальный сброс адаптера осуществляется сигналом SR, при этом все его регистры приводятся в состояние 00000000. Регистр 126 программного управления обеспечивает программное изменение внутренней конфигурации и задание режимов работы адаптера ввода-вывода. Все регистры адаптера имеют самостоятельные адреса для программного обращения к ним со стороны процессора ЦВМ по шине адрес-данные при выполнении операции чтения и записи. Регистр сдвига блока 129 преобразования кодов предназначен для образования последовательных каналов ввода-вывода и представляет собой регистр сдвига вправо (из старших разрядов в младшие). Регистр сдвига блока 129 преобразования кодов имеет доступ: со стороны внешнего объекта по цепям, образующим последовательный канал ввода-вывода; со стороны буферного регистра 128 по цепям переписи информации в режиме преобразования параллельного кода в последовательный и последовательного в параллельный.

Взаимодействие регистра сдвига блока 129 с внешними объектами по цепям последовательного канала осуществляется с использованием сигналов:

IS - входные данные последовательного канала;

EIS - разрешение входных данных;

CIS - синхронизация последовательного канала.

При каждом изменении уровня сигнала с пассивного на активный производится сдвиг содержимого регистра сдвига вправо на один разряд, а в самый левый разряд регистра в момент сдвига вводится информация с контакта IS. Сдвиг происходит только при наличии сигнала EIS.

На контакте OS/EINRO выдается информация из самого правого разряда регистра сдвига. При использовании адаптера в системе прерывания регистр блока 124 формирования сигналов обмена информацией блока 7 становится регистром прерываний, воспринимаемых в моменты их появления на контактах периферийной шины адаптера, а регистр 128 становится регистром маски. Маскирование осуществляется единицами в разрядах регистра 128 маски. Начальной установкой регистр маски 128 приводится в состояние 11111111, маскирующее все прерывания. Если в регистре прерывания появляются незамаскированные сигналы прерывания, вырабатывается сигнал INR.

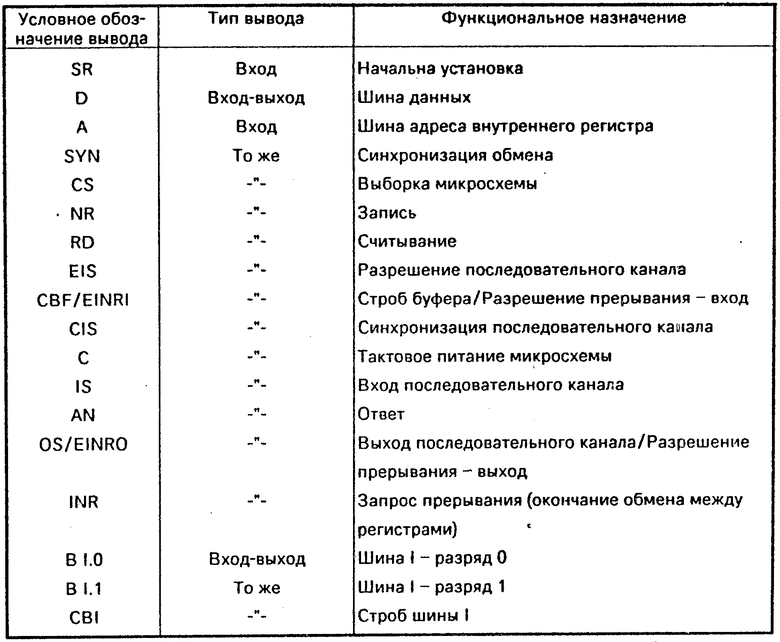

Теперь при поступлении сигналов EINRI и RD снимается сигнал INR, а на шину D выдается вектор прерывания из регистра вектора прерывания блока 125 формирования сигналов прерывания. Код вектора записывается в регистр вектора прерывания со стороны процессора ЦВМ программой начальной установки системы. Если в момент поступления сигнала EINRI сигнал INR не выдается, то вырабатывается сигнал EINRO и держится до тех пор, пока не прекращается EINRI. После получения вектора прерывания должно производиться чтение регистра прерывания в блоке 125 для определения конкретных причин прерывания. Соответствие обозначений входов и выходов микросхем М1809ВВ1 их функциональному назначению приведено в таблице.

Блок 8 памяти предназначен для записи и хранения информационного сигнала, характеризующего фазу тактовых импульсов. В состав блока 8 памяти входят накопитель и связанные с ним элементы формирования информационных входов, адресного входа, сигналов режима (запись-считывание) и строба выборки.

Накопитель представляет собой матрицу (например, из интегральных микросхем 185РУ2, каждая из которых состоит из накопителя 2k одноразрядных слова и K-разрядного дешифратора).

Блок 8 памяти имеет группу информационных входов, адресный вход, первый и второй входы, являющиеся соответственно управляющими входами задания режима работы блока (запись-считывание) и строба выборки, а также группу выходов. Режим записи блока памяти обеспечивается при поступлении на первый вход блока сигнала высокого уровня, на адресный вход кода адреса, на информационные входы - прямого кода записываемого слова. Запись производится при поступлении положительного импульса на второй вход блока памяти (строб выборки). Сигнал информации не должен меняться во время действия строба выборки. Режим хранения обеспечивается при наличии сигнала низкого уровня на втором входе блока 8 памяти. Режим считывания обеспечивается при поступлении на первый вход блока 8 памяти сигнала низкого уровня, на адресный вход-кода адреса. Считываемое слово появляется на выходах блока 8 памяти при поступлении положительного импульса "Строб выборки" на второй вход блока 8 памяти.

Устройство работает следующим образом.

Работа устройства происходит циклами. В каждом цикле организуется связь с одним из источников информации. Структура цикла работы устройства в последовательном канале представлена на фиг. 2. В первой половине цикла осуществляется передача информации с шины 9 адреса данных в канал связи. Во второй половине цикла осуществляется прием информации из канала связи и считывание ее на шину 9 адреса данных. Устройство осуществляет преобразование принимаемого из линии связи последовательного кода в параллельный, преобразование параллельного кода с шины 9 данных в последовательный и выдачу его в линию связи, а также формирование на выходе устройства сигналов запроса прерывания для инициирования обмена информацией с шиной 9 данных. Для буферизации преобразуемых байтов параллельного кода используются буферный регистр 128 БЛО2 блока 5 приема и блока 6 передачи. Обмен информацией между шиной 9 адреса данных и адресуемыми регистрами блоков 5-7 выполняется по сигналам, вырабатываемым блоком 1 интерфейса при поступлении на входы устройства управляющих сигналов. В начале каждого цикла обмена на шину 9 адреса данных устройства поступает код адреса регистра, затем данные. В каждом цикле обмена блок 1 интерфейса считывает код адреса с шины 9 адреса данных. Если поступивший адрес (разряды АДО9-АД12) совпадает с кодом адреса устройства, установленным на шине 5, то единичный сигнал с выхода блока 26 сравнения записывается в D-триггер 281 адресного селектора 20, выходной сигнал которого разрешает работу дешифратора 27 адреса, анализирующего записанные по сигналу "Обмен" в D-триггеры 282 и 283 адресного селектора 20 значения разрядов АДО7, АДО8 адреса, определяющих адресное обращение к одному из блоков 5-7 устройства. При этом на соответствующем выходе блока 1 интерфейса появляется сигнал выборки С, означающий выбор данного блока 5 (6 и 7) для участия в выполнении операций записи и чтения. Выборка внутреннего регистра выбранного блока 5 (6 и 7) осуществляется дешифрацией разрядов адреса АДО1-АДО5 с помощью внутреннего дешифратора 127 выбранного блока. Режим работы блоков 5-7 задается программно, посредством записи от процессора ЦВМ через шину 9 адреса данных кода настройки в регистры 126 программного управления этих блоков, производимой после прохождения сигнала сброса. Блок 5 приема программируется на ввод информации из канала связи. Блок 6 передачи программируется на вывод информации в канал связи. Блок 7 формирования сигналов прерывания программируется на прием сигналов прерывания, поступающих на входы периферийной шины блока 7, их обработку и выполнение всех необходимых по интерфейсу процессора ЦВМ процедур прерывания. Запись информации в буферный регистр 128 блока 6 передачи или чтения информации из буферного регистра 128 блока 5 приема выполняется по сигналу запроса прерывания, формируемому на выходе INR блока 7 формирования сигналов прерывания при поступлении сигналов в регистр прерывания блока 124 блока 7 с информационных входов периферийной шины В1 блока 7, которая постоянно открыта для записи в регистр прерывания активным сигналом (низкого уровня) на входе CB1 стробирования этой шины. Обмен информацией между регистром сдвига и буферным регистром в блоках 5 и 6 осуществляется по сдвигу байта путем отсчета числа сдвигов трехразрядным счетчиком схемы обмена в блоке 130 управления. Первоначальная установка этого счетчика на нуль делается подачей сигнала CBF. При отсутствии сигнала CBF перепись блокируется. При отсутствии сигнала EIS блокируются сдвиги. Импульс, свидетельствующий о состоявшемся обмене между регистром сдвига и буферным регистром, выдается с выхода INR ("Окончание обмена"). В режиме переписи из регистра сдвига в буферный регистр (при приеме информации из линии связи) обмен по сдвигу байта происходит после заполнения регистра сдвига байтом информации (т. е. по каждому 8-му сдвигу), а в режиме переписи из буферного регистра в регистр сдвига (при передаче информации в линию связи) по 1-му сдвигу и далее - после освобождения регистра сдвига от байта информации (т. е. по каждому 8-му сдвигу).

Передача информации в линию связи осуществляется при появлении на втором выходе блока 3 сигнала "Передача". Прием информации из линии связи ведется в течение всего времени, пока с первого выхода блока 3 поступает сигнал "Прием". По окончании приема информации от i-того источника на выходе INR блока 5 приема синхронно с очередным тактовым импульсом формируется сигнал "Окончание обмена между регистрами", используемый для формирования строба выборки при записи в блок 8 памяти. В i-ю ячейку блока 8 памяти записывается число, равное содержимому эталонного счетчика-делителя 48 блока 3 Фi (если Фi > 1/2 Kо) в момент возникновения тактового импульса, либо число равное сумме Фi' + Kо (если Фi < 1/2 Kо), где Kо - номинальный коэффициент деления (Kо = = 64) эталонного счетчика-делителя 48. Это достигается тем, что в качестве 7-го разряда в блок 8 памяти записывается инверсное значение 6-го разряда выходного кода счетчика 48. Постепенно, по мере работы с различными источниками кодовых посылок, все ячейки блока 8 памяти заполняются сигналами, характеризующими фазу управляемого счетчика-делителя 53 блока 3 на момент окончания приема информации от соответствующего источника. Двоичный код номера источника последовательной информации, с которым осуществляется связь в данном цикле работы устройства в последовательном канале, поступает через коммутатор 102 блока 3 на адресный вход блока 8 памяти с выхода (периферийной шины) адресуемого регистра, размещенного в составе блока 5 приема, куда этот код записывается с шины 9 данных в начале каждого цикла связи. При возобновлении приема информации от i-того источника в адресуемый регистр блока 124 блока 5 приема в начале цикла связи записывается с шины 9 данных код номера этого источника, и на адресном входе блока 8 памяти устанавливается i-тый адрес. В момент, соответствующий началу приема информации, синхронно с тактовым импульсом, поступающим от эталонного счетчика-делителя 48 блока 3 на третьем выходе дешифратора 92 блока 40 возникает сигнал, который переводит блок 8 памяти в режим считывания, а с выхода коммутатора 2 на вход блока 3 управления поступает код с выхода блока 8 памяти. Строб выборки при считывании формируется на выходе элемента ИЛИ 101 блока 40 блока 3. Выходным сигналом элемента И 100 осуществляется через элемент ИЛИ 56 запись в счетчик 53 кода с выхода блока 8 памяти и установка в исходное состояние через элемент ИЛИ 80 интегратора 36. Сравнение предлагаемого устройства с устройством-прототипом показывает следующее.

В известном устройстве-прототипе при переключении с одного источника на другой неизбежно возникает переходный процесс, в течение которого устройство входит в синхронизм, ввиду чего устойчивая связь с источником информации отсутствует. Это приводит к частичной потере информации и снижает, таким образом, достоверность ввода информации в известном устройстве. (56) Авторское свидетельство СССР N 1284389, кл. G 06 F 13/24, 1985.

Коффрен Дж. и Лонг В. Расширение микропроцессорных систем. М. : Машиностроение, 1987, с. 268.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| УСТРОЙСТВО СОПРЯЖЕНИЯ ЭВМ С ОБШИМ КАНАЛОМ СВЯЗИ | 1995 |

|

RU2103730C1 |

| Многоканальное устройство управления шаговым двигателем | 1990 |

|

SU1789970A1 |

| РЕЗЕРВИРОВАННАЯ СИСТЕМА | 1991 |

|

RU2010315C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ КОДОВЫХ КОМБИНАЦИЙ | 1992 |

|

RU2129338C1 |

| Кольцевая система для обмена информацией | 1988 |

|

SU1550522A1 |

| КОНТРОЛЛЕР КАНАЛА МЕЖБЛОЧНОГО ОБМЕНА | 2007 |

|

RU2345407C1 |

Изобретение относится к вычислительной технике и решает задачу повышения достоверности ввода информации. Сущность изобретения заключается в том, что по окончании приема информации от данного источника запоминается значение фазы тактовых импульсов, а в следующем цикле связи с данным источником устанавливается в качестве исходного зафиксированное ранее значение фазы тактовых импульсов. Это достигается тем, что в устройстве, содержащем блок интерфейса, блок синхронизации, блок приема, блок передачи, блок формирования сигналов прерывания, соединенные соответствующими связями, введены коммутатор и блок памяти, соединенные соответствующими связями. Предложенное устройство может быть использовано в составе командного пункта многоадресной системы радиотелеуправления - телесигнализации для организации обмена информацией управляющей вычислительной системы с каналом связи. 7 ил.

УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ, содержащее блок интерфейса, первая группа информационных входов-выходов которого является входом-выходом адреса данных устройства для подключения к ЦВМ, группа управляющих входов чтения, синхронизации, записи, входы блока интерфейса являются одноименными управляющими входами устройства для подключения к ЦВМ, информационные входы-выходы второй группы блока интерфейса объединены с группами входов-выходов блока приема, блока передачи и блока формирования сигналов прерывания, адресный вход блока интерфейса является адресным входом устройства, выходы записи, чтения, синхронизации блока интерфейса соединены с одноименными входами блоков приема, передачи и формирования сигналов прерывания, входы выборки которых соединены с выходами выборки блока интерфейса, выход признака последовательного канала блока передачи соединен через линию связи с каналом, выход "Ответ" блока интерфейса является соответствующим выходом устройства для подключения к входу запроса ЦВМ, выходы "Ответ" блоков приема, передачи и блока формирования сигналов прерывания объединены между собой и подключены к одноименному входу блока интерфейса, вход "Разрешение прерывания" устройства соединен с одноименным входом блока формирования сигналов прерывания, выход "Разрешение прерывания" которого является одноименным выходом устройства для подключения к ЦВМ, выход "Запрос прерывания" блока формирования сигналов прерывания является одноименным выходом устройства для подключения к ЦВМ, первый и второй выходы блока синхронизации соединены с входами "Разрешение последовательного канала", "Разрешение обмена" блока приема и блока передачи соответственно, выходы "Окончание обмена" соединены соответственно с первым и вторым информационными входами периферийной шины блока формирования сигналов прерывания, вход стробирования которого соединен с нулевой шиной устройства, первый вход задания режима работы блока синхронизации соединен через линию связи с каналом, третий и четвертый выходы блока синхронизации соединены с входами "Синхронизация последовательного канала" блока приема и блока передачи соответственно, пятый выход блока синхронизации соединен с входами тактового питания блоков приема, передачи и формирования сигналов прерывания, шестой выход блока синхронизации соединен с входом "Последовательная информация" блока приема, вход начала работы блока синхронизации соединен с входами "Начальная установка" блока приема, блока передачи и блока формирования сигналов прерывания и является входом "Сброс" устройства, отличающееся тем, что в него введены коммутатор и блок памяти, вход записи-чтения которого соединен с седьмым выходом блока синхронизации и управляющим входом коммутатора, первый информационный вход которого соединен с выходом блока памяти, выход "Окончание обмена" блока приема соединен с вторым входом задания режима работы блока синхронизации, восьмой выход которого соединен с входом синхронизации блока памяти, девятый и десятый выходы блока синхронизации соединены соответственно с информационным и адресным входами блока памяти, четвертый и пятый входы задания режима работы блока синхронизации соединены с первым и вторым разрядными выходами периферийной шины блока приема, группа выходов коммутатора соединена с группой входов задания режима работы блока синхронизации, одиннадцатый выход которого соединен с вторым информационным входом коммутатора, выходы "Ответ" блоков приема и передачи подключены к одноименному входу интерфейса.

Авторы

Даты

1994-04-15—Публикация

1991-05-30—Подача