Изобретение относится к электросвязи, преимущественно к передаче данных по каналам связи с помощью частотной модуляции.

Цель изобретения -повышение помехоустойчивости.

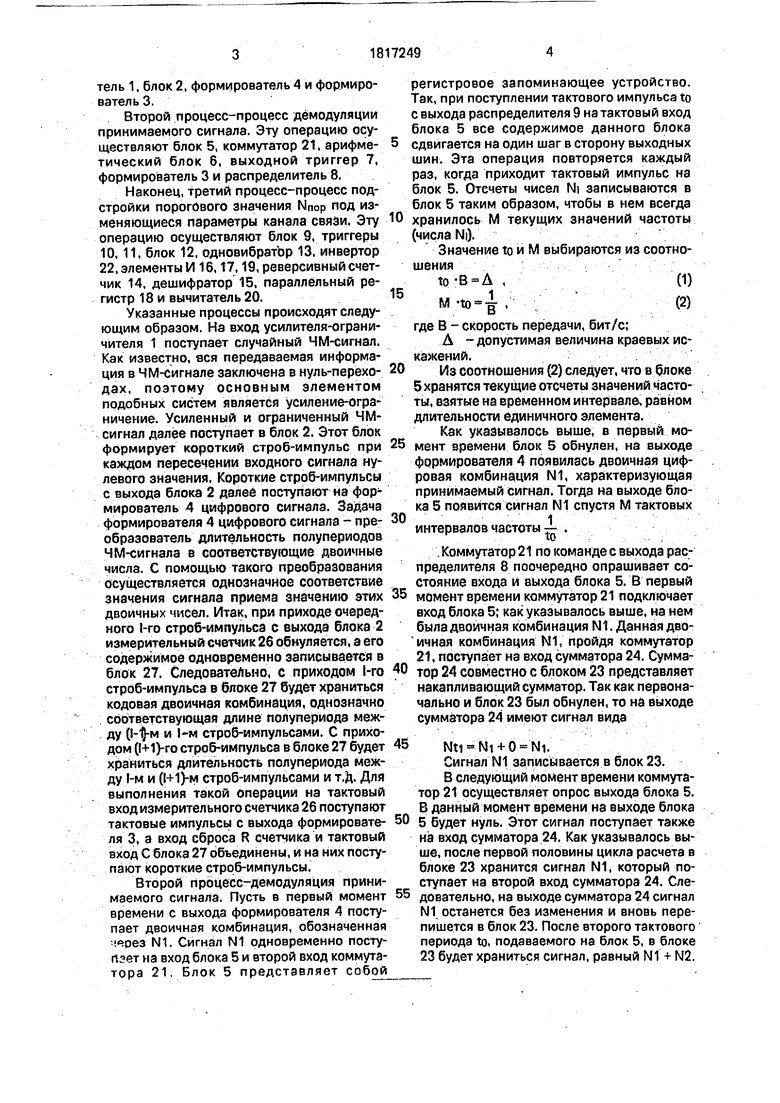

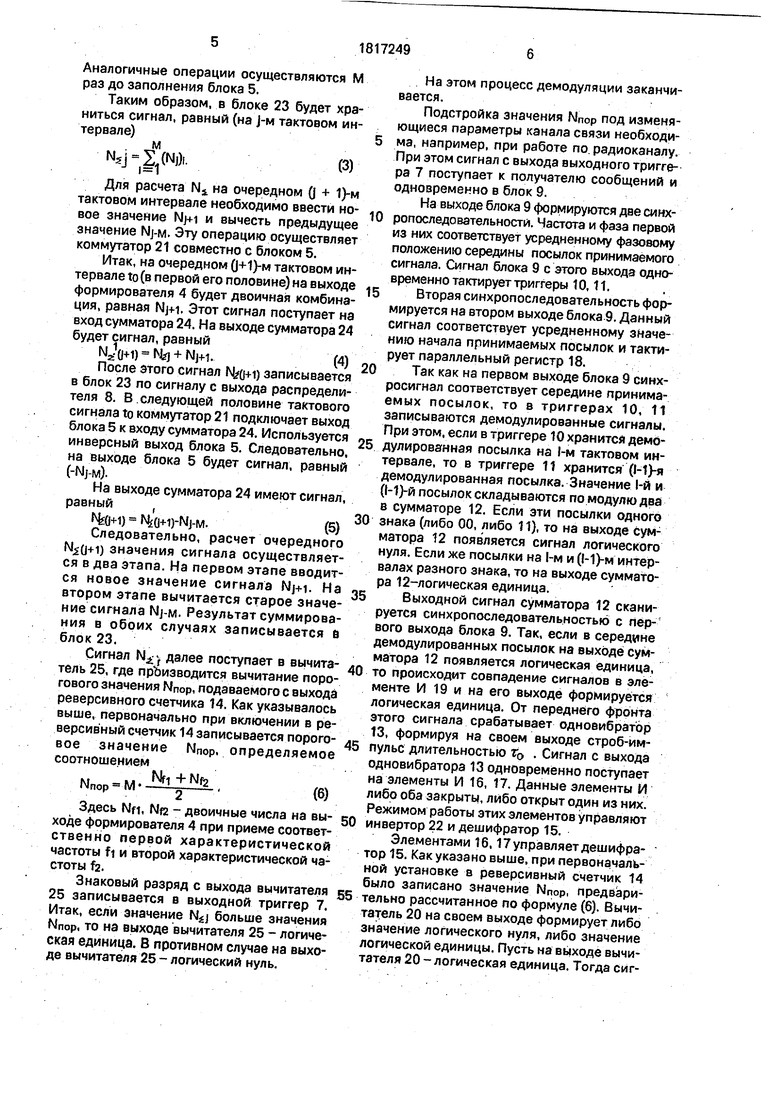

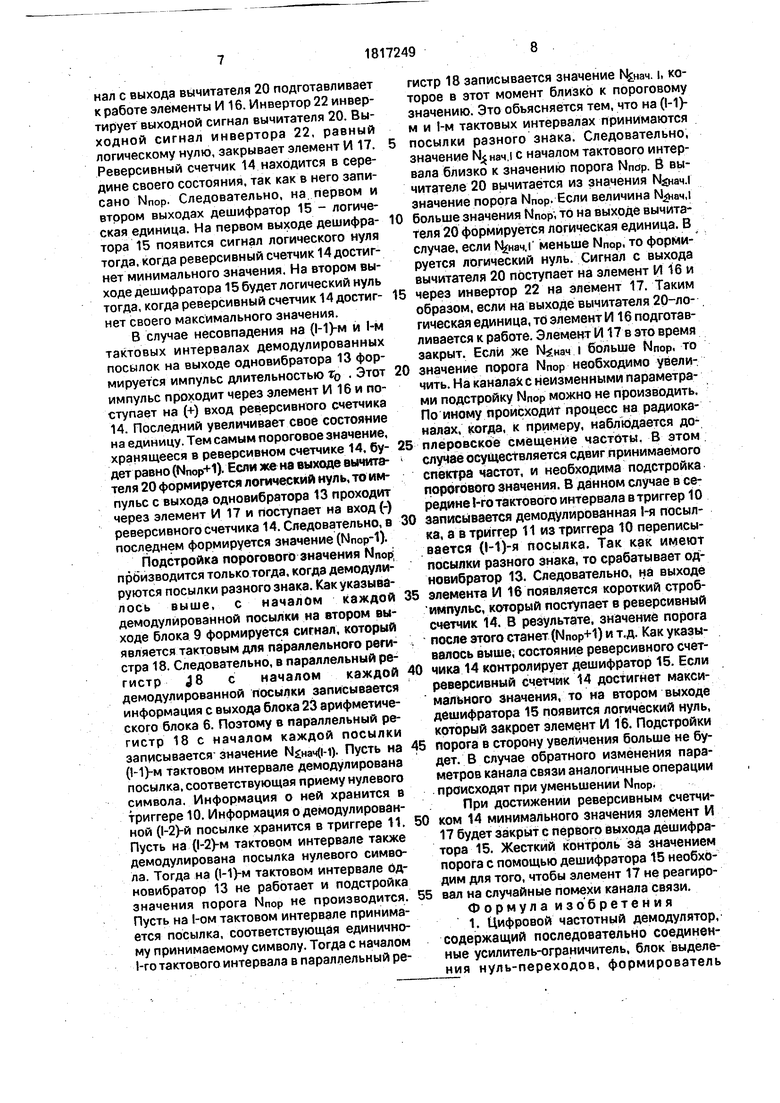

На фиг. 1 изображена структурная электрическая схема предложенного демодулятора,- на фиг. 2 - схема формирователя цифрового сигнала.

Цифровой частотный демодулятор содержит усилитель-ограничитель 1, блок 2 выделения нуль-переходов, формирователь 3 тактовых импульсов, формирователь 4 цифрового сигнала, блок 5 памяти, арифметический блок 6, выходной триггер 7, распределитель 8 импульсов, блок 9 фазовой автоподстройки частоты, первый, второй триггеры 10,11, сумматор 12 по модулю два, одновибратор 13, реверсивный счетчик 14, дешифратор 15, третий, второй элементы И 16, 17, параллельный регистр 18, первый элемент И 19, вычитатель20, коммутатор 21, инвертор 22.

Арифметический блок б содержит блок 23 буферной памяти, сумматор 24 и вычита- тель25.

Формирователь цифрового сигнала содержит измерительный счетчик 26 и блок 27 буферной памяти.

Цифровой частотный демодулятор работает следующим образом.

Сразу после включения питания обнуляются блок 5, параллельный регистр 18, блок 23, а реверсивный счетчик 14 записывает по параллельным входам значение начального порога Nnop. Перечисленные операции производятся по установочным входам R и С.

После приведения устройства в исходное состояние начинается прием частотно- модулированных сигналов. Процесс приема можно разбить на три одновременно протекающих процесса.

Первый из них - прием сигнала с входа канала связи и преобразование его в форму, удобную для дальнейшей обработки. Эту операцию производят усилитель-ограничие

00

го |ь ю

тель 1. блок 2, формирователь 4 и формирователь 3.

Второй процесс-процесс демодуляции принимаемого сигнала. Эту операцию осуществляют блок 5, коммутатор 21, арифметический блок 6, выходной триггер 7, формирователь 3 и распределитель 8.

Наконец, третий процесс-процесс подстройки порогового значения МПор под изменяющиеся параметры канала связи. Эту операцию осуществляют блок 9, триггеры 10,11, блок 12, одновибратор 13, инвертор 22, элементы И16,17,19, реверсивный счетчик 14, дешифратор 15, параллельный регистр 18 и вычитатель 20.

Указанные процессы происходят следующим образом. На вход усилителя-ограничителя 1 поступает случайный ЧМ-сигнал. Как известно, вся передаваемая информация в ЧМ-сигнале заключена в нуль-переходах, поэтому основным элементом подобных систем является усиление-ограничение. Усиленный и ограниченный ЧМ- сигнал далее поступает в блок 2. Этот блок формирует короткий строб-импульс при каждом пересечении входного сигнала нулевого значения. Короткие строб-импульсы с выхода блока 2 далее поступают на формирователь 4 цифрового сигнала. Задача формирователя 4 цифрового сигнала - преобразователь длительность полупериодов ЧМ-сигнала в соответствующие двоичные числа. С помощью такого преобразования осуществляется однозначное соответствие значения сигнала приема значению этих двоичных чисел. Итак, при приходе очередного 1-го строб-импульса с выхода блока 2 измерительный счетчик 26 обнуляется, з его содержимое одновременно записывается в блок 27. Следовательно, с приходом 1-го строб-импульса в блоке 27 будет храниться кодовая двоичная комбинация, однозначно ; соответствующая длине полупериода между ( и 1-м строб-импульсами. С приходом (1+1)-го строб-импульса в блоке 27 будет храниться длительность полупериода между -м и (1-Н)-м строб-импульсами и т.д. Для выполнения такой операции на тактовый вход измерительного счетчика 26 поступают тактовые импульсы с выхода формирователя 3, а вход сброса R счетчика и тактовый вход С блока 27 объединены, и на них поступают короткие строб-импульсы.

Второй процесс-демодуляция принимаемого сигнала. Пусть в первый момент времени с выхода формирователя 4 поступает двоичная комбинация, обозначенная чоез N1. Сигнал N1 одновременно поступает на вход блока 5 и второй вход коммутатора 21. Блок 5 представляет собой

регистровое запоминающее устройство. Так, при поступлении тактового импульса to с выхода распределителя 9 на тактовый вход блока 5 все содержимое данного блока сдвигается на один шаг в сторону выходных шин. Эта операция повторяется каждый раз, когда приходит тактовый импульс на блок 5. Отсчеты чисел NI записываются в блок 5 таким образом, чтобы в нем всегда хранилось М текущих значений частоты (числа NI).

Значение to и М выбираются из соотношения

to-B A ,(1)

-

..1

М-to-g(2)

где В - скорость передачи, бит/с;

А - допустимая величина краевых искажений.

Из соотношения (2) следует, что в блоке 5 хранятся текущие отсчеты значений частоты, взятые на временном интервале, равном длительности единичного элемента.

Как указывалось выше, в первый момент времени блок 5 обнулен, на выходе формирователя 4 появилась двоичная цифровая комбинация N1, характеризующая принимаемый сигнал. Тогда на выходе блока 5 появится сигнал N1 спустя М тактовых

1 интервалов частоты .

to

. Коммутатор 21 по команде с выхода распределителя 8 поочередно опрашивает состояние входа и выхода блока 5. В первый

момент времени коммутатор 21 подключает вход блока 5; как указывалось выше, на нем была двоичная комбинация N1. Данная двоичная комбинация N1, пройдя коммутатор 21, поступает на вход сумматора 24. Сумматор 24 совместно с блоком 23 представляет накапливающий сумматор. Так как первоначально и блок 23 был обнулен, то на выходе сумматора 24 имеют сигнал вида

Nti- Ni + O-Ni..

Сигнал N1 записывается в блок 23. В следующий момент времени коммутатор 21 осуществляет опрос выхода блока 5. В данный момент времени на выходе блока

5 будет нуль. Этот сигнал поступает также на вход сумматора 24. Как указывалось выше, после первой половины цикла расчета в блоке 23 хранится сигнал N1, который поступает на второй вход сумматора 24. Следовательно, на выходе сумматора 24 сигнал N1 останется без изменения и вновь перепишется в блок 23. После второго тактового периода to, подаваемого на блок 5, в блоке 23 будет храниться сигнал, равный N1 + N2.

Аналогичные операции осуществляются М раз до заполнения блока 5.

Таким образом, в блоке 23 будет храниться сигнал, равный (на j-м тактовом интервале)

м

N5j X(NJ)l.(3)

I - I

Для расчета М4 на очередном (J + 1)-м тактовом интервале необходимо ввести новое значение NJ+I и вычесть предыдущее значение Nj-м. Эту операцию осуществляет коммутатор 21 совместно с блоком 5.

Итак, на очередном 0+1)-м тактовом интервале to (в первой его половине) на выходе формирователя 4 будет двоичная комбинация, равная Nj+1, Этот сигнал поступает на вход сумматора 24. На выходе сумматора 24 будет сигнал, равный

NarVfl-Nfl + Nj+1.(4)

После этого сигнал N/Q+I) записывается в блок 23 по сигналу с выхода распределителя 8. В.следующей половине тактового сигнала to коммутатор 21 подключает выход блока 5 к входу сумматора 24. Используется инверсный выход блока 5. Следовательно, на выходе блока 5 будет сигнал, равный (-Nj-м).

На выходе сумматора 24 имеют сигнал, равный ,

%i+i) N a+iJ-Nj-M.(5)

Следовательно, расчет очередного ) значения сигнала осуществляется в два этапа. На первом этапе вводится новое значение сигнала Nj-и. На втором этапе вычитается старое значение сигнала NJ-М. Результат суммирования в обоих случаях записывается в блок 23.

Сигнал NЈ -t далее поступает в вычита- тель 25, где прЪизводится вычитание порогового значения Nnop, подаваемого с выхода реверсивного счетчика 14. Как указывалось выше, первоначально при включении в реверсивный счетчик 14 записывается пороговое значение Nnop. определяемое соотношением

N(iep-.M.,(6)

Здесь Nft, Nf2 - двоичные числа на выходе формирователя 4 при приеме соответственно первой характеристической частоты fi и второй характеристической частоты f2.

Знаковый разряд с выхода вы читателя 25 записывается в выходной триггер 7. Итак, если значение больше значения Nnop, то на выходе вычитателя 25 - логическая единица. В противном случае на выходе вычитателя 25 - логический нуль.

На этом процесс демодуляции заканчивается.

Подстройка значения Nnop под изменяющиеся параметры канала связи необходи- 5 ма, например, при работе по. радиоканалу. При этом сигнал с выхода выходного триггера 7 поступает к получателю сообщений и одновременно в блок 9.

На выходе блока 9 формируются две синх10 ропоследовательности. Частота и фаза первой из них соответствует усредненному фазовому положению середины посылок принимаемого сигнала. Сигнал блока 9 с этого выхода одновременно тактирует триггеры 10,11.

15 Вторая синхропоследовательность формируется на втором выходе блока 9. Данный сигнал соответствует усредненному значению начала принимаемых посылок и тактирует параллельный регистр 18.

0 Так как на первом выходе блока 9 синхросигнал соответствует середине принимаемых посылок, то в триггерах 10, 11 записываются демодулировэнные сигналы. При этом, если в триггере 10 хранится демо5 дулированная посылка на 1-м тактовом интервале, то в триггере 11 хранится (1-1)-я демодулированная посылка. Значение 1-й и (И)-й посылок складываются по модулю два в сумматоре 12. Если эти посылки одного

0 знака (либо 00, либо 11), то на выходе сумматора 12 появляется сигнал логического нуля. Если же посылки на l-м и (М)-м интервалах разного знака, то на выходе сумматора 12-логическая единица.

5 Выходной сигнал сумматора 12 сканируется синхропоследовательностью с пер- вого выхода блока 9. Так, если в середине демодулированных посылок на выходе сумматора 12 появляется логическая единица,

0 то происходит совпадение сигналов в элементе И 19 и на его выходе формируется логическая единица. От переднего фронта этого сигнала срабатывает одновибратор 13, формируя на своем выходе строб-им5 пульс длительностью г0 . Сигнал с выхода одновибратора 13 одновременно поступает на элементы И 16, 17. Данные элементы И либо оба закрыты, либо открыт один из них. Режимом работы этих элементов управляют

0 инвертор 22 и дешифратор 15.

Элементами 16,17управляетдешифра- тор 15. Как указано выше, при первоначальной установке в реверсивный счетчик 14 было записано значение Nnop, предвари5 тельно рассчитанное по формуле (6). Вычи- татель 20 на своем выходе формирует либо значение логического нуля, либо значение логической единицы. Пусть на выходе вычитателя 20 -логическая единица. Тогда сигнал с выхода вычитателя 20 подготавливает к работе элементы И 16. Инвертор 22 инвертирует выходной сигнал вычитателя 20. Выходной сигнал инвертора 22, равный логическому нулю, закрывает элемент И 17. Реверсивный счетчик 14 находится в середине своего состояния, так как в него записано Nnop. Следовательно, на. первом и втором выходах дешифратор 15 - логическая единица. На первом выходе дешифратора 15 появится сигнал логического нуля тогда, когда реверсивный счетчик 14 достигнет минимального значения. На втором выходе дешифратора 15 будет логический нуль тогда, когда реверсивный счетчик 14 достигнет своего максимального значения.

В случае несовпадения на (М)-м и 1-м тактовых интервалах демодулированных посылок на выходе одновибратора 13 формируется импульс длительностью TQ . Этот импульс проходит через элемент И 16 и поступает на (+) вход реверсивного счетчика 14. Последний увеличивает свое состояние на единицу. Тем самым пороговое значение, хранящееся в реверсивном счетчике 14, будет равно (Nnop+1). Если же на выходе вычитателя 20 формируется логический нуль, то импульс с выхода одновибратора 13 проходит через элемент И 17 и поступает на вход (-) реверсивного счетчика 14. Следовательно, в последнем формируется значение (Nnop-1). Подстройка порогового значения Nnop; производится только тогда, когда демодули- руются посылки разного знака. Как указывалось выше, с началом каждой демодулйрованной посылки на втором выходе блока 9 формируется сигнал, который является тактовым для параллельного регистра 18. Следовательно, в параллельный регистр J8 с началом каждой демодулйрованной посылки записывается информация с выхода блока 23 арифметического блока 6. Поэтому в параллельный регистр 18 с началом каждой посылки записывается значение МЈНач(М). Пусть на (М)-м тактовом интервале демодулирована посылка, соответствующая приему нулевого символа. Информация о ней хранится в триггере 10. Информация о демодулйрованной (-2)-й посылке хранится в триггере 11. Пусть на (-2)-м тактовом интервале также демодулирована посылка нулевого символа. Тогда на (1-1)-м тактовом интервале од- новибратор 13 не работает и подстройка значения порога Nnop не производится. Пусть на 1-ом тактовом интервале принимается посылка, соответствующая единичному принимаемому символу. Тогда с началом 1-го тактового интервала в параллельный регистр 18 записывается значение . i, которое в этот момент близко к пороговому значению. Это объясняется тем, что на (1-1)- м и 1-м тактовых интервалах принимаются

посылки разного знака. Следовательно, значение . с началом тактового интервала близко к значению порога Nnop. В вы- читателе 20 вычитается из значения .1 значение порога Nnop. Если величина

больше значения Nnop, то на выходе вычитателя 20 формируется логическая единица. В случае, если Нач,Г меньше Nnop, то формируется логический нуль. Сигнал с выхода вычитателя 20 поступает на элемент И 16 и

через инвертор 22 на элемент 17. Таким образом, если на выходе вычитателя 20-ло- гическая единица, то элемент И16 подготавливается к работе. Элемент И17 в это время закрыт. Если же i больше Nnop, то

значение порога Nnop необходимо увеличить. На каналах с неизменными параметрами подстройку Nnop можно не производить. По иному происходит процесс на радиоканалах, когда, к примеру, наблюдается доплеровское смещение частоты, В этом случае осуществляется сдвиг принимаемого спектра частот, и необходима подстройка порогового значения. В дан ном случае в середине 1-го тактового интервала в триггер 10

записывается демодулированная 1-я посылка, а в триггер 11 из триггера 10 переписывается (1-1)-я посылка. Так как имеют посылки разного знака, то срабатывает од- новибратор 13. Следовательно, на выходе

элемента И 16 появляется короткий строб- импульс, который поступает в реверсивный счетчик 14. В результате, значение порога после этого станет (Nnop+1) и т.д. Как указывалось выше, состояние реверсивного счетчика 14 контролирует дешифратор 15. Если реверсивный счетчик 14 достигнет максимального значения, то на втором выходе дешифратора 15 появится логический нуль, который закроет элемент И 16. Подстройки

порога в сторону увеличения больше не будет. В случае обратного изменения параметров канала связи аналогичные операции происходят при уменьшении Nnop.

При достижении реверсивным счетчиком 14 минимального значения элемент И 17 будет закрыт с первого выхода дешифратора 15. Жесткий контроль за значением порога с помощью дешифратора 15 необходим для того, чтобы элемент 17 не реагировал на случайные помехи канала Связи. Формула изобретения 1. Цифровой частотный демодулятор, содержащий последовательно соединенные усилитель-ограничитель, блок выделе ния нуль-переходов, формирователь

цифрового сигнала и блок памяти, арифметический блок, выход которого соединен с первым входом выходного триггера, формирователь тактовых импульсов, первый выход которого соединен с входом распределителя импульсов, первый, второй и третий выходы которого соединены соответственно с вторым входом блока памяти, первым входом арифметического блока и вторым входом выходного триггера, второй и третий выходы формирователя тактовых импульсов соединены с вторыми входами блока выделения нуль- переходов и формирователя цифрового сигнала, отличающийся тем, что, с целью повышения помехоустойчивости, введены последовательно соединенные блок фазовой автоподстройки частоты, первый триггер, второй триггер, сумматор по модулю два, первый элемент И, одновибратор, второй элемент И, реверсивный счетчик, дешифратор и третий элемент И, последовательно соединенные параллельный регистр, вычитатель и инвертор, а также коммутатор, первый и второй входы которого соединены соответственно с выходами формирователя цифрового сигнала и блока памяти, четвертый выход распределителя импульсов соединен с третьим входом коммутатора, выход которого соединен с вторым входом арифметического блока, третий вход которого и второй вход вычитателя соединены с выходом реверсивного счетчика, второй выход

арифметического блока соединен с первым входом параллельного регистра, второй вход которого соединен с вторым выходом блока фазовой автоподстройки частоты,

вход которого соединен с выходом выходного триггера, подключенным также к второму входу первого триггера, выход которого соединен с вторым входом сумматора по модулю два, выход одновибратора соединен с

вторым входом третьего элемента И, третий вход которого соединён с выходом вычитателя, второй выход дешифратора соединен с вторым входом второго элемента И, третий вход которого соединен с выходом инвертрра, первый выход блока автоподстройки частот соединен С вторыми входами второго триггера и первого элемента И, выход третьего элемента И соединен с вторым входом реверсивного счетчика.

2. Демодулятор по п. 1, отличающийся тем, что арифметический блок содержит последовательно соединенные сумматор, блок буферной памяти и вычитатель, выход

блока буферной памяти соединен с вторым входом сумматора, причем вход сумматора, второй вход блока буферной памяти и второй вход вычитателя являются соответственно вторым, первым и третьим входами арифметического блока, первым и вторым выходами которого являются выход вычитателя и выход блока буферной памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ измерения мгновенных значений частоты электрического сигнала и устройство для его осуществления | 1987 |

|

SU1503022A1 |

| Умножитель частоты | 1988 |

|

SU1608779A1 |

| Устройство для измерения ритма сердца | 1985 |

|

SU1284512A1 |

| Устройство для передачи сигналов приращений | 1981 |

|

SU955162A1 |

| Многоканальное устройство для обработки информации датчиков с частотным выходом | 1984 |

|

SU1196892A1 |

| Устройство для передачи сигналов приращений | 1981 |

|

SU955163A1 |

| Адаптивный цифровой корректор | 1979 |

|

SU794734A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Телевизионный пеленгатор | 1989 |

|

SU1670805A1 |

Сущность изобретения: цифровой частотный демодулятор содержит 1 усилитель- ограничитель (1), 1 блок выделений нуль переходов (2), 1 формирователь тактовых импульсов (3), 1 формирователь цифрового сигнала (4), 1 блок памяти (5), 1 арифметический блок (6), 1 выходной триггер (7), 1 распределитель импульсов (8), 1 блок фазовой автоподстройки частоты (9), 2 триггера (10, 11), 1 сумматор по модулю два (12), одновиб- ратор (13), 1 реверсивный счетчик (14), 1 дешифратор (15), 3 элемента И (16,17,19), 1 параллельный регистр (18), 1 вычитатель(20)/ 1 Коммутатор (21), 1 инвертор (22). 1-2 4-5 21-6-7-9-18-20-16-14-15-17-14-6,3-2,3-4- 21, 3-8-5, 8-21, 8-6, 8-7, 6-18, 9-10-11-12-19-13-17,13-16,22-17,15-16, 9-11,9-19, 10-12.2 ил.

Фив.1

Фиг2

| Цифровой частотный демодулятор | 1981 |

|

SU1030991A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1993-05-23—Публикация

1991-06-26—Подача