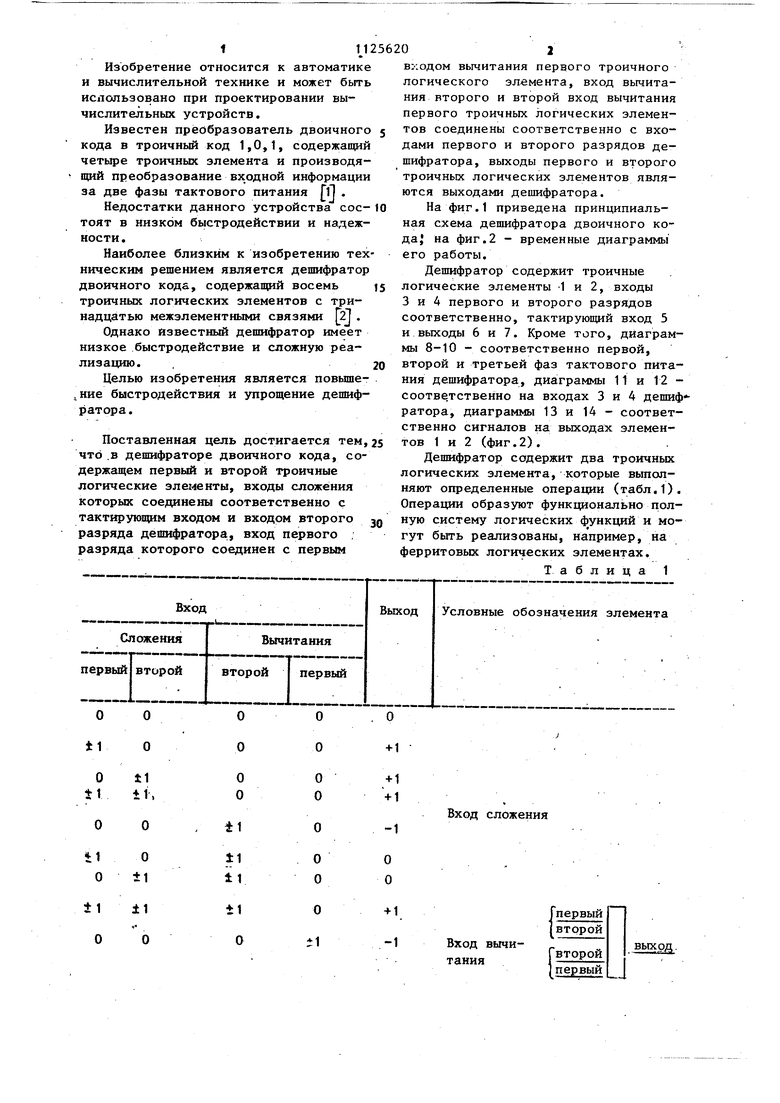

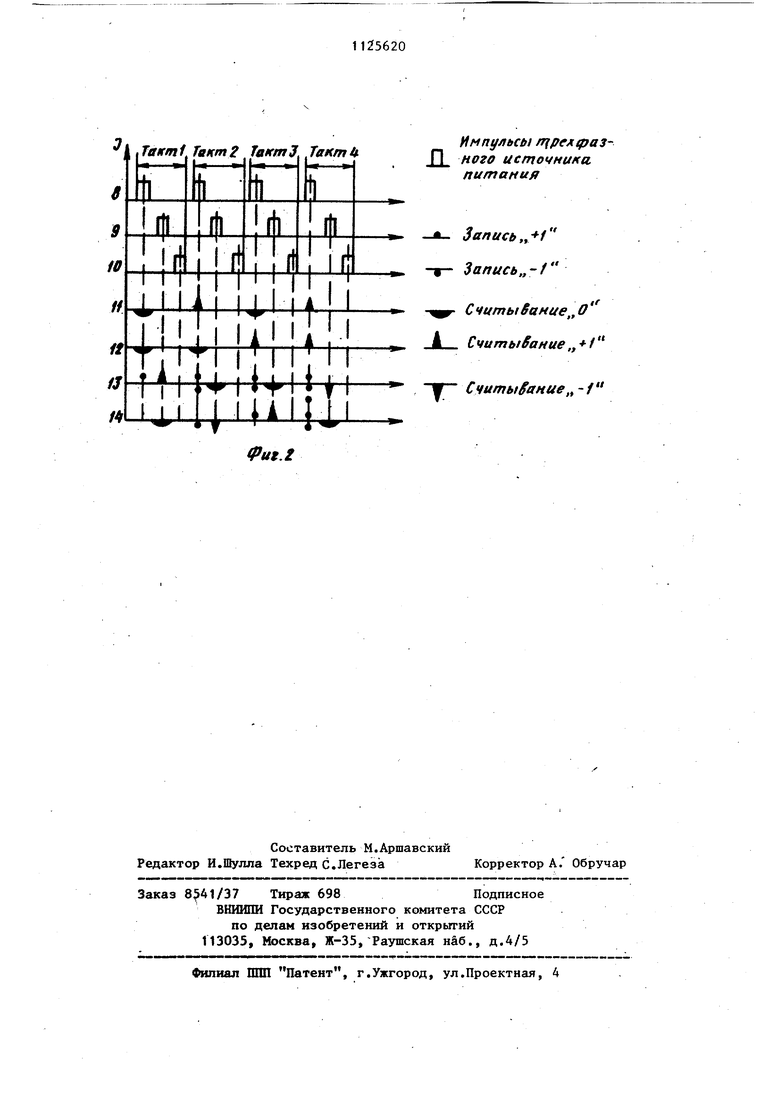

Фиг.1 Изобретение относится к автоматике и вычислительной технике и может быть ислользовано при проектировании вычислительных устройств. Известен преобразователь двоичного кода в троичный код 1,0,1, содержащий четыре троичных элемента и производящий преобразование вх одной информации за две фазы тактового питания ГЛ . Недостатки данного устройства соетоят в низком быстродействии и надежности. Наиболее близким к изобретению тех ническим решением является дешифратор двоичного кода, содержащий восемь троичных логических элементов с тринадцатью межэлементными связями 2 . Однако известный дешифратор имеет низкое быстродействие и сложную реализацию. . Целью изобретения является повыше,ние быстродействия и упрощение дешифратора. Поставленная цель достигается тем, что ,в дешифраторе двоичного кода, содержащем первый и второй троичные логические элементы, входы сложения которых соединены соответственно с тактирующим входом и входом второго разряда дешифратора, вход первого . разряда которого соединен с первым 11 02 входом вычитания пердого троичного логического элемента, вход вычитания второго и второй вход вычитания первого троичных логических элементов соединены соответственно с входами первого и второго разрядов дешифратора, выходы первого и второго троичных логических элементов являются выходами дешифратора. На фиг.1 приведена принципиальная схема дешифратора двоичного кода; На фиг.2 - временные диаграммы его работы. Дешифратор содержит троичные логические элементы и 2, входы 3 и 4 первого и второго разрядов соответственно, тактирующий вход 5 и выходы 6 и 7. Кроме того, диаграммы 8-10 - соответственно первой, второй и третьей фаз тактового питания дешифратора, диаграммы 11 и 12соответственно на входах 3 и 4 дешиф ратора, диаграммы 13 и 14 - соответственно сигналов на выходах элементов 1 и 2 (фиг.2). Депмфратор содержит два троичных логических элемента, которые выполняют определенные операции (табл.1). Операции образуют функционально полную систему логических функций и могут быть реализованы, например, на ферритовых логических элементах. Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь троично-десятичного кода в код семисегментного индикатора | 1982 |

|

SU1092488A1 |

| Дешифратор | 1983 |

|

SU1119167A1 |

| Преобразователь двоичного кода в троичный код 1,О,1 | 1985 |

|

SU1343552A1 |

| Дешифратор троичного кода 1,0,1 | 1983 |

|

SU1106015A1 |

| Преобразователь двоично-десятичного кода в код семисегментного индикатора | 1980 |

|

SU898416A1 |

| Преобразователь двоичного кодаВ ТРОичНый КОд 1,0,1 | 1979 |

|

SU796838A1 |

| Преобразователь троично-десятичного кода в код восьмисегментного индикатора | 1983 |

|

SU1107117A1 |

| Дешифратор | 1986 |

|

SU1361724A1 |

| Дешифратор | 1978 |

|

SU728123A1 |

| Преобразователь двоичного кода в троичный код 1,0,1 | 1978 |

|

SU750477A1 |

ДЕШИФРАТОР ДВОИЧНОГО КОДА, . содержащий первый и второй троичные логические элементы, входы сложения которых соединены соответственно с тактирующим входом и входом второго разряда дешифратора, вход первого разряда которого соединен с первым входом вычитания первого троичного логического элемента, отличающийся тем, что, с целью повышения его быстродействия, вход вычитания второго и второй вход вычитания первого троичных логических алиментов соединены соответственно с входами первого и второго разрядов дешифратора, выходы первого и второго троичных логических элементов являются выходами дешифратора.

О

±1

О ±1

11

О О ±1

±1

±1 О

О i1

о

о

Вход сложения

Гпервый (второй

Вход вычиГвторойтания

1 пер вый Система тактового питания дешифратора трехфазная, при этоМ входная комбинация сигналов на входах 3 и 4 . поступает через три фазы Ходим такт) передачи информации. Тактовым импульсом второй фазы считывается информация с элементов 1 и 2. Импульсы поступают на входы во время тактового импульса первой фазы, на вход 5 поступают .импульсы положительные или отрицательные.с тактовой частотой. На входы 3 и 4 дешифратора подаются кодовые комбинации в Двоичном коде (по входу 3 с весом 2, по входу 4 с весом 2 ), при этом на одном из выходов 6 или 7 дешифратора (на выходах элементов 1 и 2) появляется сигнал положительной или отрицательной полярности, однозначно -соответствующий входной комбинации сигналов. При подаче двоичного кода на входы 3 и 4 1 представляется сигналом положительной или отрицательной полярности а О - отсутствием сигнала. Двухзначная информация с входов 3 и 4 преобразуется в трехзначную информацию на выходах 6 и 7 (табл.2). Таблица 2 Полярность сигнаКодовая комбинация сигналов лов на выходах на входах

Продолжение табл.1 Продолжение табл.2 .Кодовая комПолярность сигнаринация сигналов лов на выходах на входах функционирование дешифратора в соответствии с входной кодовой комбинацией (00) осуществляется следующим образом (фиг. 1 и 2) . Тактовьм импульсом первой фазы первого такта согласно логике работы элемента (табл.1) по тактирующему входу 5 записьшается +1 на вход сложения элемента 1, импульсом второй фазы положительный сигнал с выхода элемента 1 (выход 6) поступает на выход депшфратора, образуя сигнал, соответствующий входной комбинации (00). Аналогично происходит преобразование последующих входных кодовых комбинаций (табл.2). Использование предлагаемого преобразователя обеспечивает по сравнению с известным, повышение быстродействия в три раза, поскольку преобразование сигналов происходит за одну фазу тактового питания, а в известном - за три фазы, упрощение и повьппение надежности за счет сокращения оборудования на шесть элементов.

мпульс1 1 щрелфазП ного источника питания

Запись, Запись,,-/

Считывание,, О Считывание „ /

Считы ание, 1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Преобразователь двоичного кодаВ ТРОичНый КОд 1,0,1 | 1979 |

|

SU796838A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Соколов Т.Н | |||

| и др | |||

| Ферритовые логические элементы и узлы информационных систем, ЛВИКА им.А.Ф.Можайского, Л., 1970, с | |||

| Вагонетка для движения по одной колее в обоих направлениях | 1920 |

|

SU179A1 |

Авторы

Даты

1984-11-23—Публикация

1983-08-09—Подача