(54) ЦИФРОВОЙ РЕЗОНАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой нерекурсивный фильтр | 1985 |

|

SU1270876A1 |

| Цифровой нерекурсивный фильтр | 1986 |

|

SU1350826A2 |

| Цифровой перестраиваемый полосовой фильтр | 1982 |

|

SU1166274A1 |

| Цифровой полосовой фильтр с конечной длительностью весовой функции | 1977 |

|

SU674033A1 |

| Цифровой анализатор спектра | 1985 |

|

SU1256044A1 |

| Цифровой синтезатор синусоидально- косинусоидальных сигналов | 1977 |

|

SU734706A1 |

| Нерекурсивный цифровой фильтр нижних частот | 1982 |

|

SU1037417A1 |

| Устройство для фильтрации симметричных составляющих | 1985 |

|

SU1343362A1 |

| Устройство для цифровой фильтрации | 1981 |

|

SU957416A1 |

| Цифровой нерекурсивный фильтр | 1974 |

|

SU516043A1 |

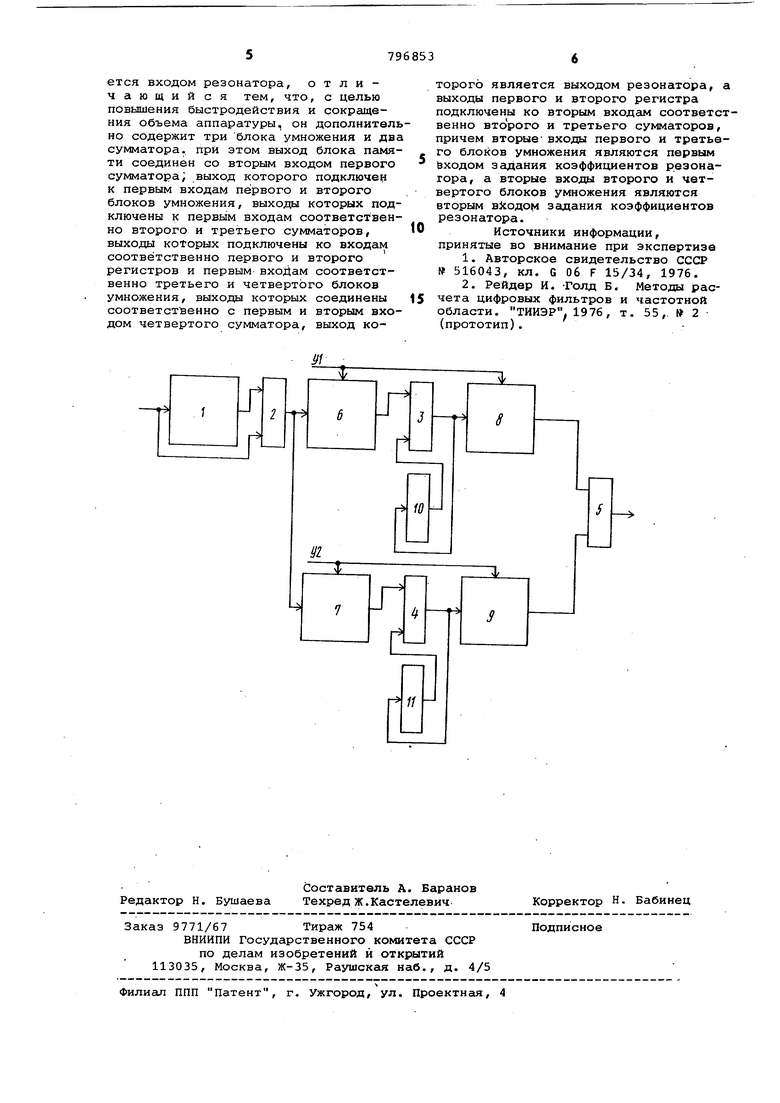

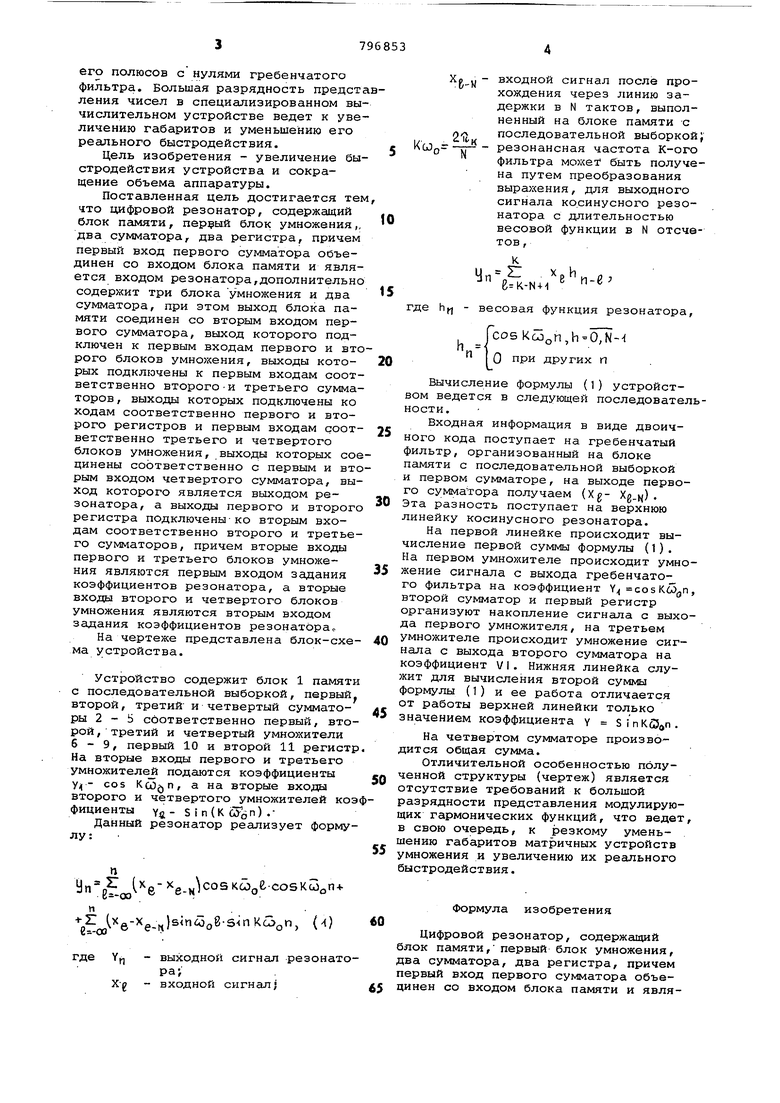

Изобретение относится к специализированным средствам вычислительной техники, применяемьлм в системах обработки радиолокационных, акустических и гидроакустических сигналов, и может быть использовано для построения методом частотной выборки различных цифровых фильтров. Известен полосовой цифровой фильт который выполняет операцию свертки отсчетов входного сигнала и соответствующих им весовых коэффИ1щентов. Весовые коэффициенты находятся по известной комплексной частотной хара теристике и хранятся в памяти {jQ Недостаток этого устройства - бол шое число арифметических опергщий на период квантования входного сигна ла, определяемое длительностью весовой функции. Наиболее близким к предлагаемому является резонатор с ограниченной им пульсной характеристикой. Он содержит блок памяти с последовательной выборкой, одно устройство умножения, два суд1матора, три (регистра и вентиль, причем.вход устройства сое динен со входрм блока памяти и со вторым входом первого сумматора, вы ход памяти соединен с первым входом первого сумматора, выход которого соединен со вторым входом вентиля и входом первого регистра, выход которого соединен со вторым входом вентиля и входом первого регистра, выход которого соединен со вторым входом второго сумматора, выход которого соединен с первым входом умножителя, на второй вход которсэго подается коэффициент ,-лт , выход умножителя соединен с первым входом вентиля, выход которого подается на первый вход третьего сумматора, выход которого является информационным выходом устройства, а также подается на вход третьего регистра, выход которого соединен с первым входом второго сумматора и входом второго регистра, вход которого соединен со вторым входом третьего сумматора рД. Основным недостатком резонатора с такой структурой является требование большой разрядности представления его коэффициентов, не менее 25 разрядов, которые диктуются необходимостью достаточно точного совмеп;енмя его полюсов с нулями гребенчатого фильтра. Большая разрядность предста ления чисел в специализированном вычислительном устройстве ведет к увеличению габаритов и уменьшению его реального быстродействия. Цель изобретения - увеличение быстродействия устройства и сокращение объема аппаратуры. Поставленная цель достигается тем что цифровой резонатор, содержащий блок паиуити, первый блок умножения,, два сумматора, два регистра, причем первый вход первого сумматора объединен со входом блока памяти и является входом резонатора,дополнительно содержит три блока умножения и два сумматора, при этом выход блока памяти соединен со вторым входом первого сумматора, выход которого подключен к первым входам первого и вто рого блоков умножения, выходы которых подключены к первым входам соответственно второгои третьего сумматоров , выходы которых подключены ко ходам соответственно первого и второго регистров и первым входам соответственно третьего и четвертого блоков умножения, выходы которых сое динены соответственно с первым и вто рым входом четвертого сумматора, выход которого является выходом резонатора, а выходы первого и второго регистра подключеныко вторым входам соответственно второго и третьего сумматоров, причем вторые входы первого и третьего блоков умножения являются первым входом задания коэффициентов резонатора, а вторые входы второго и четвертого блоков умножения являются вторым входом задания коэффициентов резонатора На чертеже представлена блок-схе ма устройства. Устройство содержит блок 1 памяти с последовательной выборкой, первый второй, третий и четвертый сумматоры 2-5 соответственно первый, второй, третий и четвертый умножители 6-9, первый 10 и второй 11 регистр На вторые входы первого и третьего умножителе й подаются коэффициенты cos , а на вторые входы второго и четвертого умножителей коэ фициенты YU- S in(K сУ ЬДанный резонатор реализует формулу:у„ ZT (Xg-Xg JcOSK60oe.-COSKcOon-. (Xg-Xg)s n Oo8-S nKcbQn, (л) где Yf - выходной сигнал резонато ра; x-g - входной сигнал; входной сигнал после прохождения через линию задержки в N тактов, выполненный на блоке памяти с последовательной выборкой; KtJo--irрезонансная частота К-ого фильтра может быть получена путем преобразования выражения, для выходного сигнала косинусного резонатора с длительностью весовой функции в N отсчетов. eFK-N / - где hf - весовая функция резонатора. Jcos KcOon,h0,N-( О при других л Вычисление формулы (1) устройством ведется в следующей последовательности. Входная информация в виде двоичного кода поступает на гребенчатый фильтр, организованный на блоке памяти с последовательной выборкой и первом сумматоре, на выходе первого суммагора получаем (Xg- Xg.n) . Эта разность поступает на верхнюю линейку косинусного резонатора. На первой линейке происходит вычисление первой суммы формулы (1). На первом умножителе происходит умножение сигнала с выхода гребенчатого фильтра на коэффициент Y cos , второй сумматор и первый регистр организуют накопление сигнала с выхода первого умножителя, на третьем умножителе происходит умножение сигнала с выхода второго сумматора на коэффициент VI. Нижняя линейка служит для вычисления второй суммы формулы (1) и ее работа отличается от работы верхней линейки только значением коэффициента у SinKcSon. На четвертом сумматоре производится общая сумма. Отличительной особенностью полученной структуры (чертеж) является отсутствие требований к большой разрядности представления модулирующих гармонических функций, что ведет, в свою очередь, к резкому уменьшению габаритов матричных устройств умножения и увеличению их реального быстродействия. Формула изобретения Цифровой резонатор, содержащий блок памяти, первый блок умножения, два сумматора, два регистра, причем первый вход первого сумматора объединен со входом блока памяти и является входом резонатора, отличающийся тем, что, с целью повышения быстродействия и сокращения объема аппаратуры, он дополнительно содержит три блока умножения и два сумматора, прИ этом выход блока памяти соединен со вторым входом первого сумматора; выход которого подключен к первым входам первого и второго блоков умножения, выходы которых подключены к первым входам соответственно второго и третьего сумматоров, выходы которых подключены ко входам соответственно первого и второго регистров и первым вхоДам соответственно третьего и четвертого блоков умножения, выходы которых соединены соответственно с первым и вторым входом четвертого сумматора, выход которого является выходом резонатора, а выходы первого и второго регистра подключены ко вторым входам соответственно второго и третьего сумматоров, причем вторые входы первого и третьего блоков умножения являются первым бходом задания коэффициентов резонатора, а вторые входы второго и четвертого блоков умножения являются вторым вводом задания коэффициентов

резонатора.

Источники информации,

принятые во внимание при экспертизе

5 области. ТИИЭР, 1976, т. 55, № 2

(прототип).

Авторы

Даты

1981-01-15—Публикация

1979-02-19—Подача