1П

Изобретение относится к электроизмерительной технике и может быть использовано также в релейной защите электроустановок от повреждений.

Цель изобретения - повышение точности фильтрации симметричных составляющих за счет повышения помехоустойчивости устройства.

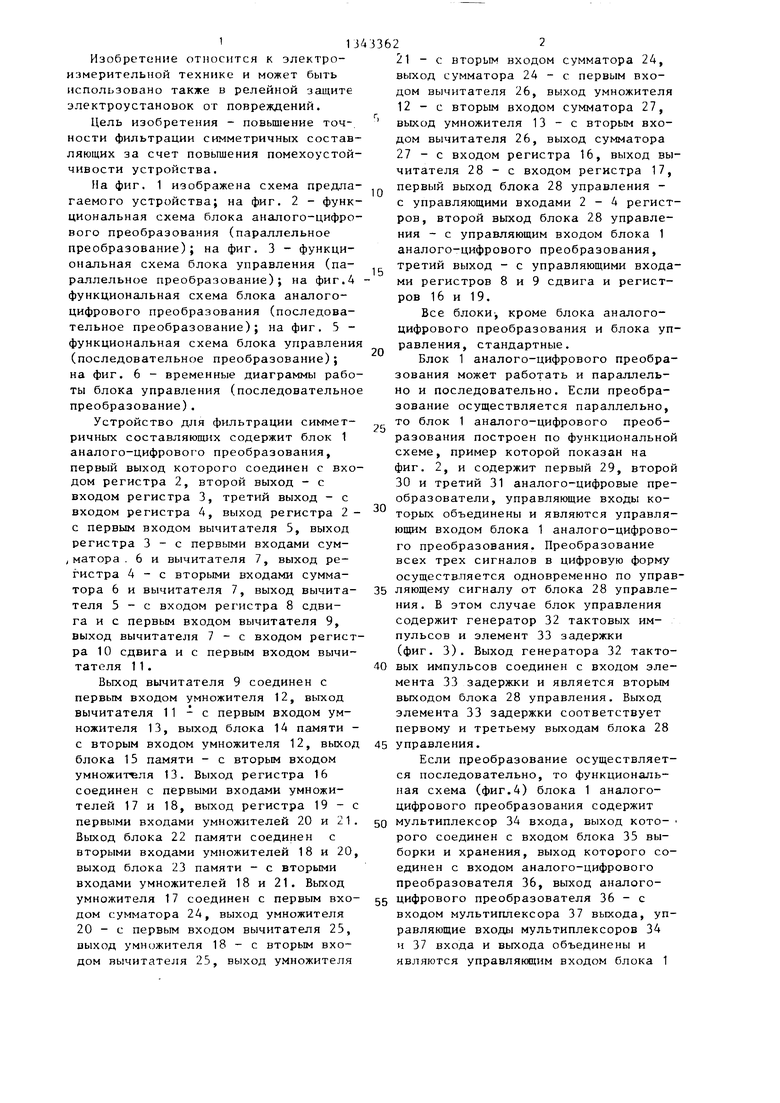

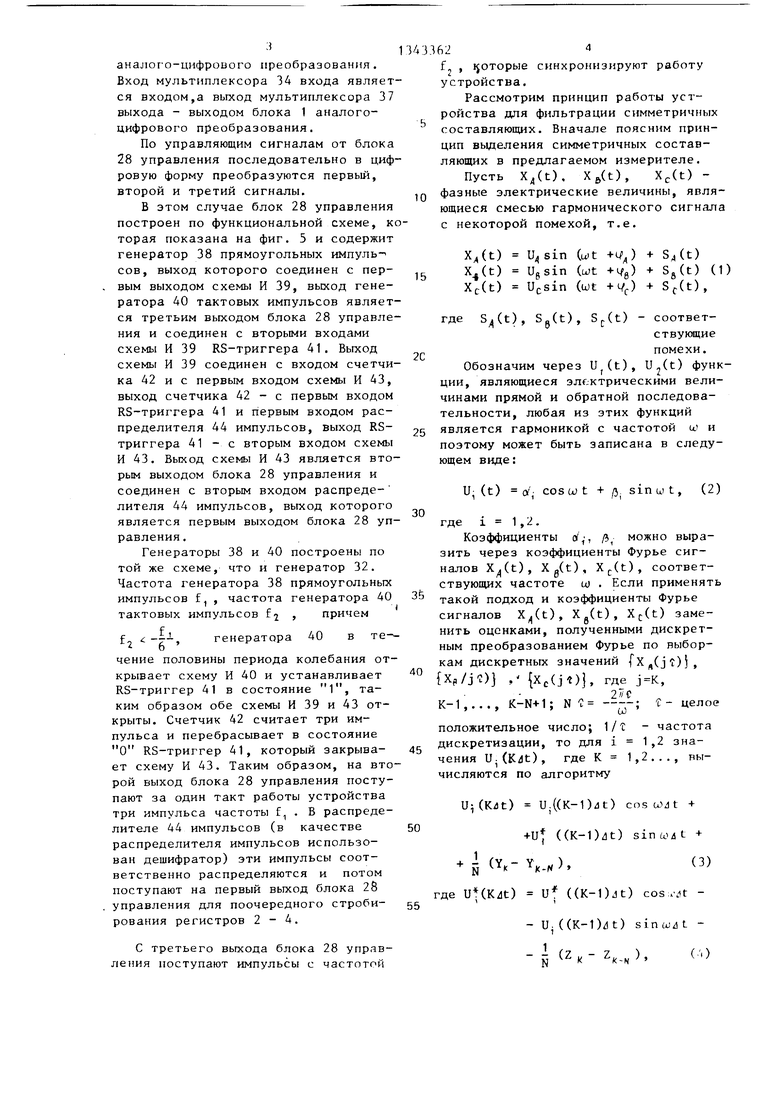

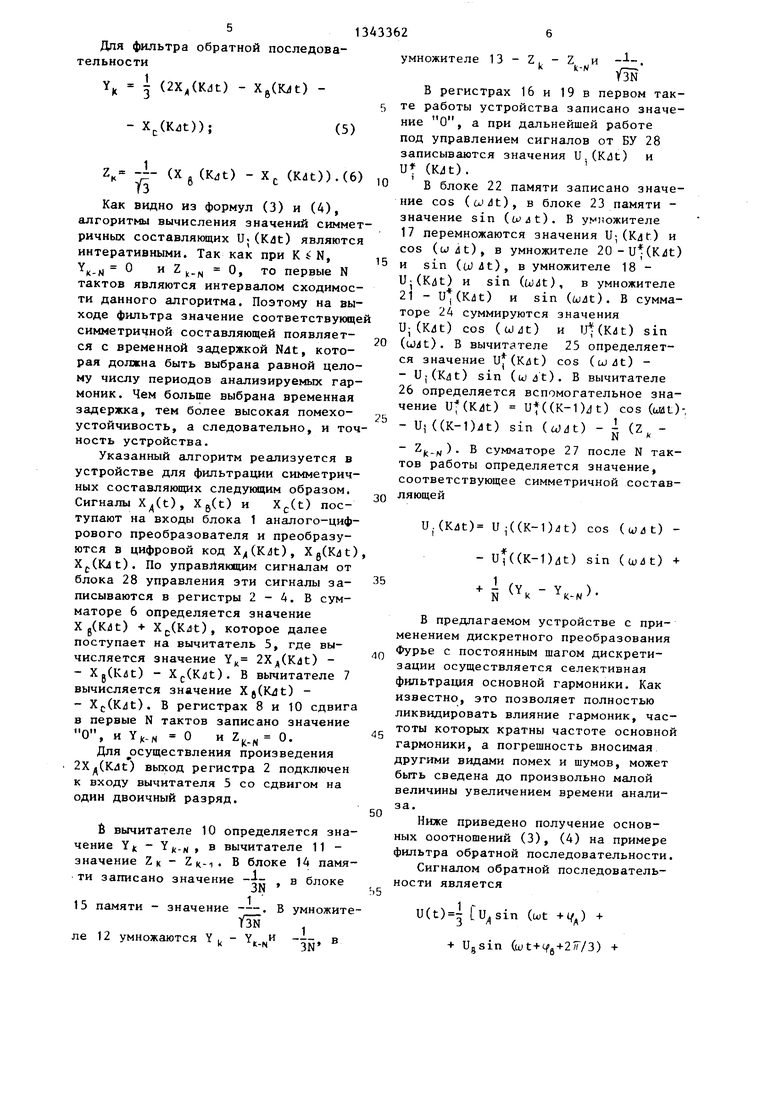

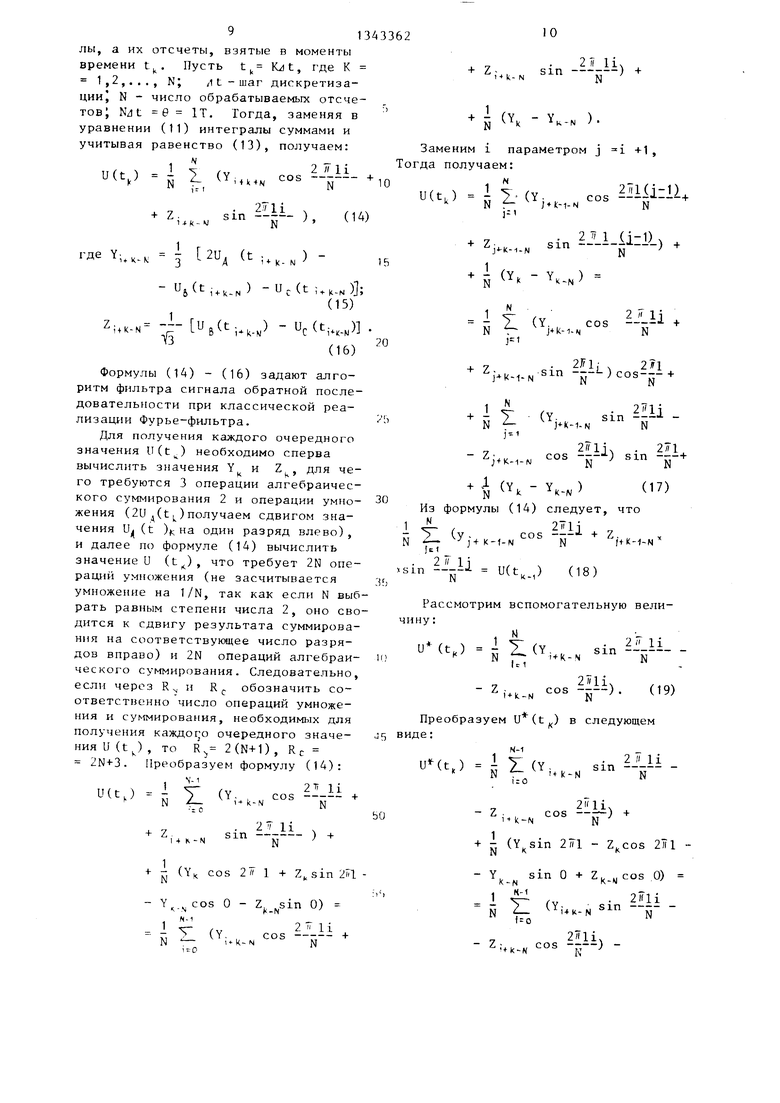

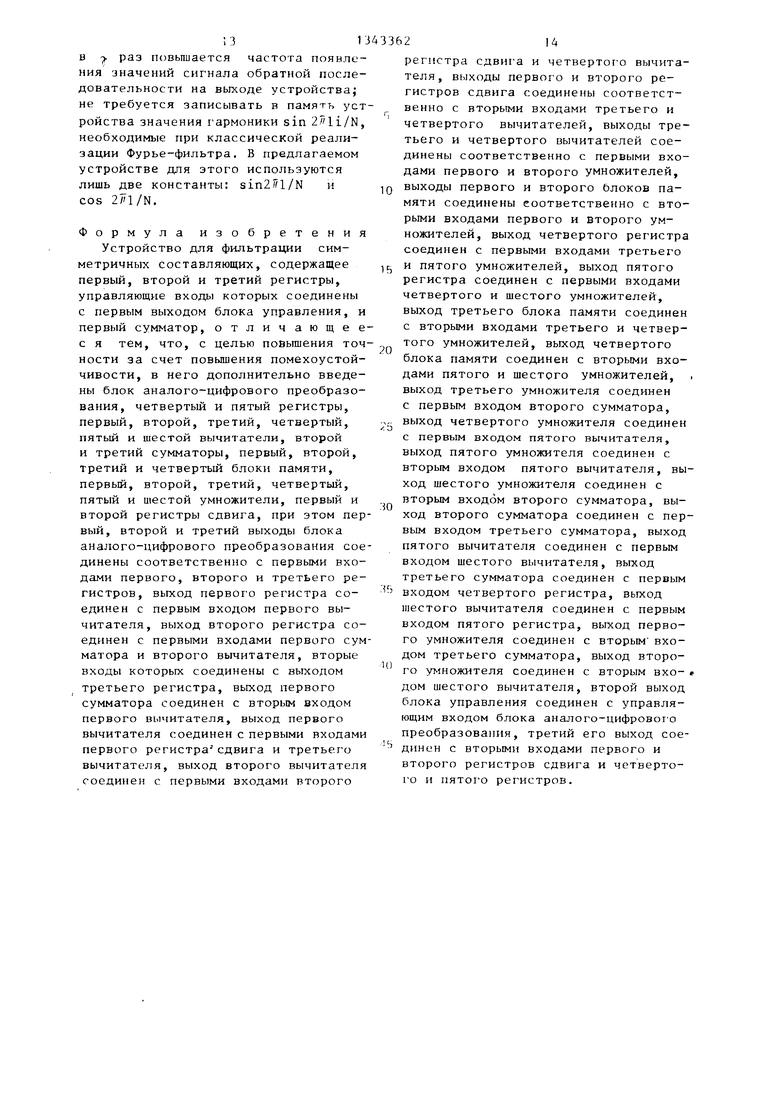

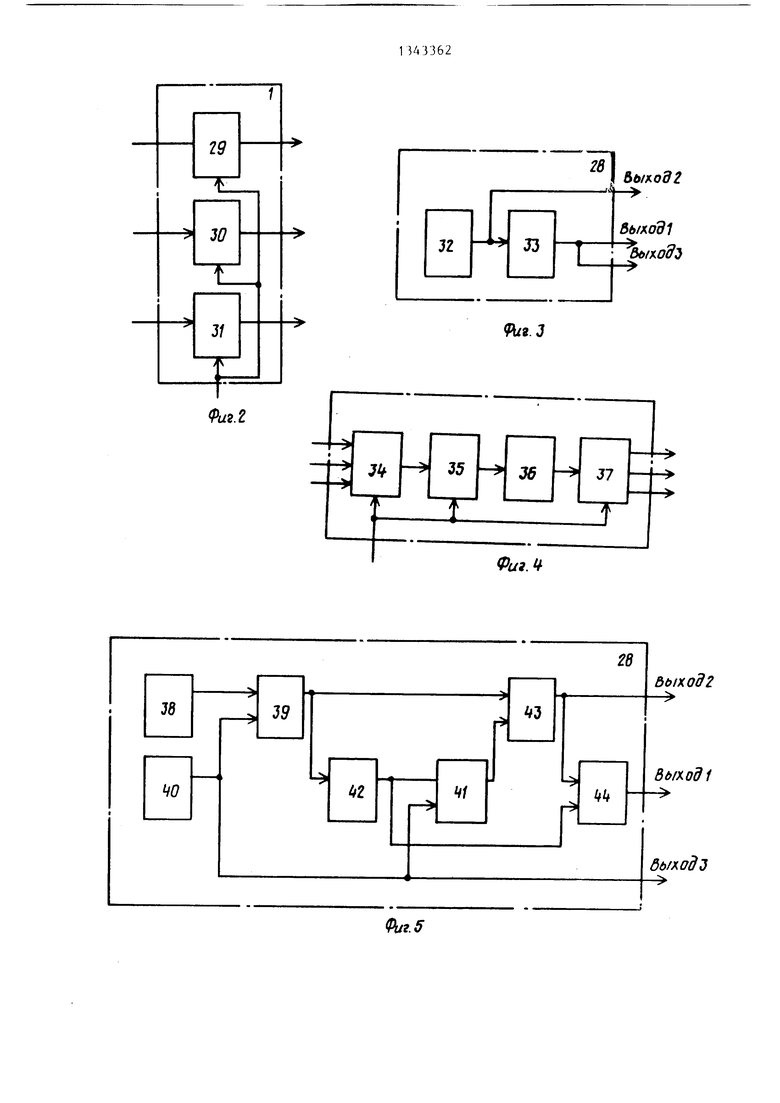

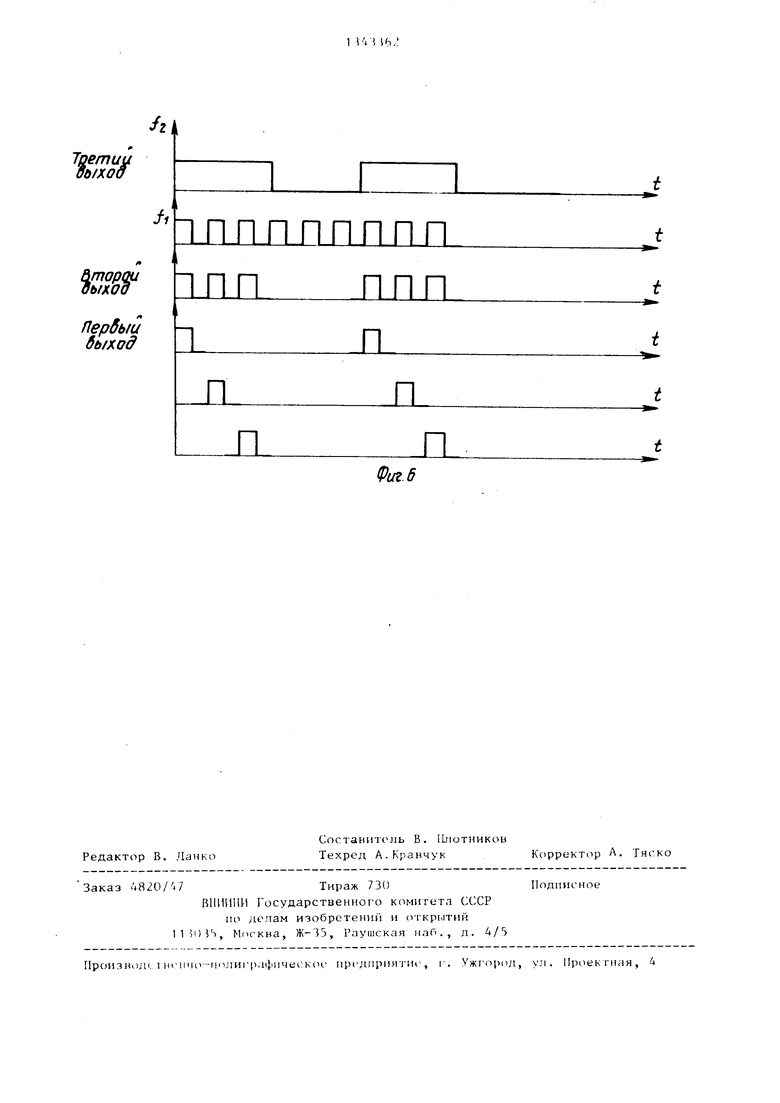

На фиг. 1 изображена схема предлагаемого устройства; на фиг. 2 - функциональная схема блока аналого-цифрового преобразования (параллельное преобразование); на фиг. 3 - функциональная схема блока управления (параллельное преобразование); на фиг.4 функциональная схема блока аналого- цифрового преобразования (последовательное преобразование); на фиг. 5 - функциональная схема блока управления (последовательное преобразование); на фиг. 6 - временные диаграммы работы блока управления (последовательно преобразование).

Устройство для фильтрации симметричных составляющих содержит блок 1 аналого-цифрового преобразования, первый выход которого соединен с входом регистра 2, второй выход - с входом регистра 3, третий выход - с входом регистра 4, выход регистра 2 - с первым входом вычитателя 5, выход регистра 3-е первыми входами сум- ,матора . 6 и вычитателя 7, выход регистра 4 - с вторыми входами сумматора 6 и вычитателя 7, выход вычитателя 5 - с входом регистра 8 сдвига и с первым входом вычитателя 9, выход вычитателя 7 - с входом регистра 10 сдвига и с первым входом вычитателя 1 1.

Выход вычитателя 9 соединен с первым входом умножителя 12, выход вычитателя 11 - с первым входом умножителя 13, выход блока 14 памяти - с вторым входом умножителя 12, выход блока 15 памяти - с вторым входом умножителя 13. Выход регистра 16 соединен с первыми входами умножителей 17 и 18, выход регистра 19 - с первыми входами умножителей 20 и 21. Выход блока 22 памяти соединен с вторыми входами умножителей 18 и 20, выход блока 23 памяти - с вторыми входами умножителей 18 и 21. Выход умножителя 17 соединен с первым входом сумматора 24, выход умножителя 20 - с первым входом вычитателя 25, выход умножителя 18 - с вторым входом нычитателя 25, выход умножителя

0

0

5

3622

21 - с вторым входом сумматора 24, выход сумматора 24 - с первым входом вычитателя 26, выход умножителя 12 - с вторым входом сумматора 27,

выход умножителя 13 - с вторым входом вычитателя 26, выход сумматора 21 - с входом регистра 16, выход вычитателя 28 - с входом регистра 17, первый выход блока 28 управления - с управляющими входами 2-4 регистров, второй выход блока 28 управления - с управляющим входом блока 1 аналого-цифрового преобразования,

третий выход - с управляющими входами регистров 8 и 9 сдвига и регистров 16 и 19.

Все блоки-, кроме блока аналого- цифрового преобразования и блока управления, стандартные.

Блок 1 аналого-цифрового преобразования может работать и параллельно и последовательно. Если преобразование осуществляется параллельно, то блок 1 аналого-цифрового преобразования построен по функциональной схеме, пример которой показан на фиг. 2, и содержит первый 29, второй 30 и третий 31 аналого-цифровые преобразователи, управляющие входы которых объединены и являются управляющим входом блока 1 аналого-цифрового преобразования. Преобразование всех трех сигналов в цифровую форму осуществляется одновременно по управ5 ляющему сигналу от блока 28 управления. В этом случае блок управления содержит генератор 32 тактовых импульсов и элемент 33 задержки (фиг. 3). Выход генератора 32 такто0 вых импульсов соединен с входом элемента 33 задержки и является вторым вьсходом блока 28 управления. Выход элемента 33 задержки соответствует первому и третьему выходам блока 28

5 управления.

Если преобразование осуществляется последовательно, то функциональная схема (фиг.4) блока 1 аналого- цифрового преобразования содержит

0 мультиплексор 34 входа, выход кото- рого соединен с входом блока 35 выборки и хранения, выход которого соединен с входом аналого-цифрового преобразователя 36, выход аналого5 цифрового преобразователя 36 - с

входом мультиплексора 37 выхода, управляющие входы мультиплексоров 34 и 37 входа и выхода объединены и являются управляющим входом блока 1

0

аналого-цифрового преобразования. Вход мультиплексора 34 входа является входом,а выход мультиплексора 37 выхода - выходом блока 1 аналого- цифрового преобразования.

По управляющим сигналам от блока 28 управления последовательно в цифровую форму преобразуются первый, второй и третий сигналы.

В этом случае блок 28 управления построен по функциональной схеме, кторая показана на фиг. 5 и содержит генератор 38 прямоугольных импуль- сов, выход которого соединен с первым выходом схемы И 39, выход генератора 40 тактовых импульсов является третьим выходом блока 28 управления и соединен с вторыми входами схемы И 39 RS-триггера 41. Выход схемы И 39 соединен с входом счетчика 42 и с первым входом схемы И 43, выход счетчика 42 - с первым входом RS-триггера 41 и первым входом распределителя 44 импульсов, выход RS- триггера 41 - с вторым входом схемы И 43. Выход схемы И 43 является вторым выходом блока 28 управления и соединен с вторым входом распреде- лителя 44 импульсов, выход которого является первым выходом блока 28 управления .

Генераторы 38 и 40 построены по той же схеме, что и генератор 32. Частота генератора 38 прямоугольных

импульсов f. , частота

тактовых импульсов fj

f, .

fl

генератора

генератора , причем

40 в

чение половины периода колебания открывает схему И 40 и устанавливает RS-триггер 41 в состояние 1, таким образом обе схемы И 39 и 43 открыты. Счетчик 42 считает три импульса и перебрасывает в состояние О RS-триггер 41, который закрывает схему И 43. Таким образом, на второй выход блока 28 управления поступают за один такт работы устройства

. В распреде- качестве

три импульса частоты f лителе 44 импульсов (в распределителя импульсов использован дешифратор) эти импульсы соответственно распределяются и потом поступают на первый выход блока 28 управления для поочередного строби- рования регистров 2-4.

С третьего выхода блока 28 управления поступают импульсы с частотой

b

f

, , оторые синхронизируют работу устройства.

Рассмотрим принцип работы устройства для фильтрации симметричных составляющих. Вначале поясним принцип выделения симметричных составляющих в предлагаемом измерителе.

Пусть X(t), XgCt), Xc(t) - фазные электрические величины, являющиеся смесью гармонического сигнала с некоторой помехой, т.е.

15

где S(t), Sg(t), S(t) - соответствующиепомехи.

Обозначим через U(t), U,(t) функции, являющиеся элс:ктрическими величинами прямой и обратной последовательности, любая из этих функций является гармоникой с частотой и. и поэтому может быть записана в следующем виде:

U- (t) 01- cos ш t + /5- sin u) t, (2)

30

35

40

45

где i 1,2.

Коэффициенты of у, ft можно выразить через коэффициенты Фурье сигналов X(t), Xg(t), X(,(t), соответствующих частоте u) . Если применять такой подход и коэффициенты Фурье сигналов X(t), X.(t), X(-(t) заменить оценками, полученными дискретным преобразованием Фурье по выборкам дискретных значений fx,(jt)5,

X./jO , {XeCjOJ, где ,

t- целое

со

положительное число; 1/t - частота дискретизации, то для i 1,2 значения U.(Kjt), где К 1,2..., вычисляются по алгоритму

UijCKit) Uj((K-1)4t) coscojt +

К-1,..., K-N+1; N

50

fUt ((K-1)4t) sin W4 t +

fY

K-H

),

(3)

56

где U(K4t) U ((K-l)jt) cosiv.it - - U. ((K-1)t) sino) t s ( K-H

),

Для фильтра обратной последовательности 1

Y (2X(Kdt) - Xg(KJt) - ));

(5)

Z - (X g (Kjt) - X (Kdt)) . (6)

Как видно из формул (3) и (А), алгоритмы вычисления значений симметричных составляющих Uj(Kdt) являются интеративными. Так как при К J N, Yj 0 и Z K. О, то первые N тактов являются интервалом сходимости данного алгоритма. Поэтому на выходе фильтра значение соответствукмце симметричной составляющей появляется с временной задержкой N4t, которая должна быть выбрана равной целому числу периодов аналнзируемьпс гармоник. Чем больше выбрана временная задержка, тем более высокая помехоустойчивость, а следовательно, и точность устройства.

Указанный алгоритм реализуется в устройстве для фильтрации симметричных составляющих следующим образом, Сигналы Хд(с), Xg(t) и X((t) поступают на входы блока 1 аналого-цифрового преобразователя и преобразуются в цифровой код X(KJt), Xg(K4t) Xj.(lCdt). По управляющим сигналам от блока 28 управления эти сигналы записываются в регистры 2 - 4. В сумматоре 6 определяется значение X (K4t) + Xp(KJt), которое далее поступает на вычитатель 5, где вычисляется значение Y 2Xy,(K4t) -Xg(KiSt) - X(K/it). В вычитателе 7 вычисляется значение Xj(Kjt) -Xc(K4t). В регистрах 8 и 10 сдвига в первые N тактов записано значение

О, и Y;,. О

и Z. 0.

Для осуществления произведения

выход регистра 2 подключен к входу вычитателя 5 со сдвигом на один двоичный разряд.

2Хд(Клс)

6 вычитателе 10 определяется значение YH - Y,. , в вычитателе 11 - значение ZK - ZK-I. В блоке 14 памяти записано значение . в блоке

3N

15 памяти - значение . В умножитеУзы

ле 12 умножаются Y ,, - Y, „и ---,, в

к K-N 3N

5

0

5

0

5

0

5

0

5

умножителе 13 - Z, - Z и - -.

/3N

В регистрах 16 и 19 в первом такте работы устройства записано значение О, а при дальнейшей работе под управлением сигналов от БУ 28 записываются значения U.(K4t) и и| (KJt).

Б блоке 22 памяти записано значение cos ((jj at) , в блоке 23 памяти - значение sin (). В умножителе 17 перемножаются значения и;(Кл1г) и cos (u)4t), в умножителе 20-U() и sin (), в умножителе 18 - Uj(Kdt) и sin (wdt), в умножителе 21 - U(Kdt) и sin (di)4t). В сумматоре 24 суммируются значения и- (K4t) cos (u)jt) и Ij () sin (ujt). В вычитателе 25 определяется значение U(K/lt) cos (и) ut} -U;(K4t) sin (wijt). В вычитателе 26 определяется вспомогательное значение U- CK/lt) U|((K-1)jt) cos ((.at)-,

-U| ((K-1)4t) sin (iJJt) - (Z, Z ). В сумматоре 27 после N тактов работы определяется значение, соответствующее симметричной составляющей

U,(Kdt) U|((K-1)4t) cos (wHt) - - ut((K-1)4t) sin (oidt) +

Ч -

В предлагаемом устройстве с применением дискретного преобразования Фурье с постоянным шагом дискретизации осуществляется селективная фильтрация основной гармоники. Как известно, это позволяет полностью ликвидировать влияние гармоник, частоты которых кратны частоте основной гармоники, а погрешность вносимая другими видами помех и шумов, может быть сведена до произвольно малой величины увеличением времени анализа.

Ниже приведено получение основных соотношений (3), (4) на примере фильтра обратной последовательности.

Сигналом обратной последовательности является

U(t)| (u.t +1/) + + Ugsin (u)t + (g+2/r/3) +

+ Uj. sin (wt +4 ,+

r U COS (/Д 61 n Ы t +

- T U.siny. cos Lot +

/ h

13Д33628

Величины el i ft являются коэффициентами Фурье сигнала обратной последовательности U(t) на частоте и, как видно по формулам (9), опре- 1деляются коэффициентами Фурье сиг+ U sin / cosu t - - Ujcosq-gsinwt - налов U(t), UgCt), Uc (t) .

Так как сигнал U(t) выражается через коэффициенты Фурье сигналов

), Ug(t), Uc(t), то целесообразно пользоваться Фурье-фильтром. Для нахождения текущего значения U (t) воспользуемся интервалом длительности б , предшествующим моменту

,g времени t, т.е. интервалом (t - 8,t). Учитьшая свойства амплитудно-частотной характеристики Фурье фильтра, длительность 0 следует выбирать равной целому числу 1 периодов Т

2 7f w гармоник сигналов U(t), Ug(t), ), т.е. е IT. Тогда, беря за начало отсчета времени момент t-6, имеем:

f3

+ -г-Uj cos (gCos U) t

----Ua sinqi. Sin u; t

о 8

1„

--j-U costfj.sincot

1,T --2 Uj, sin ly coswt

( cos (/j, COS U3t +

f3 + -j- Uc sintf sin U) tj . (7)

Величины a U4sinV. и Ь. и. соs(/являются коэффициентами Фурье сигнала Uд(t) на частоте ы . Аналогично для сигналов Ug(t) и U|-(t) имеем ад Ugsini, bg Ug cos(/g, 3 U sini/;., bc Upcosv,. Уравнение (7) можно переписать в следующем виде:

u(t) {(ъ,, - Ь, 25 «(t) Q- (2U (-.) - Ue(C) t-б

-U (Г) ) sin U) (t-t+ e ) d J i

-S f3 (Ug(f) - UeO

t-e cosw ( 1 -t + 9)d ;J; (10)

30

3

Y3

2

Уз

35

+ -2 a ) sin uj t +

(- be-a c- -f-bgV 1

- --- b,.. ) coswt 7 ( -be - Y3 (aj- a,)) sinuit ( ag- a + + (bg- be) cos U) t a sinwt +/5coswt, (8)

40

45

50

/i(t) :rf (2U( J) - UgCf) - i-e

- U ©) cosw (r - t +

t

+ 0)dC +J Y3 (U5(O t-6-U (1)) sinu) (г-с+0)c/:j,

(11)

и вместо уравнения (8) получаем: и (t) o/(t) sin со (I-t +e) +

+ /J (t) cos w( 1 - t + e ) .

(12)

где

I bg- bc-V3 (ag- ас);

(9)

/i 2а,- ag- a, ( - be) .

«(t) Q- (2U (-.) - Ue(C) t-б

-U (Г) ) sin U) (t-t+ e ) d J i

-S f3 (Ug(f) - UeO

t-e cosw ( 1 -t + 9)d ;J; (10)

/i(t) :rf (2U( J) - UgCf) - i-e

- U ©) cosw (r - t +

t

+ 0)dC +J Y3 (U5(O t-6-U (1)) sinu) (г-с+0)c/:j,

(11)

и вместо уравнения (8) получаем: и (t) o/(t) sin со (I-t +e) +

+ /J (t) cos w( 1 - t + e ) .

(12)

Текущее значение U(t) получаем подстановкой в уравнение (12) . Так как sin(jo9 sin 2 я 1 О, cosw0 1, то

55

U(t) ,(t)

(13)

При дискретной обработке сигналов обрабатываются не аналоговые сигмаI /, т т t т10

у13А3362

лы, а их отсчеты, взятые в моменты 1

времени t. Пусть t Kjt, где К + , sin-) +

1,2,..., N; лt - шаг дискретизации) N - число обрабатываемых отсчетов; е IT. Тогда, заменяя в к уравнении (11) интегралы суммами и

учитывая равенство (13), получаем: Заменим i параметром j 1+1, . N2 7Г1 Тогда получаем:

„,,.1,

-г,... sin 2111-,, с,4)

, , , , - ,..-. ), .

1-Де Y;,,., 3 2ид (t ;,. ) - ,5

Ч Y. - YK-,)

- U5(t,4,-N) -Uc(t ;.к-ы);

(15)1 2;Г1

ZU,.H .,.,) -Uc(t,..,.,) ..N Г

(16) °

+ Z --lL 2П Формулы (14) - (16) задают алго-j K-i-N N N

ритм фильтра сигнала обратной последовательности при классической pea-I . fv sin --- лизации Фурье-фильтра. N j K-i-N N

i 1 Для получения каждого очередного-- j-, 2Ji

значения U(t) необходимо сперва- Zj cos j ) iri

вычислить значения Y и Z, для чего требуются 3 операции алгебраичес-+ - (k K-N (Т)

кого суммирования 2 и операции умно-30 формулы (14) следует, что жения (2U (t 1)получаем сдвигом зна- щ„-, .

чения Цд (t )) на один разряд влево), - У (у . cos --- + .х и далее по формуле (14) вычислить

значение и (t), что требует 2N one- xsin ---iJ- u(t ) (18)

раций умножения (не засчитываетсяу, N

умножение на 1/N, так как если N выб „Рассмотрим вспомогательную велирать равным степени числа 2, оно сво чину:

дится к сдвигу результата суммирова- .

ния на соответствующее число разря- U (t ) - (Y sin ДОН вправо) и 2N операций алгебраи-К) Ui i+K-N N ческого суммирования. Следовательно,

если через R и R (, обозначить со- .,ц j -

ответственно число операций умножения и cy fмиpoвaния, необходимых для Преобразуем U(t) в следующем

получения каждо1;о очередного значе-J5 виде:

ния и (tj, то R 2(N+1), RC 1 ±. . 2N + 3. Преобразуем формулу (14): (tJ i+k-N N

N-1

1 ,., 2т И

ЬО- i.-, -

(4)5 Г ,,. ,..

+ Z, sin --) + I (Y sin 2 - Z.cos 2«1 N .

+ (YK cos 27Г 1 + Z sin2n-- sin 0 + Z,.cos,0)

1 V .V . 2l(li - Y.cos 0 - 0) N f:- Г

S I .... - Ч-- - 3,,cos 2ili, I /, т т t т10

А3362

- N - Vr) .

Заменим i параметром j i+1. Тогда получаем:

N

Из уравнения (13) следует, что

N

1 V cv 2/1 Ij N 2- (Y.,.,. sin ----i - Z .

co.2|U,,,.,,

Подставляя формулы (15) и (18) уравнения (14) и (17), получаем:

и(ц) U(t,,,) cos 2ii +U(t,.,) 30

«in -Г S 22) U4t,) U(t,.,) cos 21135

/ ч 2iri и, (t., ) sin ---- 1

fj k K-N

(23)

При замене обозначений в (22) и

t Kjt, t.,

C7

N

(K-1) ut, получим основные выражения (3) и (4) .

Формулы (15), (16), (22) и (23) задают алгоритм фильтра сигнала обратной последовательности, отличающийся реализацией Фурье-фильтра.

Как и в классическом случае, сперва следует вычислить значения Y и Z| формулы (15) и (16). В блок-схеме устройства (фиг. 1) это выполняют блоки 1-15.

Для вычисления каждого очередного значения U (t,) используется предыдущее значение U (t) этого дискретного сигнала и предыдущее зна343362)2

чение U(t., ) вспомогательного дискретного сигнала формула (22).

Следовательно, параллельно необ- . ходимо вычислять процесс и (t), для чего также используются значения U(t) и U (t,., ) формула (23). Величины cos 2T1/N и sin - константы, заданные параметрами 1

N. В блок-схеме устройства Фурье- фильтр реализуется блоками 16-27,

Как видно по формулам (15), (16), (22) и (23), для получения каждого 5 очередного значения U (t) требуемые числа операций умножения Ry и суммирования R составляют R 6, R 9 независимо от числа N используемых отсчетов. Предлагаемое устройство для получения каждого очередного значения сигнала обратной последовательности U (t) по сравнению с применением классической реализации Фурье-фильтра позволяет в f

0

5

0

5

(N+1)3 раз сократить требуемое число операций умножения ив YJ. (2N+3)/9 раз сократить число операций суммирования.

Так, например, при N 32, имеем у, 11; v, 7,4; а при N 256 . 171,3; , 57,2.

Если через i j и tj. обозначить времена, необходимые для выполнения операций умножения и суммирования соответственно, то для получения каждого очередного значения U(t ) предлагаемое устройство требует в

- 2lN+l)();Cc

40

+ 9

(N+1)/3

раз меньше времени, чем устройство, реализующее классический алгоритм Фурье-фильтра. Таким образом, предлагаемое устройство позволяет в г раз повысить частоту дискретизации входных сигналов и, следовательно, в -у раз увеличить период амплитудно-частотной характеристики дискретного Фурье-фильтра. Этим повьшается точность фильтрования высокочастотных составляющих присутствующих на входе шумов и помех; в v раз увеличивается число обрабатываемых отсчетов и, следовательно, уменьшается погрешность ( :; V раз), вносимая низкочастотными составляющими шумов;

1313

в - раз повьшается частота появления значений сигнала обратной последовательности на выходе устройства; не требуется записывать в память устройства значения гармоники sin 2, li/N, необходимые при классической реализации Фурье-фильтра, В предлагаемом устройстве для этого используются лишь две константы; sinZ/ l/N и cos 2lil/N.

Формула изобретения

Устройство для фильтра1щи симметричных составляющих, содержащее первый, второй и третий регистры, управляющие входы которых соединены с первым выходом блока управления, и первый сумматор, отличающее- с я тем, что, с целью повьшения точности за счет повышения помехоустойчивости, в него дополнительно введены блок аналого-цифрового преобразования, четвертый и пятый регистры, первый, второй, третий, четвертый, пятый и шестой вычитатели, второй и третий сумматоры, первый, второй, третий и четвертый блоки памяти, первый, второй, третий, четвертый, пятый и шестой умножители, первый и второй регистры сдвига, при этом первый, второй и третий выходы блока аналого-цифрового преобразования соединены соответственно с первыми входами первого, второго и третьего регистров, выход первого регистра соединен с первым входом первого вы- читателя, выход второго регистра соединен с первыми входами первого сумматора и второго вычитателя, вторые входы которых соединены с выходом третьего регистра, выход первого сумматора соединен с вторым входом первого вычитателя, выход первого вычитателя соединен с первыми входами первого регистра сдвига и третьего вычитателя, выход второго вычитателя соединен с первыми входами второго

14

0

регистра сдвига и четвертого вычитателя, выходы первого и второго регистров сдвига соединены соответственно с вторыми входами третьего и четвертого вычитателей, выходы третьего и четвертого вычитателей соединены соответственно с первыми входами первого и второго умножителей,

выходы первого и второго блоков памяти соединены соответстве шо с вторыми входами первого и второго умножителей, выход четвертого регистра соединен с первыми входами третьего

E, и пятого умножителей, выход пятого регистра соединен с первыми входами четвертого и шестого умножителей, выход третьего блока памяти соединен с вторыми входами третьего и четвертого умножителей, выход четвертого блока памяти соединен с вторыми входами пятого и шестого умножителей, . выход третьего умножителя соединен с первым входом второго сумматора, выход четвертого умножителя соединен с первым входом пятого вычитателя, выход пятого умножителя соединен с вторым входом пятого вычитателя, выход шестого умножителя соединен с вторым входом второго сумматора, выход второго сумматора соединен с первым входом третьего сумматора, выход пятого вычитателя соединен с первым входом шестого вычитателя, выход третьего сумматора соединен с первым входом четвертого регистра, выход шестого вычитателя соединен с первым входом пятого регистра, выход первого умножителя соединен с вторым входом третьего сумматора, выход второго умножителя соединен с вторым вхо- дом шестого вычитателя, второй выход блока управления соединен с управляющим входом блока аналого-цифровогю преобразова)1ия, третий его выход соединен с вторыми входами первого и второго регистров сдвига и четвертого и пятого регистров.

о

0

5

0

Редактор В. Ланко

Составитель В. Плотников

Техред А.Кравчук , Корректор Л- Тяско

Заказ 4820/V/Тираж 730Подпиское

ВИИИ11И Государственного комитета С;ССР

по делам изобретений и откр1.1тий lliOJS, Могква, Ж-35, Раушская маб., д. A/-S

ПрОИЗИОДС. I 1ИЧ

-пoJIИlp.lфичecкot предприлтио, гч Ужгород, ул. Проектная, (

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель симметричных составляющих | 1985 |

|

SU1255964A1 |

| Амплифазометр с дискретной ортогональной обработкой сигнала | 1986 |

|

SU1406513A1 |

| Устройство для измерения фазовых сдвигов | 1984 |

|

SU1226341A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1290351A1 |

| Устройство для вычисления скользящего спектра | 1988 |

|

SU1527642A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Устройство для вычисления коэффициентов Фурье | 1983 |

|

SU1096655A1 |

| Цифровой фильтр | 1987 |

|

SU1390784A1 |

| Устройство дискретного преобразования Фурье | 2017 |

|

RU2647701C1 |

| Устройство для вычисления спектра временного ряда | 1973 |

|

SU492881A1 |

Изобретение относится к электроизмерительной технике и может быть использовано в релейной защите электроустановок от повреждений. Целью изобретения является повышение точности фильтрации симметричных составляющих за счет повьшения помехоустойчивости устройства. Цель достигается введением в устройство блока 1 аналого-цифрового преобразования, четвертого 3 и пятого 4 регистров, второго 24 и третьего 26 сумматоров. Это позволяет повысить частоту дискретизации входных сигналов и увеличить период амплитудно-частотной характеристики дискретного Фурье-фильтра. Таким образом повышается точность отфильтровывания высокочастотных составляющих. 6 ил. (Л со 4 СО со О5 N3

| Фильтр симметричных составляющих системы фазных сигналов | 1979 |

|

SU896756A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для фильтрации составляющих прямой последовательности трехфазных электрических величин | 1980 |

|

SU1034112A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1987-10-07—Публикация

1985-06-10—Подача