t

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано при цифровом спектральном анализе многочастотных узкополосных сигналов, сигналов связи и управления.

Целью изобретения является повышение быстродействия.

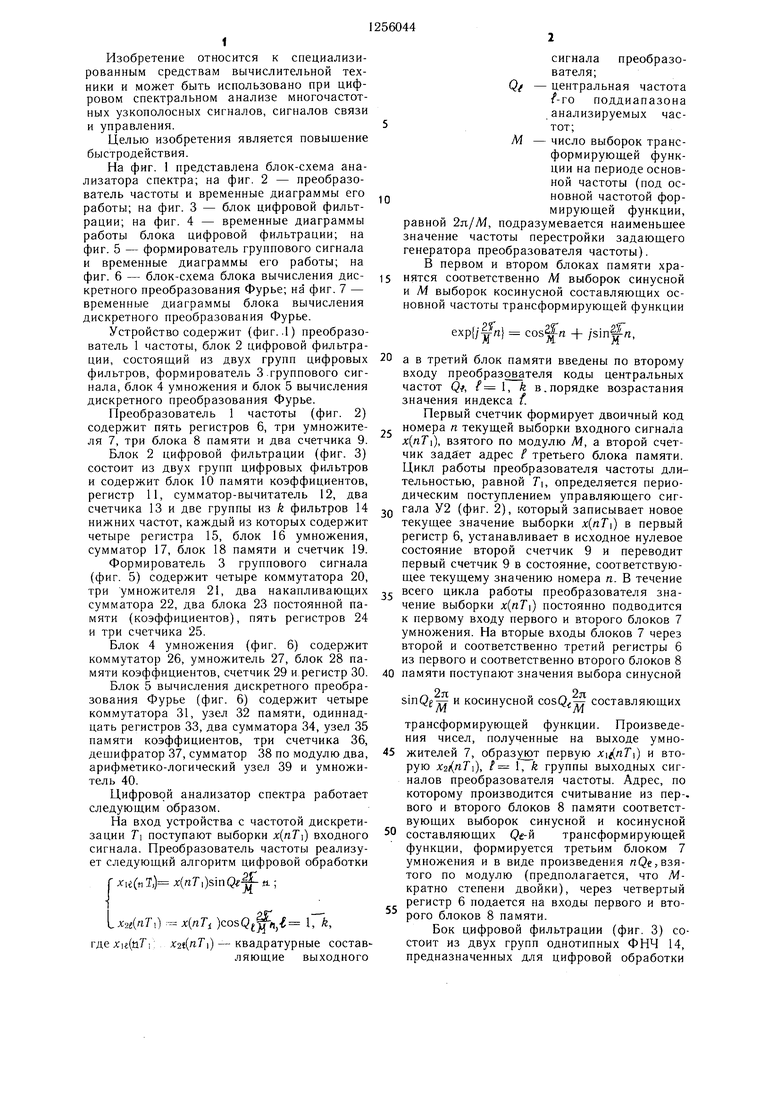

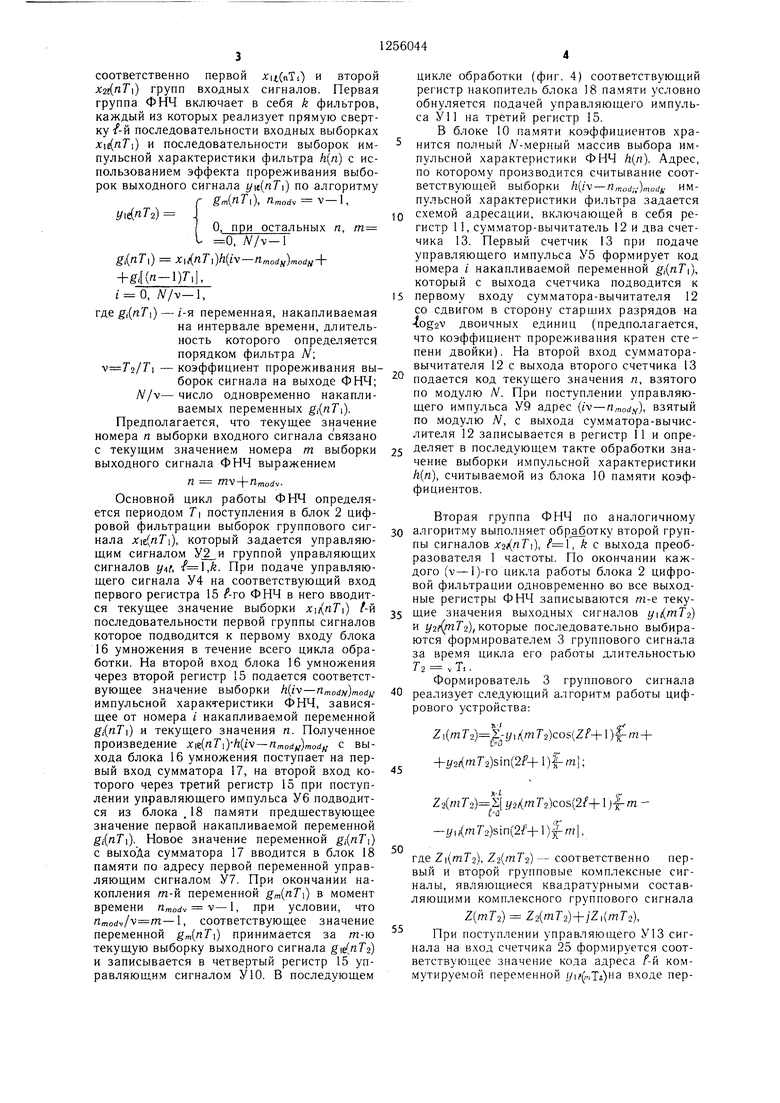

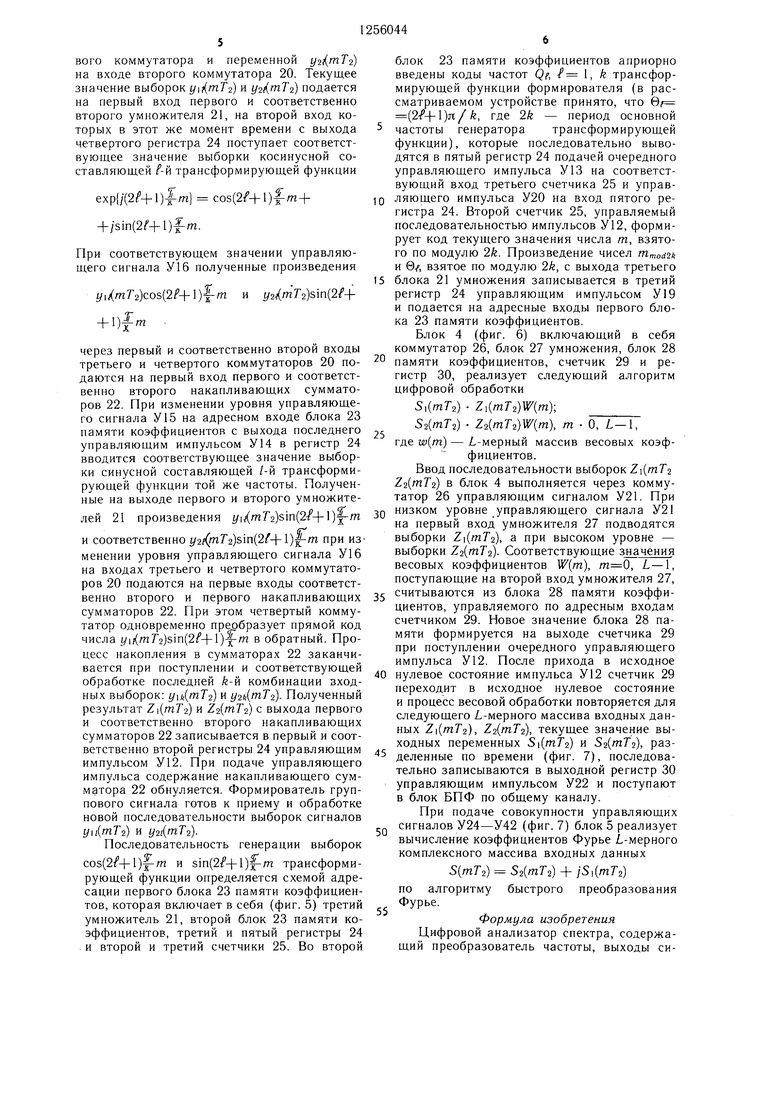

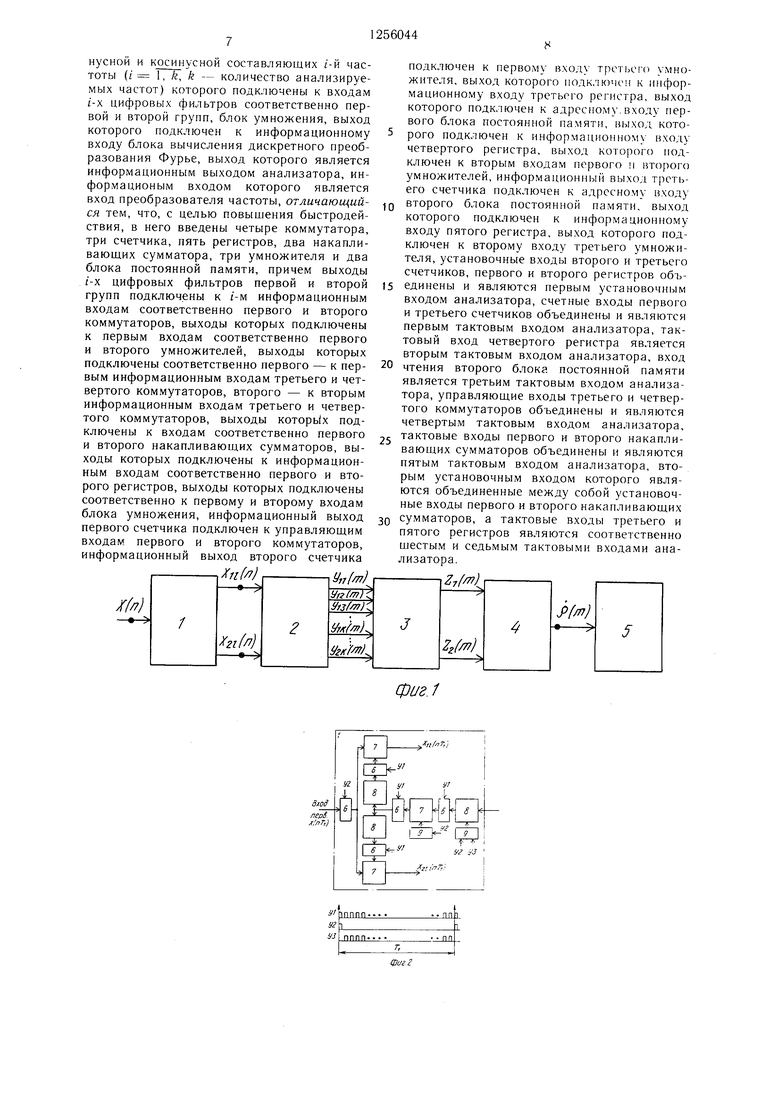

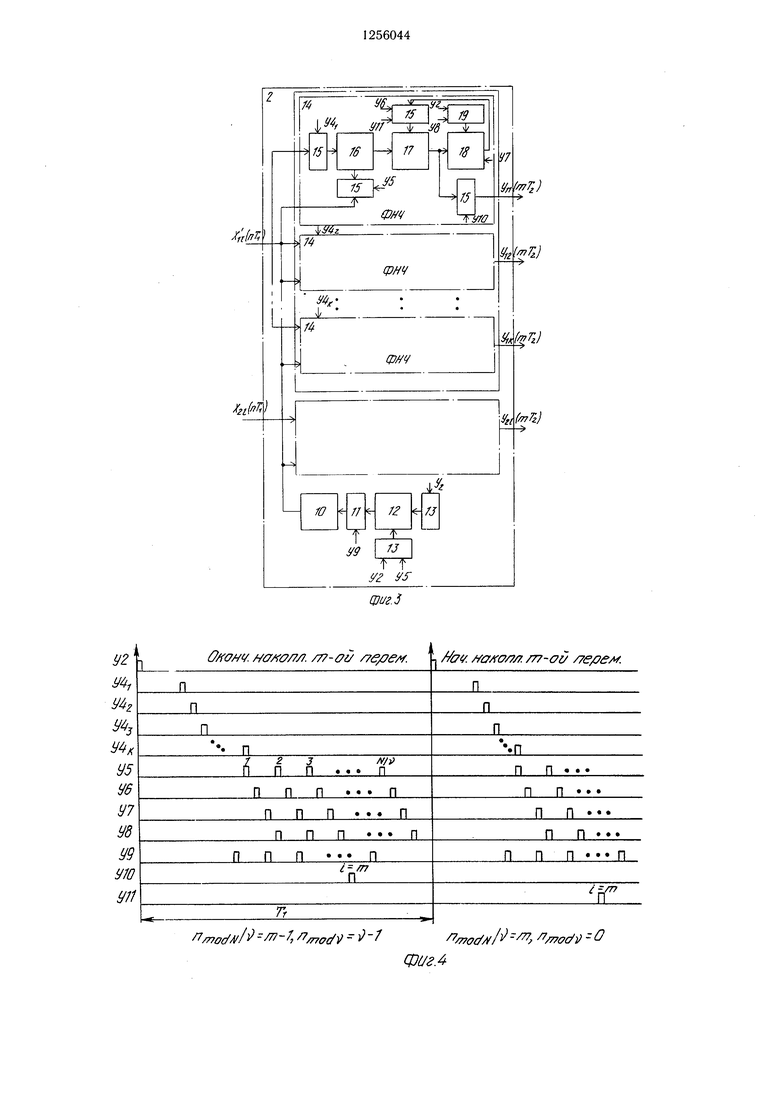

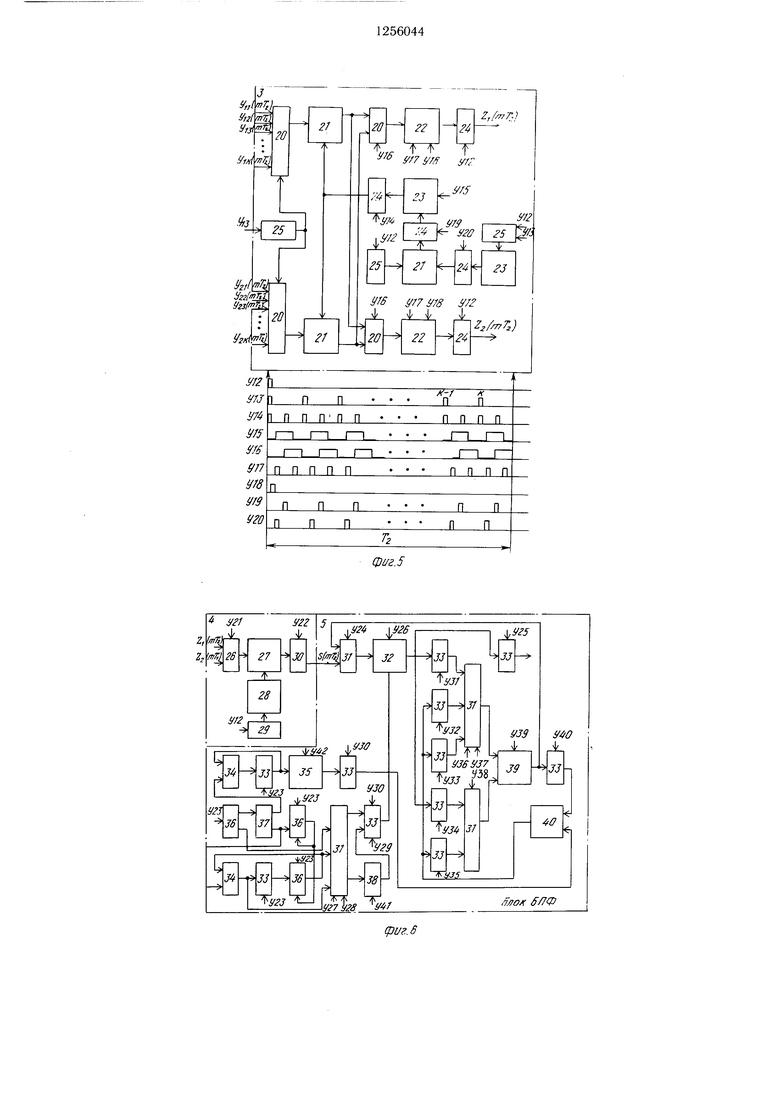

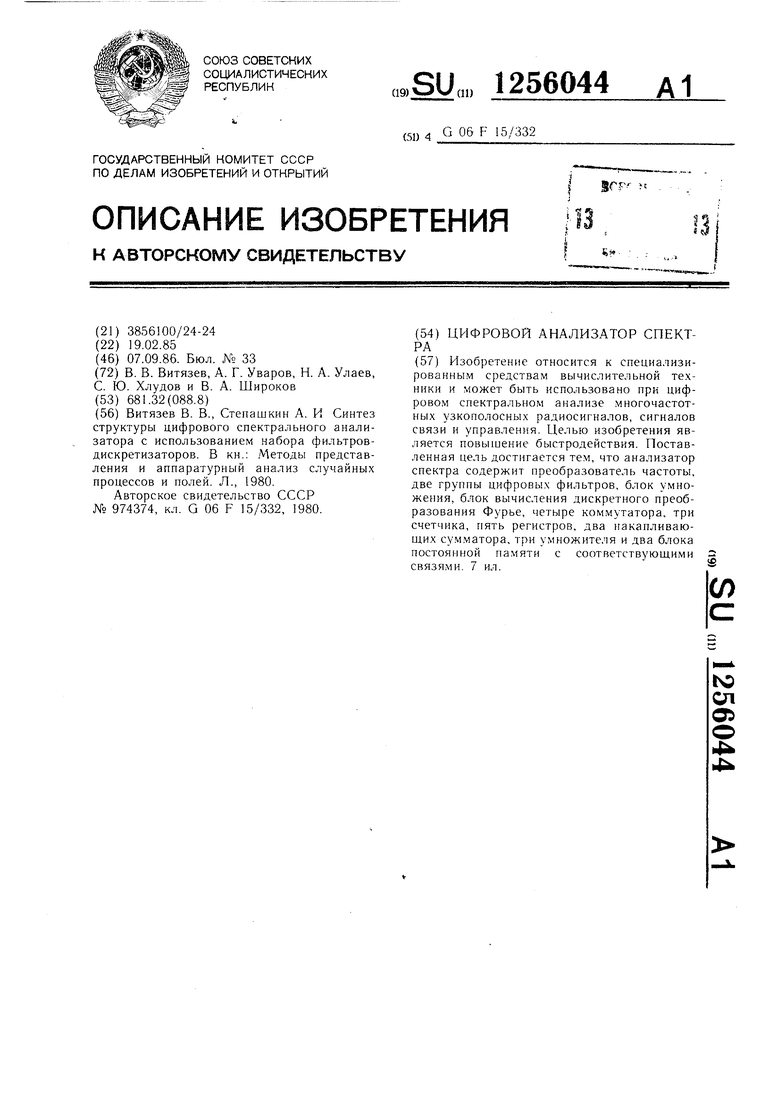

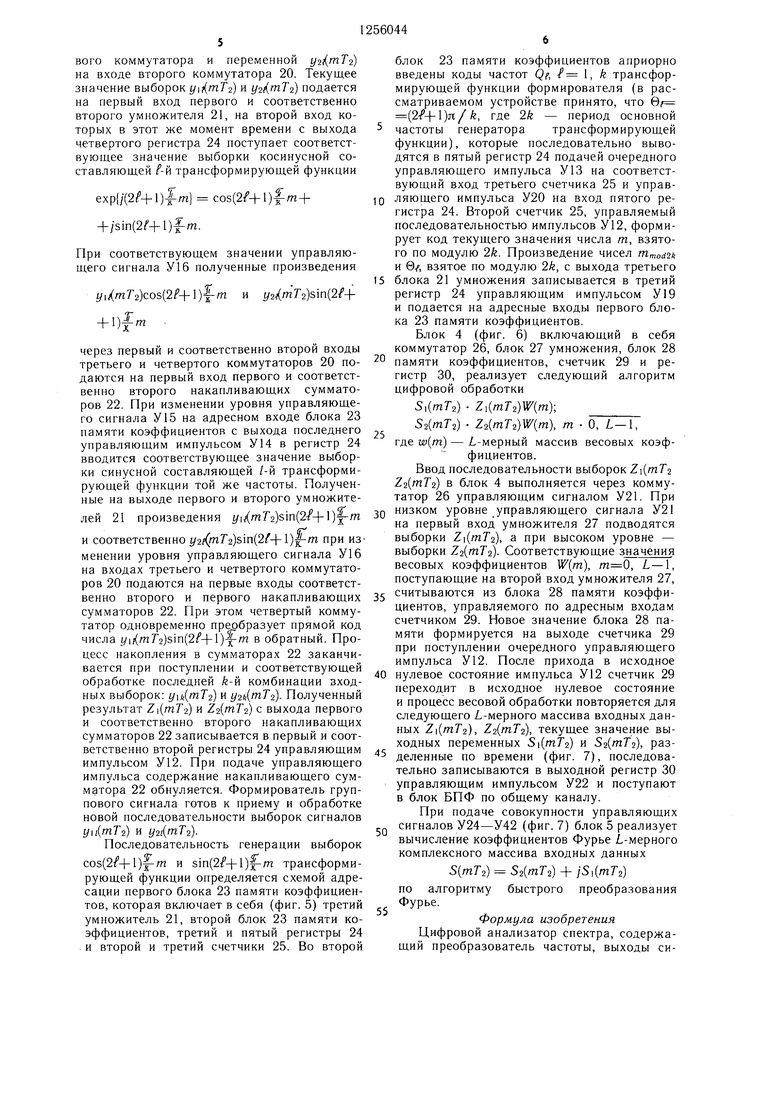

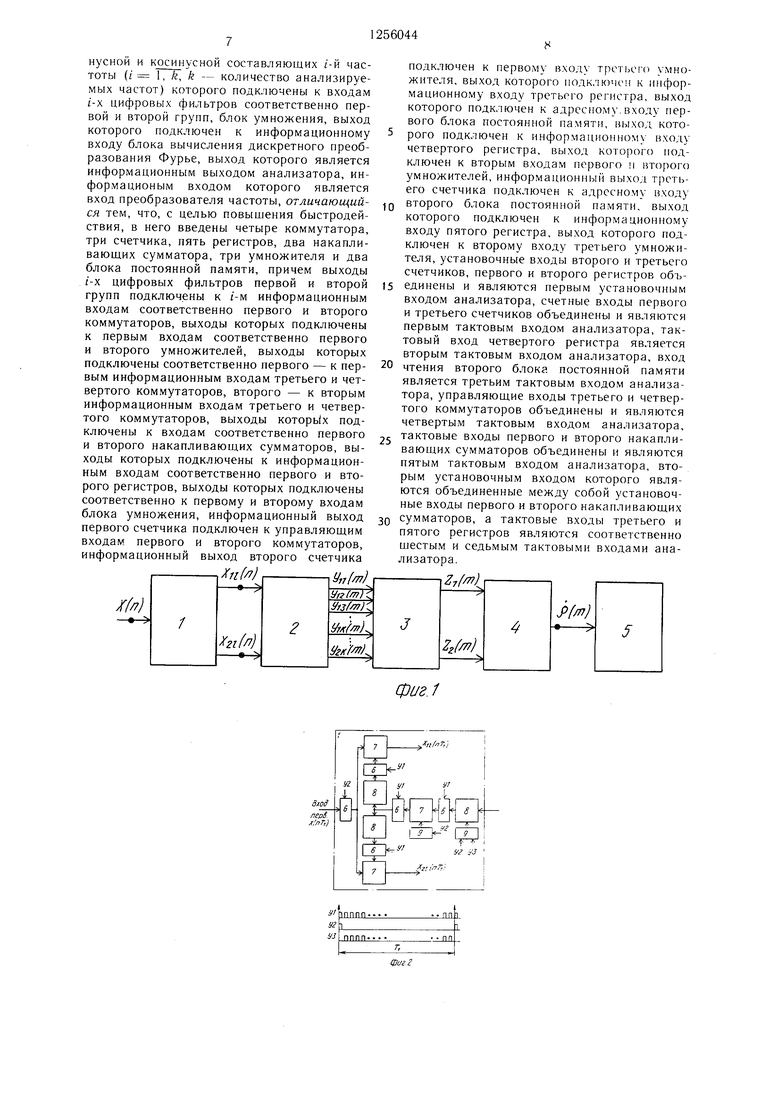

На фиг. 1 представлена блок-схема анализатора спектра; на фиг. 2 - преобразователь частоты и временные диаграммы его работы; на фиг. 3 - блок цифровой фильтрации; на фиг. 4 - временные диаграммы работы блока цифровой фильтрации; на фиг. 5 - формирователь группового сигнала и временные диаграммы его работы; на фиг. 6 - блок-схема блока вычисления дискретного преобразования Фурье; на фиг. 7 - временные диаграммы блока вычисления дискретного преобразования Фурье.

Устройство содержит (фиг. .1) преобразователь 1 частоты, блок 2 цифровой фильтрации, состоящий из двух групп цифровых фильтров, формирователь 3.группового сигнала, блок 4 умножения и блок 5 вычисления дискретного преобразования Фурье.

Преобразователь 1 частоты (фиг. 2)

сигнала преобразователя;

Q/ - центральная частота f-ro поддиапазона анализируемых час-

М - число выборок трансформирующей функции на периоде основной частоты (под ос1Qновной частотой формирующей функции,

равной 2л/М, подразумевается наименьщее значение частоты перестройки задающего генератора преобразователя частоты).

В первом и втором блоках памяти хра- 15 нятся соответственно М выборок синусной и М выборок косинусной составляющих основной частоты трансформирующей функции

;2Г„

20

ехр{/ п} + ,

а в третий блок памяти введены по второму входу преобразователя коды центральных частот Q-f, , k в.порядке возрастания значения индекса f.

Первый счетчик формирует двоичный код

содержит пять регистров 6, три умножите- номера п текущей выборки входного сигнала

ля 7, три блока 8 памяти и два счетчика 9. Блок 2 цифровой фильтрации (фиг. 3) состоит из двух групп цифровых фильтров и содержит блок 10 памяти коэффициентов, регистр 11, сумматор-вычитатель 12, два

x(nTi), взятого по модулю М, а второй счетчик задает адрес f третьего блока памяти. Цикл работы преобразователя частоты длительностью, равной Т, определяется периодическим поступлением управляющего сигсчетчика 13 и две группы из k фильтров 14 Q У2 (фиг. 2), который записывает новое

нижних частот, каждый из которых содержит четыре регистра 15, блок 16 умножения, сумматор 17, блок 18 памяти и счетчик 19. Формирователь 3 группового сигнала (фиг. 5) содержит четыре коммутатора 20,

текущее значение выборки x(nTi) в первый регистр б, устанавливает в исходное нулевое состояние второй счетчик 9 и переводит первый счетчик 9 в состояние, соответствующее текущему значению номера п. В течение

три умножителя 21, два накапливающих - всего цикла работы преобразователя знасумматора 22, два блока 23 постоянной памяти (коэффициентов), пять регистров 24 и три счетчика 25.

Блок 4 умножения (фиг. 6) содержит коммутатор 26, умножитель 27, блок 28 пачение выборки х(пТ) постоянно подводится к первому входу первого и второго блоков 7 умножения. На вторые входы блоков 7 через второй и соответственно третий регистры 6 из первого и соответственно второго блоков 8

мяти коэффициентов, счетчик 29 и регистр 30. 40 памяти поступают значения выбора синусной

Блок 5 вычисления дискретного преобразования Фурье (фиг. 6) содержит четыре коммутатора 31, узел 32 памяти, одиннадцать регистров 33, два сумматора 34, узел 35 памяти коэффициентов, три счетчика 36, дешифратор 37, сумматор 38 по модулю два, арифметико-логический узел 39 и умножитель 40.

Цифровой анализатор спектра работает следующим образом.

На вход устройства с частотой дискретизации Г поступают выборки х(пТ) входного сигнала. Преобразователь частоты реализует следующий алгоритм цифровой обработки

f х,е(«Т,) x(nTt)smQfy- я.;

,x-2e(nTi - x(nTi ),€ iTk,

где jcielnTi: Х2е(/гГ|) - квадратурные состав

ляющие выходного

sinQg и косинусной cosQf- составляющих

трансформирующей функции. Произведения чисел, полученные на выходе умно- 45 жителей 7, образуют первую ) и вторую , / , k группы выходных сигналов преобразователя частоты. Адрес, по которому производится считывание из первого и второго блоков 8 памяти соответствующих выборок синусной и косинусной составляющих Qf-й трансформирующей функции, формируется третьим блоком 7 умножения и в виде произведения «Qe,взятого по модулю (предполагается, что М- кратно степени двойки), через четвертый регистр 6 подается на входы первого и второго блоков 8 памяти.

Бок цифровой фильтрации (фиг. 3) со стоит из двух групп однотипных ФНЧ 14, предназначенных для цифровой обработки

50

256044

сигнала преобразователя;

Q/ - центральная частота f-ro поддиапазона анализируемых час-

М - число выборок трансформирующей функции на периоде основной частоты (под ос1Qновной частотой формирующей функции,

равной 2л/М, подразумевается наименьщее значение частоты перестройки задающего генератора преобразователя частоты).

В первом и втором блоках памяти хра- 15 нятся соответственно М выборок синусной и М выборок косинусной составляющих основной частоты трансформирующей функции

;2Г„

20

ехр{/ п} + ,

а в третий блок памяти введены по второму входу преобразователя коды центральных частот Q-f, , k в.порядке возрастания значения индекса f.

Первый счетчик формирует двоичный код

номера п текущей выборки входного сигнала

номера п текущей выборки входного сигнала

x(nTi), взятого по модулю М, а второй счетчик задает адрес f третьего блока памяти. Цикл работы преобразователя частоты длительностью, равной Т, определяется периодическим поступлением управляющего У2 (фиг. 2), который записывает новое

У2 (фиг. 2), который записывает новое

текущее значение выборки x(nTi) в первый регистр б, устанавливает в исходное нулевое состояние второй счетчик 9 и переводит первый счетчик 9 в состояние, соответствующее текущему значению номера п. В течение

всего цикла работы преобразователя знавсего цикла работы преобразователя значение выборки х(пТ) постоянно подводится к первому входу первого и второго блоков 7 умножения. На вторые входы блоков 7 через второй и соответственно третий регистры 6 из первого и соответственно второго блоков 8

памяти поступают значения выбора синусной

sinQg и косинусной cosQf- составляющих

трансформирующей функции. Произведения чисел, полученные на выходе умно- 5 жителей 7, образуют первую ) и вторую , / , k группы выходных сигналов преобразователя частоты. Адрес, по которому производится считывание из пер, вого и второго блоков 8 памяти соответствующих выборок синусной и косинусной составляющих Qf-й трансформирующей функции, формируется третьим блоком 7 умножения и в виде произведения «Qe,взятого по модулю (предполагается, что М- кратно степени двойки), через четвертый регистр 6 подается на входы первого и второго блоков 8 памяти.

Бок цифровой фильтрации (фиг. 3) состоит из двух групп однотипных ФНЧ 14, предназначенных для цифровой обработки

0

соответственно первой хц(пТО второй ) групп входных сигналов. Первая группа ФНЧ включает в себя k фильтров, каждый из которых реализует прямую свертку /-Й последовательности входных выборках xii{nTi) и последовательности выборок импульсной характеристики фильтра h(n) с использованием эффекта прореживания выборок выходного сигнала (nT) по алгоритму

г gm(nTt), V-1,

(пТ2) J

О, при остальных п, т. I 0, N/V - 1

g{nT) )h()modu+

+g.l(n-l)T,

, yV/v-1,

гле gi(nT) - /-Я переменная, накапливаемая на интервале времени, длительность которого определяется порядком фильтра jV;

- коэффициент прореживания выборок сигнала на выходе ФНЧ; N/V- число одновременно накапливаемых переменных gi(nTi}. Предполагается, что текуш.ее значение номера п выборки входного сигнала с вязано с текущим значением номера т выборки выходного сигнала ФНЧ выражением

п mv+imodv.

Основной цикл работы ФНЧ определяется периодом Т поступления в блок 2 цифровой фильтрации выборок группового сигнала .(nTi), который задается управляющим сигналом группой управляющих сигналов 1/4Л f,k. При подаче управляющего сигнала У4 на соответствующий вход первого регистра 15 -го ФНЧ в него вводится текущее значение выборки Х(пТ) f-и последовательности первой группы сигналов которое подводится к первому входу блока 16 умножения в течение всего цикла обработки. На второй вход блока 16 умножения через второй регистр 15 подается соответствующее значение выборки h(iv - «mod/)modv

импульсной характеристики ФНЧ, зависящее от номера i накапливаемой переменной gi(nT) и текущего значения п. Полученное произведение xte.(nTi)-h(iv-nr,odtf modff с выхода блока 16 умножения поступает на первый вход сумматора 17, на второй вход которого через третий регистр 15 при поступлении управляющего импульса У6 подводится из блока. 18 памяти предшествующее значение первой накапливаемой переменной gi(nT). Новое значение переменной gi(nTi) с выхо Да сумматора 17 вводится в блок 18 памяти по адресу первой переменной управляющим сигналом У7. При окончании накопления т-к переменной gm(nT) в момент времени nmorfv v-1, при условии, что rtmodv/v m-1, соответствующее значение переменной gm(nT) принимается за /п-ю текущую выборку выходного сигнала gie(«T 2) и записывается в четвертый регистр 15 управляющим сигналом У10. В последующем

цикле обработки (фиг. 4) соответствующий регистр накопитель блока 18 памяти условно обнуляется подачей управляющего импульса У11 на третий регистр 15.

В блоке 10 памяти коэффициентов хранится полный j V-мерный массив выбора импульсной характеристики ФНЧ Л(л). Адрес, по которому производится считывание соот- ветствуюцдей выборки h(i - nmod;; mod импульсной характеристики фильтра задается

схемой адресации, включающей в себя регистр 11, сумматор-вычитатель 12 и два счетчика 13. Первый счетчик 13 при подаче управляющего импульса У5 формирует код номера / накапливаемой переменной gi(, который с выхода счетчика подводится к

первому входу сумматора-вычитателя 12 со сдвигом в сторону старших разрядов на -fog2V двоичных единиц (предполагается, что коэффициент прореживания кратен степени двойки). На второй вход сумматора- вычитателя 12 с выхода второго счетчика 13

подается код текущего значения л, взятого по модулю N. При поступлении управляющего импульса У9 адрес ((v - ), взятый по модулю yV, с выхода сумматора-вычислителя 12 записывается в регистр 11 и определяет в последующем такте обработки значение выборки импульсной характеристики h(n), считываемой из блока 10 памяти коэффициентов.

Вторая группа ФНЧ по аналогичному алгоритму выполняет обработку второй группы сигналов ), f, k с выхода преобразователя 1 частоты. По окончании каждого (v-1)-го цикла работы блока 2 цифровой фильтрации одновременно во все выходные регистры ФНЧ записываются ш-е теку- щие значения выходных сигналов у тТ-2} и y2i(rnT2), которые последовательно выбираются формирователем 3 группового сигнала за время цикла его работы длительностью 7-2 V Т,.

Формирователь 3 группового сигнала реализует следующий алгоритм работы цифрового устройства:

Zi(mT-2} Jl-y,(mT2 cos{Zf+ fm+

+y2(mT2)sm(2F+)

Z2(mT 2)I.{y2i( nT2}cos()m

f- d

70)5 in(2/-)-1 ) m

где Z(mT2), Z2(mT2) - соответственно первый и второй групповые комплексные сигналы, являющиеся квадратурными составяющими комплексного группового сигнала

Z(m.T2) Z2(mT2)(fnT-2),

При поступлении управляющего У13 сигнала на вход счетчика 25 формируется соответствующее значение кода адреса f-й коммутируемой переменной 1/|,(тТа)на входе первого коммутатора и переменной ) на входе второго коммутатора 20. Текущее значение выборок ) и ) подается на первый вход первого и соответственно второго умножителя 21, на второй вход которых в этот же момент времени с выхода четвертого регистра 24 поступает соответствующее значение выборки косинусной составляющей / -и трансформирующей функции

exp{/( 1)) cos(2if+l)|-m+ +/sin(2/ +l)fm.

При соответствующем значении управляющего сигнала У16 полученные произведения

у1/(тГ2)соз{2/ -|-1)|-т и t/2XmT2)sin(2/+ + l)fm .

через первый и соответственно второй входы третьего и четвертого коммутаторов 20 подаются на первый вход первого и соответственно второго накапливающих сумматоров 22. При изменении уровня управляющего сигнала У15 на адресном входе блока 23 памяти коэффициентов с выхода последнего управляющим импульсом У14 в регистр 24 вводится соответствующее значение выборки синусной составляющей /-и трансформирующей функции той же частоты. Полученные на выходе первого и второго умножителей 21 произведения yiXm7 2)sin(2/4-l)|-

и соответственно /2/(m7 2)sin()|-m при изменении уровня управляющего сигнала У16 на входах третьего и четвертого коммутаторов 20 подаются на первые входы соответственно второго и первого накапливающих сумматоров 22. При этом четвертый коммутатор одновременно преобразует прямой код числа )s,m( 2:{- - m в обратный. Процесс накопления в сумматорах 22 заканчивается при поступлении и соответствующей обработке последней fe-й комбинации входных выборок: (tnT2) и y2k(tnTz). Полученный результат Z(mT2j и Z(mT 2) с выхода первого и соответственно второго накапливающих сумматоров 22 записывается в первый и соответственно второй регистры 24 управляющим импульсом У12. При подаче управляющего импульса содержание накапливающего сумматора 22 обнуляется. Формирователь группового сигнала готов к приему и обработке новой последовательности выборок сигналов (mT 2) и y2i(mT2).

Последовательность генерации выборок

соз(2 -4-1)-т и sin(2/ -f l)f-/n трансформирующей функции определяется схемой адресации первого блока 23 памяти коэффициентов, которая включает в себя (фиг. 5) третий умножитель 21, второй блок 23 памяти коэффициентов, третий и пятый регистры 24 и второй и третий счетчики 25. Во второй

0

5

°

5

0

5

0

5

блок 23 памяти коэффициентов априорно введены коды частот Qf, / 1, k трансформирующей функции формирователя (в рассматриваемом устройстве принято, что в/ (2/-|-1)я/fe, где 2k - период основной частоты генератора трансформирующей функции), которые последовательно выводятся в пятый регистр 24 подачей очередного управляющего импульса У13 на соответствующий вход третьего счетчика 25 и управляющего импульса У20 на вход пятого регистра 24. Второй счетчик 25, управляемый последовательностью импульсов У12, формирует код текущего значения числа т, взятого по модулю 2fe. Произведение чисел nimodik и в/, взятое по модулю 2, с выхода третьего блока 21 умножения записывается в третий регистр 24 управляющим импульсом У19 и подается на адресные входы первого блока 23 памяти коэффициентов.

Блок 4 (фиг. 6) включающий в себя коммутатор 26, блок 27 умножения, блок 28 памяти коэффициентов, счетчик 29 и регистр 30, реализует следующий алгоритм цифровой обработки

5,(т7-2) Z,(m72));

52(72) Z2(mTz)W(m), т О, L-l, где w(m) - L-мерный массив весовых коэффициентов.

Ввод последовательности выборок Z(mT2 Zi.(mT-i) в блок 4 выполняется через коммутатор 26 управляющим сигналом У21. При низком уровне управляющего сигнала У21 на первый вход умножителя 27 подводятся выборки Zi(m7 2), а при высоком уровне - выборки Zz(mTz). Соответствующие значения весовых коэффициентов W(rn), , L-1, поступающие на второй вход умножителя 27, считываются из блока 28 памяти коэффициентов, управляемого по адресным входам счетчиком 29. Новое значение блока 28 памяти формируется на выходе счетчика 29 при поступлении очередного управляющего импульса У12. После прихода в исходное нулевое состояние импульса У12 счетчик 29 переходит в исходное нулевое состояние и процесс весовой обработки повторяется для следующего L-мерного массива входных данных Zi(mT2), Z2(mT2), текущее значение выходных переменных Si(m7 2) и S2(mT2), разделенные по времени (фиг. 7), последовательно записываются в выходной регистр 30 управляющим импульсом У22 и поступают в блок БПФ по общему каналу.

При подаче совокупности управляющих сигналов У24-У42 (фиг. 7) блок 5 реализует вычисление коэффициентов Фурье L-мерного комплексного массива входных данных

S(mT2) S2(mT2) + /5,(тГ2)

по алгоритму быстрого преобразования Фурье.

Формула изобретения Цифровой анализатор спектра, содержащий преобразователь частоты, выходы си

нуснои и косинусной составляющих i-и частоты (/ 1, k, k - количество анализируемых частот) которого подключены к входам г -х цифровых фильтров соответственно первой и второй групп, блок умножения, выход которого подключен к информационному входу блока вычисления дискретного преобразования Фурье, выход которого является информационным выходом анализатора, ин- формационым входом которого является вход преобразователя частоты, отличающий- ся тем, что, с целью повышения быстродействия, в него введены четыре коммутатора, три счетчика, пять регистров, два накапливающих сумматора, три умножителя и два блока постоянной памяти, причем выходы /-Х цифровых фильтров первой и второй групп подключены к /-м информационным входам соответственно первого и второго коммутаторов, выходы которых подключены к первым входам соответственно первого и второго умножителей, выходы которых подключены соответственно первого - к первым информационным входам третьего и четвертого коммутаторов, второго - к вторым информационным входам третьего и четвертого коммутаторов, выходы которь(х подключены к входам соответственно первого и второго накапливающих сумматоров, выходы которых подключены к информационным входам соответственно первого и второго регистров, выходы которых подключены соответственно к первому и второму входам блока умножения, информационный выход первого счетчика подключен к управляющим входам первого и второго коммутаторов, информационный выход второго счетчика

,)

5

Q

0

5

подключен к первому входу третьего умножителя, выход которого подключен к информационному входу третьего регистра, выход которого подключен к адресному, входу первого блока постоянной памяти, выход которого подключен к информационному входу четвертого регистра, выход которого подключен к вторым входам первого второго умножителей, информационный выход третьего счетчика подключен к адресному «ходу второго блока постоянной памяти, выход которого подключен к информационному входу пятого регистра, выход которого подключен к второму входу третьего умножителя, установочные входы второго и третьего счетчиков, первого и второго регистров объединены и являются первым установочным входом анализатора, счетные входы первого и третьего счетчиков объединены и являются первым тактовым входом анализатора, тактовый вход четвертого регистра является вторым тактовым входом анализатора, вход чтения второго блока постоянной памяти является третьим тактовым входом анализатора, управляющие входы третьего и четвертого коммутаторов объединены и являются четвертым тактовым входом анализатора, тактовые входы первого и второго накапливающих сумматоров объединены и являются пятым тактовым входом анализатора, вторым установочным входом которого являются объединенные между собой установочные входы первого и второго накапливающих сумматоров, а тактовые входы третьего и пятого регистров являются соответственно шестым и седьмым тактовыми входами анализатора.

)

фиг.1

/770С/А// , /7/„ос/ - V - //7/770(/ -- /770а О

Фиг4

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор спектра случайныхпРОцЕССОВ | 1979 |

|

SU838600A1 |

| Цифровой анализатор спектра | 1981 |

|

SU974374A1 |

| Цифровой синтезатор сигналов | 1984 |

|

SU1224949A1 |

| Устройство для обработки данных при формировании диаграммы направленности антенной решетки | 1987 |

|

SU1462351A1 |

| Цифровой многофазный преобразователь мощности в частоту | 1989 |

|

SU1707557A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1997 |

|

RU2137287C1 |

| Цифровой анализатор спектра | 1979 |

|

SU798615A1 |

| Адаптивный коррелометр | 1977 |

|

SU732887A1 |

| Цифровой нерекурсивный фильтр | 1983 |

|

SU1124430A1 |

| Цифровой нерекурсивный фильтр | 1985 |

|

SU1352622A1 |

Изобретение относится к специализированным средствам вычислительной те.ч- ники и может быть использовано при цифровом спектральном анализе многочастотных узкополосных радиосигналов, сигналов связи и управления. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что анализатор спектра содержит преобразователь частоты, две группы цифровых фильтров, блок умножения, блок вычисления дискретного преобразования Фурье, четыре коммутатора, три счетчика, пять регистров, два накапливающих сумматора, три умножителя и два блока постоянной памяти с соответствующими связями. 7 ил. (С Ю СП 05 О 4;а 4

сриг.7

| Витязев В | |||

| В., Степашкнн А | |||

| И Синтез структуры цифрового спектрального анализатора с использованием набора фильтров- дискретизаторов | |||

| В кн.: Методы представления и аппаратурный анализ случайных процессов и полей | |||

| Л., 1980 | |||

| Цифровой анализатор спектра | 1981 |

|

SU974374A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-09-07—Публикация

1985-02-19—Подача