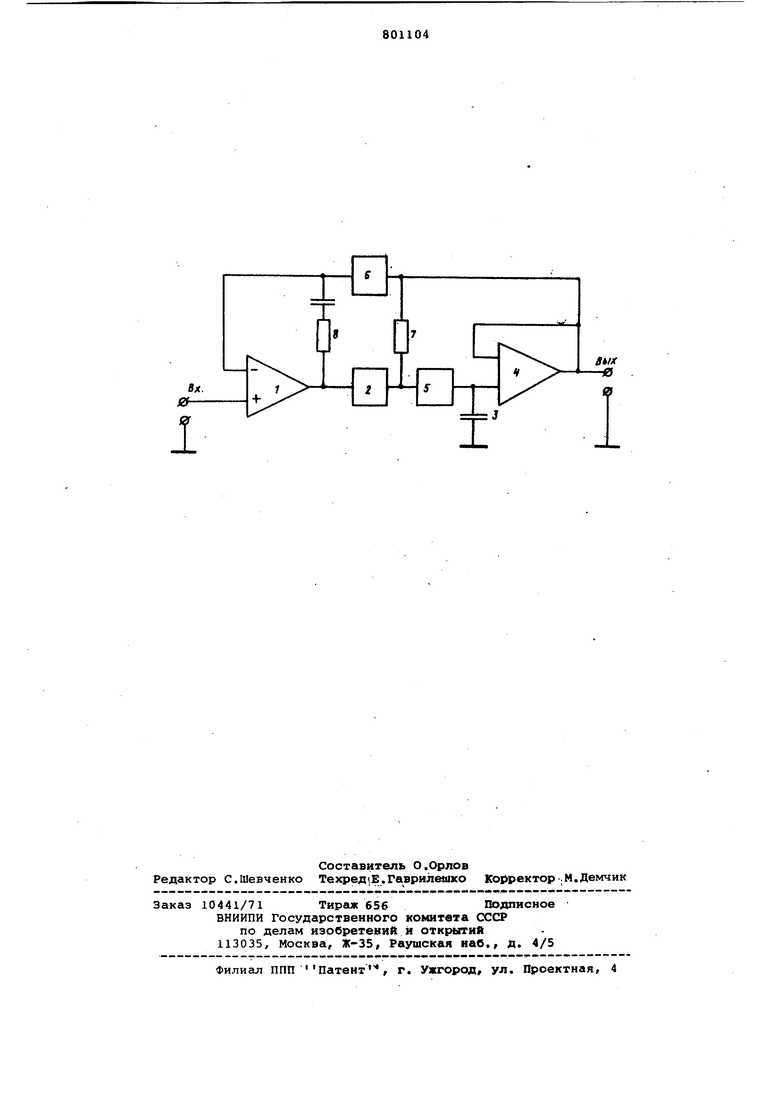

Изобретение относится к вычислительной технике и может быть использовано, например в контрольно-измерительных приборах. известно запоминающее устройство, содержащее входной и выходной усилители, переключающие элементы и запоминающую емкость 1. Недостатком этого устройства явля ется большой уровень коммутационных помех, что не позволяет использовать такие запоминающие устройства в изме рительных устройствах систем обработ ки информации. Наиболее близким к предлагаемому .являемся аналоговое запоминающее уст ройство, содержащее три ключа,; входной и выходной операционные усилители, запоминающую емкость, выход вход ного .операционного усилителя соедине через последовательно соединенные первый и второй ключи со входом выходного операционного усилителя и одной из обмоток запоминающей емкости на входе выходного операционного усилителя 2. Недостатком этого устройства явля ется недостаточная точность. Цель изобретения - повышение точности устройства. Поставленная цель достигается тем, что в аналоговом запоминакицем устройстве, содержащем три ключа, входной и выходной операционные усилители, накопительный элемент, выход входного операционного усилителя подключен через последовательно соединенные первый и второй ключи ко входу выходного операционного усилителя и одному из выводов ; накопительного элемента, другой вывод которого подключен к шине нулевого потенциала, выход третьего ключа подключен к инвертирующему входу входного операционного усилителя, а вход - к выходу выходного операционного усилителя, в него введены резистор и RC-цепочка, вход которой подключен к выходу входного операционного усилителя, а выход к выходу третьего ключа, один вывод резистора подключен к выходу первого ключа, другой вывод - ко входу третьего ключа. На чертеже изображена блок-схема аналогового запоминающего устройства. Аналоговое запоминающее устройство состоит из входного операционного усилителя 1, первого ключа 2, запоминающей емкости (конденсатор) 3, выходного операционного усилителя 4,

второго ключа 5, третьего ключа 6, реэцстора 7 и RC-цепочки 8.

Устройство работает следующим образом.

Входное напряжение подается на неинвертирукхдий вход входного операционного усилителя. В режиме выборкЦ ключк 3, 5, 6 замкнуты, при этом напряжемм на накопительном элементе повторяет входное напряжение с учетом коэффициента передачи выходного операционного усилителя (повторителя) 4 и ключа б. Напряжение обратной связи снимается с-выхода устройства, что исключает разряд накопительного элемента по цепи обратной связи в режиме хранения, снижает требования к величине коэффициента передачи повторителя 4 и входного сопротивления входного операционного усилителя. Погрешностью от падения напряжения на открытом ключе 6 можно пренебречь, если обеспечить достаточно высокое входное сопротивление входного операционного усилителя на инвертирующем входе (свьлие 100 кОм) по сравнению с сопротивлением открытого клю.ча 6. Через RC-цепочку поддерживается обратная связь по переменному току на инвертирующий вход входного операционного усилителя во время нахождения ключей в состоянии неопределенности при их коммутации. На время выборки действие RC-цепочки блокируется через открытый ключ 6 выходным сопротивлением выходного операционного усилителя (повторителя) 4. Активное сопротивление НС-цепочки должно быть на 2-3 порядка выше сопротивления открытого ключа б, постоянная времени определяется временем действия коммутационных помех. При переходе к режиму хранения ключи 2, 5, 6 размыкаются и ча накопительном элементе фиксируется напряжение, установившееся к концу выборки до размыкания ключей. Через резистор 7 с выхода, повторителя 4 на вход ключа 5 подается напряжение, обеспечивакицее выравниваннв потенциалов на его входе и выходе. Это исключает погрешность, вызванную разрядом накопительного эле еыт1В1 через обратное сопротивление закрытогоключа в режиме хранения. Величина сопротивления резистора 7 определяется из условия допустимой нагрузки в цепи выхода входного one рационного усилителя. Погрешность, вызванная влиянием резистора 7 в режиме выборки убирается цепью .отрицательной обратной связи.

Введение RC-цепочки и резистора, а также новых связей в предлагаемое запоминающее устройство приводят к уменьшению сигнала помехи и Динамической погрешности. Экспериментальная проверка устройства как в виде отдельного макета, а также в составе информационной измерительной системы показала, что переходные помехи и динамическая погрешность уменьшены в 2-3 раза по сравнению с известными аналоговыми запоминающими устройствами. Надежность работы и время запоминания устройства повысилась, так как исключены импульсные помехи во время обращения непосредственно к адресуемой ячейке или соседним, время хранения .информации в каждой из ячеек памяти равно 5-7 с, погрешность хранения информации за это время равна Ojl± :f 10 MB..

Формула изобретения

Ансшоговое запоминающее устройство содержащее три ключа, входной и выходной операционные усилители, накопительный элемент, выход входного операционного усилителя подключен через последовательно соединенные первый и второй ключи ко входу выходного операционного усилителя и одному из выводов накопительного элемента, другой вывод которого подключен к шине нулевого потенциала, выход третьего ключа подключен к инвертирующему входу входного операционного усилителя, а вход - к выходу выходного операционного усилителя, отличающеес я тем, что, с целью повышения точности устройства, в него введены резистор и RC цепочка, .вход которой подключен к выходу входного операционного усилителя, а выход - к выходу третьего ключа, один вывод резистора подключен к выходу первого ключа, другой вывод - ко входу третьего ключа.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР №548008, кл. G 11 С 27/00, 1.975.

2.Авторское свидетельство СССР 461454, кл. G 11 С 27/00, 1973 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналоговое запоминающее устройство | 1979 |

|

SU830584A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1065889A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРИОД - НАПРЯЖЕНИЕ | 1991 |

|

RU2030108C1 |

| Аналоговое запоминающее устройство | 1986 |

|

SU1484163A1 |

| Аналоговое запоминающее устройство | 1987 |

|

SU1548813A1 |

| Аналоговое запоминающее устройство | 1978 |

|

SU767844A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU978200A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРИОДИЧЕСКОГО СИГНАЛА В ЧАСТОТУ И ПЕРИОД | 2012 |

|

RU2520409C2 |

| Аналоговое запоминающее устройство | 1989 |

|

SU1691895A1 |

| Аналоговое запоминающее устройство | 1987 |

|

SU1531173A1 |

Авторы

Даты

1981-01-30—Публикация

1979-03-20—Подача