(54) УСТРОЙСТВО РЕГЕНЕРАЦИИ СИНХРОИМПУЛЬСОВ

ПОЛЕЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ТЕЛЕВИЗИОННОГО ВЕЩАНИЯ С ЗАЩИТОЙ ОТ НЕСАНКЦИОНИРОВАННОГО ПРИЕМА И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2013024C1 |

| Программируемый трансверсальный фильтр | 1988 |

|

SU1651354A1 |

| Устройство для регистрации динамических процессов | 1989 |

|

SU1702358A1 |

| Устройство для селекции изображений | 1991 |

|

SU1837335A1 |

| УСТРОЙСТВО КАДРОВОЙ СИНХРОНИЗАЦИИ | 1972 |

|

SU432689A1 |

| МНОГОМЕРНАЯ СИСТЕМА ТЕЛЕМЕХАНИКИ | 1989 |

|

RU2020594C1 |

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| Замкнутая телевизионная система для измерения объектов | 1987 |

|

SU1412004A1 |

| Устройство для селекции элементов телевизионного изображения | 1983 |

|

SU1256054A1 |

| Устройство поэлементной синхронизации | 1987 |

|

SU1517142A1 |

1

Изобретение относится к радио , технике и может использоваться в приемниках совмещенного телевизион ного сигнала и синхрогенераторах.

Известно устройство регенерации синхроимпульсов полей, состоящее из последовательно соединенных селектора кадровых синхроимпульсов, блока фазирования, счетчика и формирователя импульсов l| .

Однако известное устройство недостаточно помехоустойчиво, так как не имеетсредств защиты от появления ложных и искаж1енных импульсов. Цель изобретения - повышение помехоустойчивости путем устранения ложных и искаженных импульсов в режиме быстрого фазирования.

Указанная цель достигается тем, что в устройство введен анализатор синхронизма, содержащий коммутатор, нецнвертирующий и инвертирующий элементы памяти, триггер задержки н бло совпадения, при этом первый сравнивающий вход коммутатора подключен к выходу селектора кадровых синхроимпульсов , второй сравнивающий вход - к выходу формирователя импульсов , первый и второй выходы коммутатора подключены, соответственно

к информационным входам неинвертирующего и инвертирующего элементов памяти, выходы которых, а также, выход триггера задержки подключены ко входам блока совпадения, выходом соединенного ,с информационным входом триггера задержки, причем обнуляющие входы каждого элемента памяти и тактовый вход триггера задержки подклю0чены к тактовому выходу формирователя импульсов, выход инвертирующего .элемента памяти подключен к запрещающему входу формирователя импульсов, а выход триггера задержки под5соединен к запрещающему входу блока фазирования и к разрешающему входу формирователя импульсов.

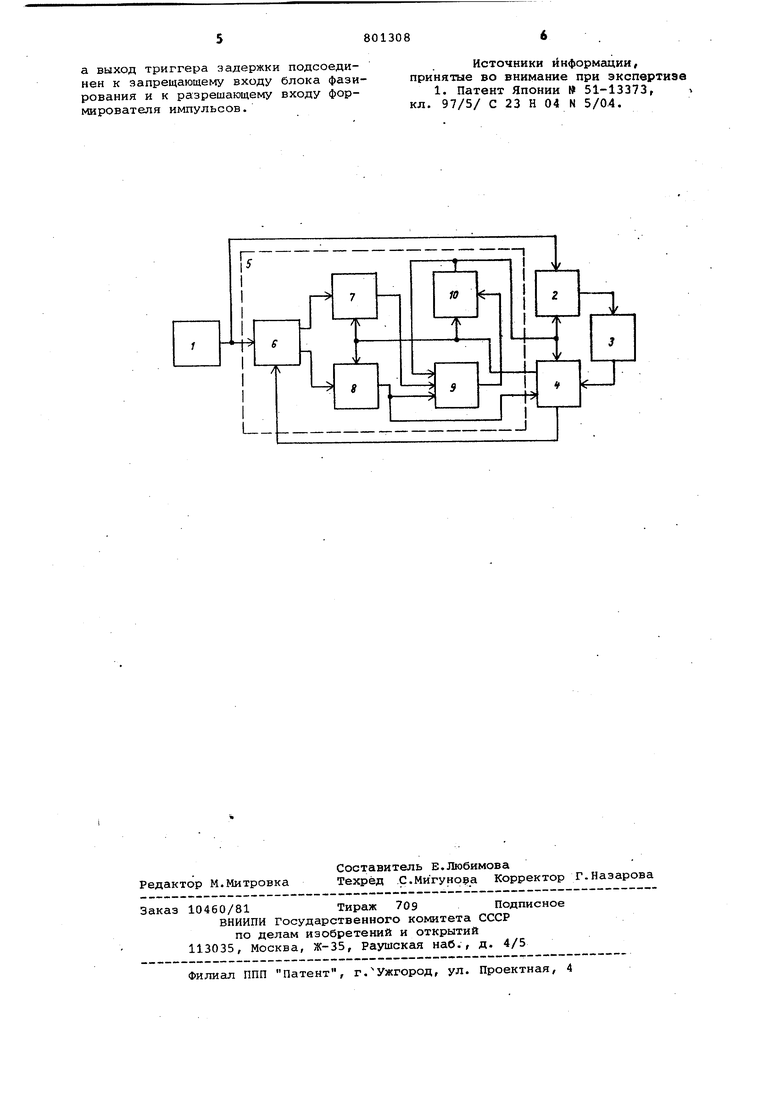

, На чертеже представлена структур0ная электрическая схема предлагаемого устройства.

Устройство регенерации синхроимпульсов полей содержит селектор 1 кадровых синхроимпульсов, блок 2 фа5зирования, счетчик 3, формирователь 4 импульсов г анализатор 5 синхронизма, содержащйй коммутатор 6, неинвертирующий и инвертирующий элементы 7 и В памяти, блок 9 совпадения и

а триггер 10 задержки. Устройство работает следующим образом. Действующий на выходе селектора 1 импульс установки, соответствующий моменту появления кадрового синхроимпульса входного телевизионного сиг нала , поступает на первый сравнивающий вход а ализатора 5 и вход 2. Ври наличии нулевого сигнала на запрещающем входе блока 2 импульс установки фиксирует такое состояние счетчика 3, при котором импульс, вырабатываемый формирователем 4 на втором сравнивающем входе анализатора 5,-занимает ту же временную позицию в цикле работы счетчика 3, что и импульс установки. Таким образом, достигается быстрое совпадениепо фазе между входным телевизионным сигналом и регенерированными импульсагли частоты полей, которые вырабаты ваются формирователем 4. Формирователь 4 наряду с обычными входами, которые подключены к разрядам счетчика 3, имеет дополнитель ный разрешающий вход. При подаче на этот вход нулевого сигнала запрещается формирование импульсов частоты полей на соответствующих выходах формирователя 4, На тактовом выходе формирователя 4, соединенном с такто вым входом анализатора 5, импульс, соответствующий началу цикла работы счетчика 3, вырабатывается независиМО от состояния сигнала на разрешающем входе формирователя 4. Этот импульс является тактовым для анализатора 5, и только при появлении его происходит изменение сигнала на запрещающем входе блока 2 и разрешающем входе формирователя 4. Таким образом достигается согласованное изменение сигнала на всех входах формирователя 4, что исключа ет возможность возникновения какихлибо ложных импульсов в момент изме нения сигнала на разрешающем входе. При этом в калодом цикле работы счет чика 3, о ватывающем интервал време ни между двумя соседними тактовыми импульсами, имеются только две возможности , соответствующие определен ному уровню сигнала На разрешающем входе формирователя 4 и соединенном с ним запрещающем входе блока 2. Если в Данном -цикле работы счетчика 3 этот сигнал имеет единичный уровень, то блок 2 блокируется, импульсы установки не поступают на счетчик 3 и возможность появления ложны и искаженных импульсов из-за наруше ния последовательности переключения разрядов счетчика 3 исключается Если же сигнал на разрешающем входе формирователя 4 имеет нулевой уровень, то происходит перефазировка счетчика 3, однако ложные и искажен-, ные импульсы, которые могут позникнуть вследствие нарушения последовательности срабатывания разрядов счетчика 3, устраняются благодаря действию на разрешающем входе формирователя 4 нулевого сигнала, который блокирует соответствующие выходы формирователя 4. В первом из. рассматриваемых случаев устройство работает в режиме формирования, а во втором - в режиме фазирования. Перевод устройства из одного режима в другой производится анализатором 5, который в каждом цикле работы счетчика 3 оценивает временное положение импульсов установки. G этой целью в каждом цикле с помощью коммутатора б производится распределение импульсов установки селектора 1 на неинвертйрующий и инвертирующий элементы 7 и 8 памяти, причем если импульс установки совпадает по времени с импульсом на втором сравнивающем входе анализатора 5, то он попадает на инвертирующий элемент 8 памяти, если же такого совпадения нет, то импульс установки подается на неинвертирующий элемент 7 памяти. Формула изобретения Устройство регенерации синхроимпульсов полей, состоящее из последовательно соединенных селектора кадровых синхроимпульсов, блока фазирования, счетчика и формирователя импульсов, отличающееся тем, что, с целью повышения помехоустойчивости путем устранения ложных и искаженных импульсов в режиме быстрого фазирования, в него введен анализатор синхронизма, содержащий коммутатор, неинвертирующий и инвертирующий элементы памяти, задержки и блок совпадения, при этом первый сравнивающий вход коммутатора подключен к выходу селектора кадровых синхроимпульсов, второй сравнивающий вход - к выходу формирователя импульсов, первый и второй выходы коммутатора подключены, соответственно, к информационным входам неинвертирующего и инвертирующего элементов памяти, выходы которых, а также выход триггера задержки подключены ко входам блока совпадения, выходом соединенного с информационным входом триггера задержки, причем обнуляющие входы каждого элемента памяти и тактовый вход триггера задержки подключены к тактовому .вцходу формирователя импульсов, выход инвертирующего эле.мента памяти подключен к запрещающему входу формирователя импульсов.

а выход триггера задержки подсоединен к запрещающему входу блока фазирования и к разрешающему входу формирователя импульсов.

Источники информации, принятые во внимание при экспертизе 1. Патент Японии 51-13373, кл. 97/5/ С 23 Н 04 N 5/04.

Авторы

Даты

1981-01-30—Публикация

1979-04-02—Подача