Вх

эл-ты И-НЕ 5 и 10, эл-ты И 6, 7 н 9, эл-т ИЛИ 8, эл-т НЛИ-НЕ 11,К-триггер 12, управляемый счетчик 14, блок выбора 18 режима работы, блок 22 дискретной фазовой автоподстройки, блок коррекции 37 и задающий г-р 45, Цель достигается за счет коррекции положения синхроимпульса во время перерывов связи в соответствииеизмеренными в течение сеанса связи скоростью и направлением вызванного расстройкой

перемещения действительных границ элементарных посылок. Погрешность коррекции не превышает to /8 ( о д - длительность принимаемых элементарных посыпок). Поэтому после окончания перерыва св.чзи фаза синхроимпульсов с достаточно высокой точностью соответствует действительной фазе принимаемых посылок, и сбоев поэлементной , и цикловой синхронизации не происхо- дит, 2 з,п, ф-лы, 2 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| Устройство поэлементной синхронизации | 1981 |

|

SU987834A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство для фазовой синхронизации | 1983 |

|

SU1149425A2 |

| Устройство для автоподстройки частоты | 1988 |

|

SU1653159A1 |

| Устройство тактовой синхронизации | 1987 |

|

SU1555892A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ФАЗОВОЙ СИНХРОНИЗАЦИИ | 2004 |

|

RU2267221C1 |

| Устройство тактовой синхронизации | 1989 |

|

SU1720162A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

Изобретение относится к радиосвязи. Цель изобретения - повышение помехоустойчивости путем обеспечения безобрывности связи при расстройке частот задающих г-ров передатчика и приемника и снижения погрешности синхронизации. Устройство содержит Д-триггеры 1 и 13, селектор 2 фронтов, счетчик 3, делители 4 и 46 частоты, эл-ты И-НЕ 5 и 10, эл-ты И 6,7 и 9, эл-т ИЛИ 8, эл-т ИЛИ-НЕ 11, R - триггер 12, управляемый счетчик 14, блок выбора 18 режима работы, блок 22 дискретной фазовой автоподстройки, блок коррекции 37 и задающий г-р 45. Цель достигается за счет коррекции положения синхроимпульса во время перерывов связи в соответствии с измеренными в течение сеанса связи скоростью и направлением вызванного расстройкой перемещения действительных границ элементарных посылок. Погрешность коррекции не превышает τ0/8 (τ0 - длительность принимаемых элементарных посылок). Поэтому после окончания перерыва связи фаза синхроимпульсов с достаточно высокой точностью соответствует действительной фазе принимаемых посылок, и сбоев поэлементной и цикловой синхронизации не происходит. 2 ил.

Изобретение относится к технике электро- и радиосвязи и может быть использовано в системах передачи и приема цифровой информации в каналах с замираниями или длительными комму- тащюнными помехами.

Цель изобретения - повышение помехоустойчивости путем обеспечения без- обрывности при расстройке частот задающих генераторов передатчика и приемника и снижения погрешности синхронизации.

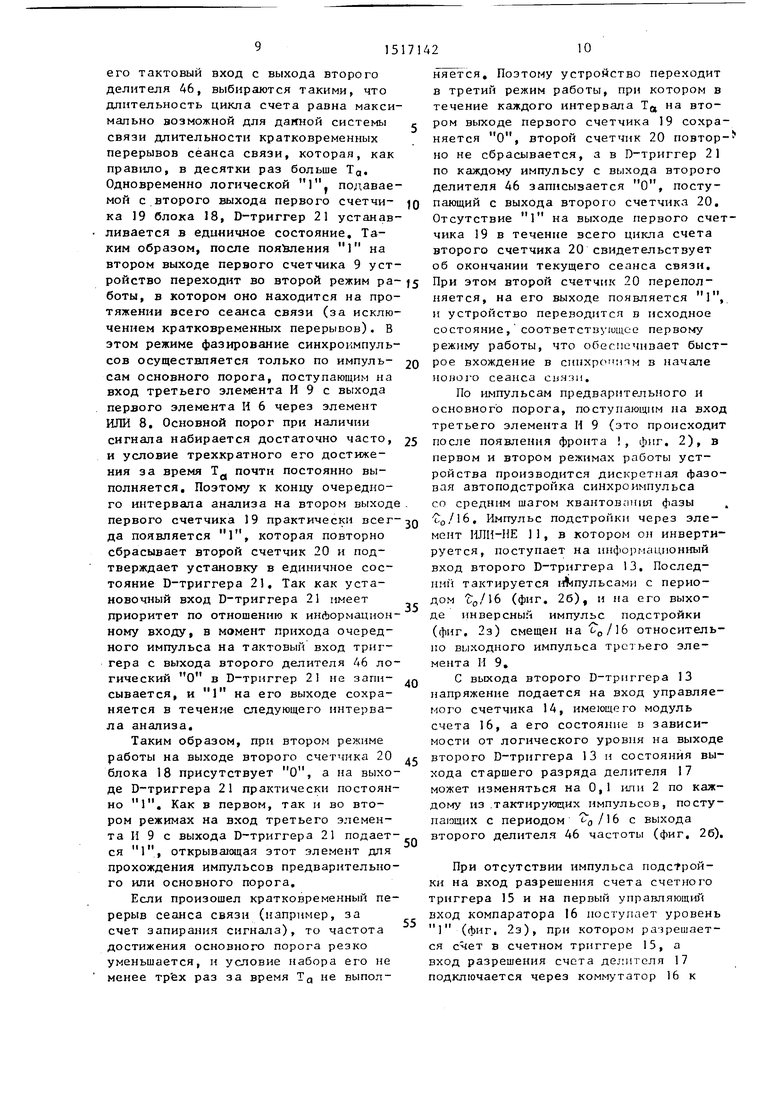

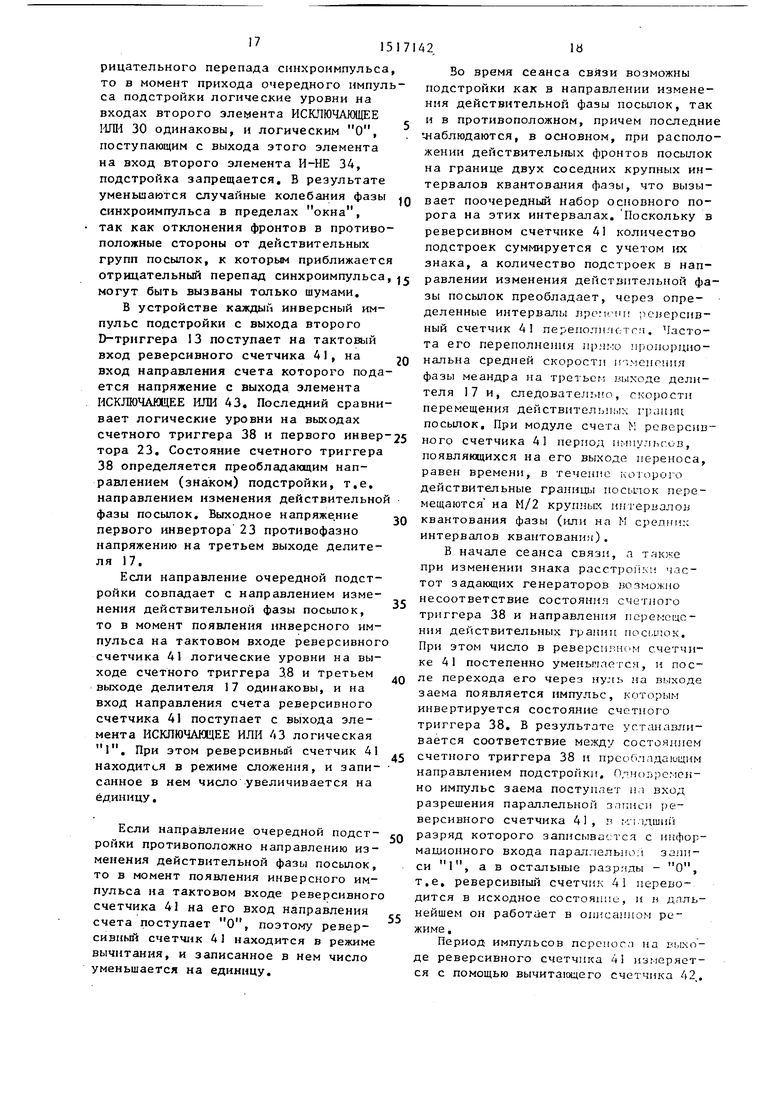

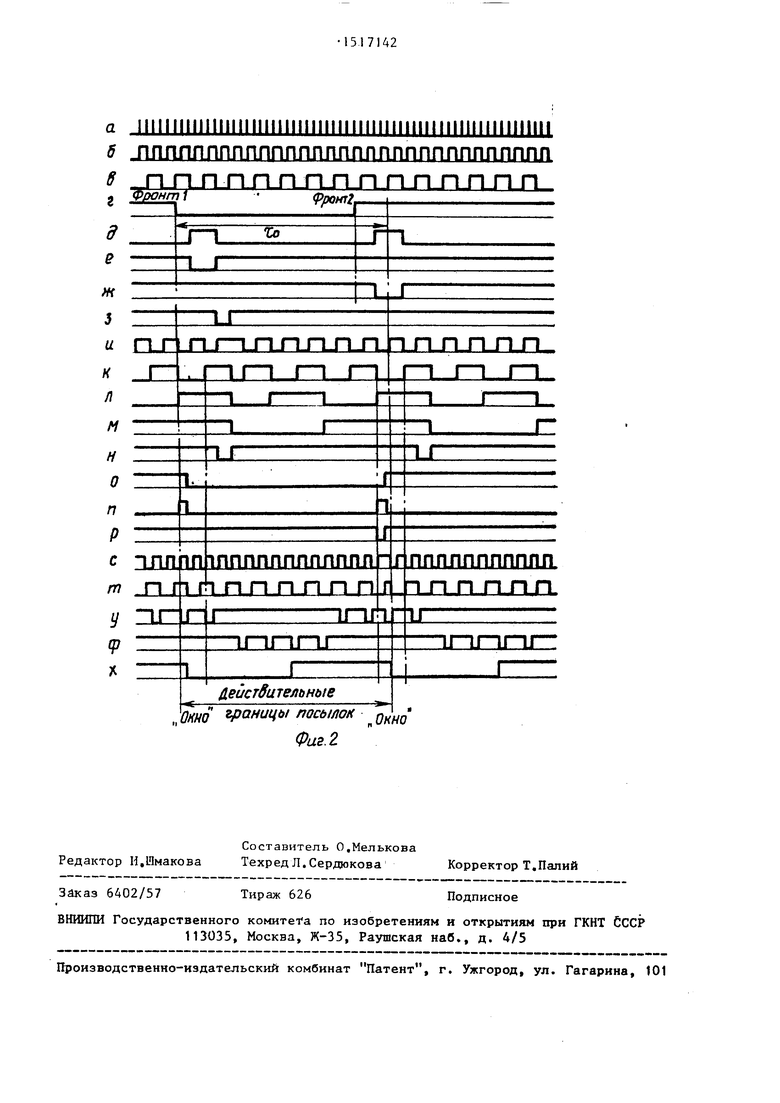

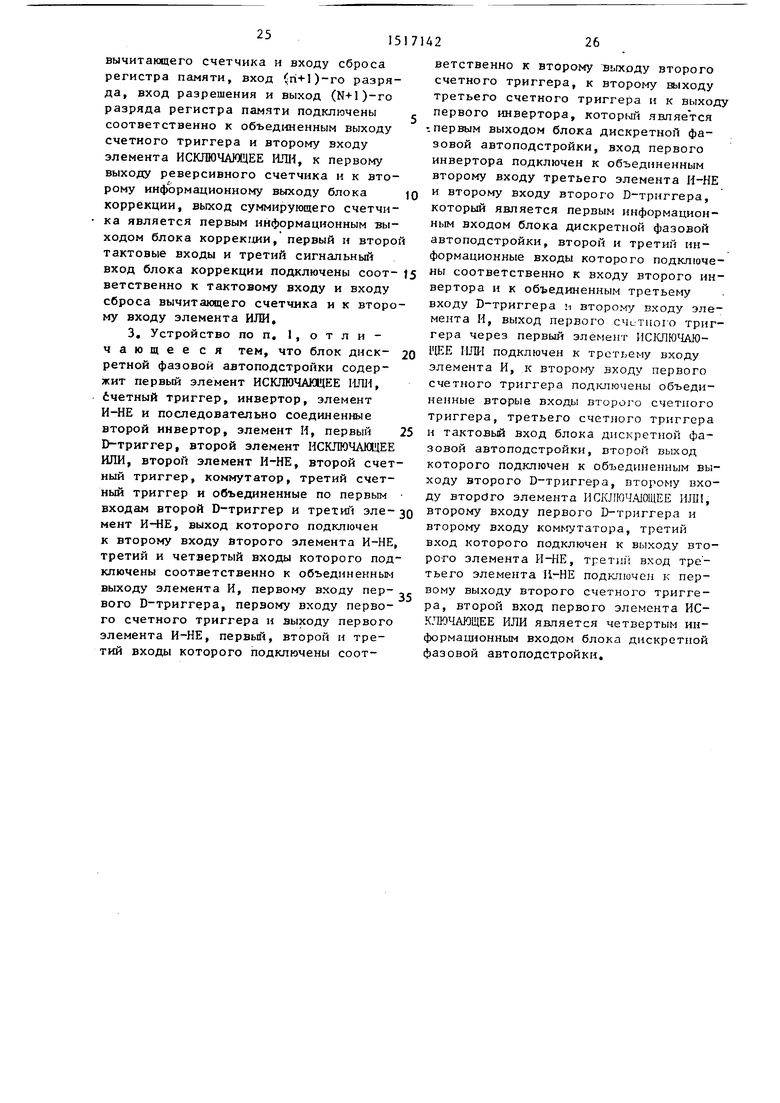

На фиг, 1 приведена функциональная схема устройства поэлементной синхронизации; на фиг, 2 - диаграмма состояний элементов устройства.

Устройство поэлементной синхронизации содержит первый D-триггер 1, селектор 2 фронтов, счетчик 3, первый делитель 4 частоты,- первый элемент Н-ИЕ 5, первый 6 и второй 7 элементы И, элемент ИЛИ 8, третий элемент И 9, второй элемент И-НЕ 10, элемент ИЛИ- НЕ 11, R-триггер 12, второй D-триггер 13, управляемый счетчик 14, состоящий из счетного триггера 15, коммутатора 16 и делителя 17 частоты, блок 18 выбора режима работы, состоящий из первого 19 и второго 20 счетчиков и D-триггера 21, блок 22 дискретной, фазовой автоподстройки, состоящий из первого 23 и второго 24 инверторов, первого элемента И 25, первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 26, первого счетного триггера 27, первого 1 -триггера 28, первого элемента И-НЕ

29,второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ

30,коммутатора 31, второго 32 и третьего 33 счетных триггеров, второго элемента И-НЕ 34, второго D-триггера 35 и третьего элемента И-НЕ 36, блок

0

5

0

5

0

5

0

5

37 коррекции, содержащий счетный триггер 38,. суммирующий счетчик 39, элемент ИЛИ 40, реверсивный счетчик 41, вычитающий счетчик 42, элемент ИСКЛЮ- ЧАЮ(ЦЕЕ ИЛИ 43 и регистр 44 памяти, задающий генератор 45 и второй делитель 46 частоты.

Устройство работает следующим образом.

Принимаемые элементарные посылки длительностью t с выхода порогового устройства демодулятора поступают на информационный вход первого D-триггера 1, на тактовьй вход которого с выхода задающего генератора 45 подаются импульсы (фиг, 2а) с периодом в 32 раза меньше длительности посыпки. Эти импульсы делят элементарную посылку на 32 мелких интервала квантования фазы, В первом D-триггере 1 осуществляется привязка границ посылок (фронтов) к началу ближайшего мелкого интервала квантования, (фиг, 2г). Селектор 2 по каждому фронту выходного напряжения первого D- триггера 1 формирует импульсы (фиг,2д) длительностью, равной крупному щагу квантования фазы S, /8, Крупный шаг квантования фазы задается импульсами, поступающими с периодом на тактовый вход селектора 2 (фиг, 2в) с второго выхода второго делителя 46 частоты. Импульс на выходе селектора 2 формируется на ближайщем после поступившего фронта крупном интервале квантования (фиг, 2г,д), поэтому он оказывается задержанным на t /8 относительно крупного интервала квантования, соответству1шдего фронту. Например, если на выходе первого D- триггера 1 фронт посылки появился на

515

k-M крупном интервале квантования фазы, то селектор 2 формирует импуль на (k+l)-M интервале,

С выхода селектора 2 импульс пос- тупает на вход сброса первого делителя 4 с коэффициентом деления восемь, при этом осуществляется запоминание фазы очередного фронта путем синхронного сброса первого делителя 4, на выходе которого после сброса формируются инверсные импульсы длительность (,/8 (фиг, 2е), следующие с периодом tg и синфазные с импульсом сброса. Сброс является синхронным (фиг. 2е), так как он производится при наличии логической I на выходе селектора 2 (фиг, 2д) в момент прихода на тактовый вход первого делителя 4 очередного импульса с выхода второго делите- ля 46,

Если очередной и предыдущ1:й фронты синфазны с точностью до tg /8 (т,е. они попадают в один крупньй интервал квантования фазы), то импульс на вы- ходе селектора 2 появляется одновременно с инверсным импульсом на выходе первого делителя 4 (фиг. 2д,е, фронт 1 фиг, 2г) и на выходе второго элемента И-НЕ 10 сохраняется логическая 1 (фиг, 2ж). При этом счетчик 3 находится в режиме счета выходных импульсов селектора 2 и записанное в нем число увеличивается на единицу после прихода каждого фронта, сии- фазного с предыдущими.

Если очередной и предыдущий фрон- Tbi попадают в разные крупные интервалы квантования фазы, то на выходе второго элемента И-НЕ 10 появляется о . (фиг, 2ж, фронт 2 фиг. 2г), который сбрасывает счетчик 3. Таким образом, счетчик 3 подсчитывает число синфазных фронтов, следующих подряд. Когда это число достигает емкости счетчика 3, на его выходе появляется 1, а дальнейш:-й счет прекращается, Данное состояние сохраняется до тех пор, пока не произойдет сброс счетчика 3, т,е, пока не поступит фронт, попадающий в другой крупный интервал квантования фазы посылки,

Синхроимпульс в устройстве вырабатывается в пределах крупного интервала квантования фазы, которому соот- ветствует определенное количество следующих подряд синфазных фронтов, превышающее заданной порог. Начальная синхронизация осущестапается при

426

достижении достаточно низкого предварительного порога, а надежная синхронизация - при достижении сравнительно высокого основного порога. Фазирование синхроимпульса по предварительному порогу обеспечивает в начале сеанса связи уменьшение времени синхронизации благодаря быстрому набору предварительного порога даже при не- больаих отношениях сигнал/шум. Достижению предварительного порога, который равен двум, соответствует наличие 1 на выходе второго элемента Н-НЕ 10 в момент появления импульса на выходе селектора 2, Данная комбинация выявляется с помощью второго элемента И 7, на первый и второй входы которого поступают выходные сигналы селектора 2 и второго элемента И-НЕ 10.

Основной порог в устройства выбирается равным, например, восьми. Емкость счетчика 3 на единицу меньше основного порога. Если семь следующих подряд фронтов посылок имеют одинаковую фазу, то на выходе счетчика 3 появляется 1. При совпадении фазы и восьмого фронта с предыдущими на втором и третьем входах первого элемента И 6 в момент появления импульса на выходе селектора 2 присутствуют 1, и этот импульс проходит через первый элемент И 6 (достигнут основной порог). Положение импульса с точностью до крупного шага квантования фазы совпадает с действительной фазой посылок, сдвинутой на один крупный шаг квантования (за счет задержки в селекторе 2). При постугшении каждого последующего фронта (девятого, десятого и т,д,), имеющего такую же фазу, как и предыдущие, импульсы на вьлоде первого элемента И 6 повторяются, что соответствует многократному достижению основного порога,

Частота достижения осноьиого порога характеризует качество связи: чем больше отношение сигнал/шум, тем меньше отклонение гра1гиц посылок от но шнального положения и чаще достигается основной порог, В устройстве наличие принимаемого сигнала фиксируется по числу достижений основного порога в течение заданного интервала времени. Необходимое число достижений основного порога может быть выбрано равным трем, а интервал времени

анализа TQ

10

. Подсчет количества импульсов основного порога, пос- тупаго цих с выхода первого элемента И 6, производится с помощью первого счетчика 19 блока 18 емкостью три, на вход сброса которого подаются импульсы с выхода второго делителя 46 частоты, имеющие период следования „

В исходном состоянии (после импульса сброса) на первом выходе- первого

счетчика 19 блока 18 присутствует 1, а на втором - О, Если после очередного импульса сброса первого счетчика 19 входа 18 хотя бы один раз был набран основной порог, то на первом выходе первого счетчика 19 блока 18 появляется О, который сохраняется до следующего импульса сброса. Если основной порог был наб- рлн три и более раз, то на втором выходе первого счетчика 19 блока 18 появляется 1, В момент прихода следующего импульса сброса первый счетчик 19 блока 18 обнуляется, и на его первом выходе устанавливается 1, а на втором - О,

Состояния блока 18 зависят от уровня принимаемого сигнала, определяют один из трех возможных режимов работы устройства: синхронизация по предварительному порогу в начале сеанса связи, синхронизация по основному порогу и запрет синхронизации по предварительному порогу при достаточно хорошем качестве связи и запрет синхронизащда как по предварительному, так и по основному порогам и коррекция фазы синхроимпульсов в течение кратковременных перерывов связи.

Перед началом сеанса связи, когда на входе демодулятора имеются только щумы, фронты поступают па вход устройства поэлементной синхронизации в случайные моменты времени. При этом устройство работает в первом режиме, предварительний порог набирается сравнительно редко, а основной порог во много раз реже предварительного (примерно один раз за время 10 ) Трехкратное достижение основного порога в течение интервала времени TQ при отсутствии сигнала является практически невозможным событием. Поэтом на втором выходе первого счетчика 19 присутствует О, а второй счетчик 20 находится в состоянии переполнения, при котором на его выходе имеется 1, которая записывается в В-триг

Q р

5

0

5

гер 21 в момент прихода очередного импульса с выхода второго делителя iG На третий и четвертый входы второго элемента И 7 поступают 1, в результате разрешается синхронизация по предварительному порогу.

После появления сигнала предварительный порог быстро достигается на том крупном интервале квантования фазы, которому соответствует действи- тельное положение границ посыпок, или на одном из соседних интервалов. При каждом достижении предварительного порога- на выходе второго элемента И 7 появляется импульс, который поступает через первый элемент -ШИ 8 на вход третьего элемента И 9, Так как набор предварительного порога даже при небольших отношениях сигнал/шум повторяется очень часто, правипьная синхронизация достигается еще до достижения основного порога.

Через некоторое время набирается основной порог, с выхода первого элемента И 6 на тактовый вход первого счетчика 19 поступает импульс, и на первом выходе этого счетчика появляется напряжение логического О, которое закрывает второй элемент И 7 и запрещает синхронизащ-но по предварительному порогу. Однако данный запрет является кратковременным и сохраняется только до конца интервала анализа числа достижений основного порога, т.е, до очередного импульса с выхода второго делителя 46, Ограничение времени запрета при однократном наборе основного порога позволяет избежать нарушения работы устройства из-за случайных наборов основного порога в отсутствие сигнала. Если за это время основной порог не достигнут еще два раза, то синхронизация по предварительному порогу вновь разрешается после сброса первого счетчика 19 и установления на его первом выходе 1,

ЕСЛИ за время Т основной порог достигается не менее трех раз, то на втором выходе первого счетчика 19 появляется 1, которая сбрасывает второй счетчик 20, и на его выходе устанавливается уровень О, запре- синхронизацию по предварительному порогу путем блокировки второго элемента И 7 на время, равное длительности цикла счета второго счетчика 20. Емкость второго счетчика 20 и частота импульсов, поступающих на

его тактовый вход с выхода второго делителя 46, выбираются такими, что длительность цикла счета равна максимально возможной для данной системы связи длительности кратковременных перерывов сеанса связи, которая, как правило, в десятки раз больше Тд, Одновременно логической 1, подаваемой с второго выхода первого счетчи- ка 19 блока 18, D-триггер 21 устанавливается в единичное состояние. Таким образом, после 1 на втором выходе первого счетчика 9 устройство переходит во второй режим ра боты, в котором оно находится на протяжении всего сеанса связи (за исключением кратковременных перерывов). В этом режиме фазирование синхроимпульсов осуществляется только по импуль- сам основного порога, поступающим на вход третьего элемента И 9 с выхода первого элемента И 6 через элемент ИЛИ 8, Основной порог при наличии сигнала набирается достаточно часто, и условие трехкратного его достижения за время Т почти постоянно выполняется. Поэтому к концу очередного интервала анализа на втором выход первого счетчика 19 практически всег да появляется 1, которая повторно сбрасывает второй счетчик 20 и подтверждает установку в единичное состояние D-триггера 21, Так как установочный вход D-триггера 21 имеет приоритет по отношению к информационному входу, в момент прихода очередного импульса на тактовый вход триггера с выхода второго делителя 46 логический О в D-триггер 21 не запи- сывается, и 1 на его выходе сохраняется в течение следующего интервала анализа.

Таким образом, при втором режиме работы на выходе второго счетчика 20 блока 18 присутствует О, а на выходе D-триггера 21 практически постоянно 1, Как в первом, так и во втором режимах на вход третьего элемента И 9 с выхода D-триггера 21 подается 1, открывающая этот элемент для прохождения импульсов предварительного или основного порога.

Если произошел кратковременный перерыв сегшса связи (например, за счет запирания сигнала), то частота достижения основного порога резко уменьшается, и условие набора его не менее тр ех раз за время Тд не выпол

, д J5 20 25 . д ,д

дс

35

50

5

няется. Поэтому устройство переходит в третий режим работы, при котором в течение каждого интервала 1 на втором выходе первого счетчика 19 сохраняется О, второй счетчик 20 повтор- но не сбрасывается, а в D-триггер 21 по каждому импульсу с выхода второго делителя 46 записывается О, поступающий с выхода второго счетчика 20, Отсутствие 1 на выходе первого счетчика 19 в течение всего цикла счета второго счетчика 20 свидетельствует об окончании текущего сеанса связи. При этом второй счетчик 20 переполняется, на его выходе появляется I, и устройство переводится в исходное состояние, соответстцушщее первому режиму работы, что обеспечивает быстрое вхождение в синхроитм в начале ноного сеанса сия:и|.

По импульсам предварительного и основного порога, поступающим на вход третьего элемента Н 9 (это происходит после появления фронта , фиг, 2), в первом и втором режимах работы устройства производится дискретная фазовая автоподстройка синхроимпульса со средним шагом квантовлшш фазы . Со/16, Импульс подстройки через элемент ИЛИ-НЕ 1, в котором он инвертируется, поступает на информационный вход второго D-триггера 13, Последний тактируется импульсами с периодом б(,/1б (фиг, 26), и на его выходе инверсный импульс подстройки (фиг, 2з) смещен Ha C o/lG относительно выходного импульса трс7ьего элемента И 9,

С выхода второго D-триггера 13 напряжение подается на вход управляемого счетчика 14, имеющего модуль счета 16, а его состояние в зависимости от логического уровня на выходе второго D-триггера 13 и состояния выхода старшего разряда делителя 17 может изменяться на 0,1 или 2 по каждому из .тактирующих импульсов, поступающих с периодом /16 с выхода второго делителя 46 частоты (фиг, 26),

При отсутствии импульса подстройки на вход разрешения счета счетного триггера 15 и на первый управляющий вход компаратора 16 поступает уровень 1 (фиг, 2з), при котором разрешается в счетном триггере 15, а вход разрешения счета делителя 17 подключается через коммутатор 16 к

выходу этого триггера (независимо от напряжения на втором управляющем входе коммутатора 16). 3 этом случае состояние управляемого счетчика на ка;хдом среднем шаге квантования фазы C c o/l) изменяется на единицу (на фиг. 2и показано выходное напряжение счетного триггера 15, а на фиг. 2к, л,м - первого, второго и.третьего выходов делителя 17 соответственно). Инверсный импульс подстройки с выхода второго D-триггера 13 (фиг,2з) запрещает счет в счетном триггере 15 (фиг. 2и). Одновременно переключается коммутатор 16, который соединяет с входом разрешения счета делителя 17 третий выход этого делителя (при логической 1 на втором управляющем входе коммутатора 16) или выход (N+l)-ro разряда регистра А4 памяти (при логическом О на втором управляющем входе). В первом и втором режимах работы устройства, когда ведется подстройка по импульсам предварительного или основного порогов, на второй управляющий вход коммутатора 16 с выхода D-триггера 21 подается 1, и позтому с входом разрешения счета делителя 17 частоты соединяется третий выход этого делителя. Напряжение на этом выходе делителя 17 частоты имеет форму меандра (фиг,2м) с периодом од, причем уровню 1 на этом выходе при наличии импульса подстройки с выхода второго D-триггера 13 соответствует запаздывание синхроимпульса по отношению к импульсу подстройки, а уровню О - опережение.

Если в момент появления на выходе второго D-триггера 13 инверсного импульса подстройки с третьего выхода делителя 17 на вход разрешения счета данного делителя подается 1 (фиг,2м фронт 1), То счет в делителе разрешается, и при поступлении очередного тактирующего импульса состояние управляемого счетчика изменяется на 2 (фиг. 2и, к,л,м). Это эквивалентно добавлению одного дополнительного тактирующего импульса.

Если в момент появления импульса подстройка на третьем выходе делителя 17 присутствует О, то счёт в делителе запрещается, и при поступлении очередного тактирующего импульса состояние управляемого счетчика не

0

5

0

5

0

5

0

5

изменяется, что эквивалентно исключению одного тактирующего импульса.

В обоих случаях фаза меандра на третьем выходе делителя 17 частоты приближается на один средний шаг квантования к фазе импульса подстройки. При совпадении этих фаз, когда в момент окончания импульса предварительного или основного порога на выходах счетного триггера 15 и делителя 17 имеются 1, подстройка запрещается с помощью первого элемента И-НЕ 5, которьй дешифрирует указанное состояние счетного триггера 15 и делителя 17 и блокирует подстройку ло- гичесю1м О (фиг. 2н), подаваемым на вход третьего элемента И 9,

После завершения подстройки фаза меандра, на третьем выходе делителя 17 совпадает с фазой импульсов подстройки, запаздывающих относительно действительных границ посылок на постоянную величину. Поэтому действительным границам посылок соответствует крупный интервал квантования фазы, в течение которого на первом выходе второго делителя 17 имеется О, а на втором и третьем выходах 1 (на фиг. 2 этот интервал выделен штрих- пунктирными линиями). В пределах данного интервала (окна) фаза синхроимпульсов уточняется с помощью дискретной фазовой автоподстройки с мелким шагом квантования . Уточнение производится путем тактирования второго D-триггера 35 импульсами (фиг. 2т), поступающими с периодом Оо/8 с прямого выхода третьего счетного триггера 33, момент окончания одного из которых совпадает с действительными границами посылок с точностью до ,/32. Для выделения этого импульса из всей последовательности в устройстве используется стробирова- ние второго D-триггера 35 напряжением с второго выхода делителя 17. При появлении 1 на этом выходе (фиг. 2л) разрешается запись во второй D-триг- гер 35 и в момент окончания очередного тактирующего импульса (фиг. 2т) в него записывается информация, поступающая на информационный вход с третьего выхода делителя 17, Сигнал . стробирования (фиг. 2л) появляется дважды за времяТд , причем в первый раз, когда с третьего выхода делителя 17 во второй D-триггер 35 переписывается Vl, сигнал стробирования

соответствует окну , а во второй раз, когда во BTOpoii D-триггер 35 переписывается О, - иитерв;и1у, сдви- нутог-ту относительно окна на . Таким образом, на инверсном выходе второго D-триггера 35, яшгяющемся выходом устройства, формируется меандр (фиг. 2х), отрицательные перепады которого совпадают с действтель- ными границами посылок с точностью до с д/32. Срезы меандра и яв тяютсн синхроимпульсами устройства поэлементной синхронизации.

Дискретная фазовая автоподстройка с мелким шагом квантования производится в пределах окна следующим образом. На один вход первого элемента ИСКЛЮ ШОЩЕЕ ИЛИ 26 поступает сигнал с выхода первого D-триггера 1, а на друго -. вход - с В1)1хода nepuoi:) счетного триггера 27. В исходном состоянии (до поступления очередного фронта элементарной посылки) оба сигнала имеют одинаковые логические уровни (фиг. 2г,о). При этом с выхода первого элемента ИСКЛЮЧАЮЩЕЕ ШШ 26 на вход первого элемента И 25 подается О, который появляется и па выходе первого элемента II 25 (фиг. 2п), запрещая изменение состояния первого счетного триггера 27.

После изменения логического уровня на выходе первого D-трнггера 1 (т.е. после появления очередного фронта сигнала) на выходе первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 26, а значит, и на входе первого элемента И 25 .устанавливается . При наличии 1 на дру

гих входах первого элемента И 25 этот уровень появляется и на выходе первого элемента И 25, разрешая изменение состояния первого счетного тррлтсра 27 в момент прихода очередного тактирующего импульса. Послг срабатьиааиия первого счетного тригге 1а 27 логические уровни на его выходе и выходе первого D-триггера 1 внол; становятся одинаковыми, в результате на выходе первого элемента М 25 но.чвлмет- ся О. Таким образом, на пмходе первого элемента И 25 ({юрмируются короткие импульсы (фмг. 2п) после пос- тунлешгя каждого фронта сг.гнала.

Если фронт на выходе перного D- триггера 1 опережает окно (но ие более чем на Сд/2), то импульс на выходе первого элемента И 25 поятиш- ется в первой четверти окна (,2г

Q

5 0 5 Q

5

0

5

0

фронт 2). Если фронт находится в пределах окна (данный случа11 встречается наиболее часто), то импульс появляется непосредственно после фронта также в пределах окна (фиг,2п, фронт 1). Ecjni фронт запаздывает относительно окна (но не более чем на сГд/2), то импульс формируется в nepBoi i четверти крупного интервала квантования, сдвинутого на по отношению к окну.

Это означает, что формируем1)1е на выходе первого элемента II 25 импульсы оказываются привязанными во времени к одному из указанных двух крупных интервалов квантовани; . . Они являются импульсами rioAv; i гоЙ1,и с мелким тагом квантования (. IJIMMCM под- ) может iiponsnojiMriiCM в одном из ,. liiii-::-; -.и..,- i- .чтг ..мння : в окне, если (lipoHT пмс rn-:i опережает оюю lUHi попадает к nei o, и в интервале, сдвинутом относительно окна на „/2, если фронт апазд/)ва- ет по отношению к окну.

Импульсы подстройки, поступающие с выхода первого элемента И 25, инвертируются во втором элементе 34 1 поступают (фи1 . 2р) на пход управляемого счетчика, образовашюго вторым счетным триггером 32 (маадший разряд), коммутатором 3 и счет)ым триггером 33 (старений разряд). Работа этого управляемого счетчика ь одобна работе управляемого счетчика, описанного выше.

При отсутствии импул; . подстройки на вход разрешения счета }л-орого счетного триггера 32 и п управляющий вход коммутатора 31 поступает уровень логической 1, при котором разрешается счет во втором счетном триггере 32, а вход разреи1ения счета третьех о триг- reyij 33 подключается черч ) i : Ммутатор 31 к выходу второго счетного триггера 32. В этом случае состояние управляемо о счетчика на каждог-; . -lejihOM шаге кпантования фазы изменяете на единицу (на фиг, 2с,т показан. лыходн11 е напряжения второго 32 и -rpcTijero 33 счеткых триггеров соответственно).

В течение интервала

на

третьего счетного трипч -ра 33 форми- ру)отся восемь импульсов, ричем положение отрицательного ni, peiia; a импульса, 1Гаходящегося в , совпадает с 1оложением деГ1ст)зите.Ь11ых границ посьитох с точностью 0/32,

Инверсный импульс подстройки (фиг, 2р) запрещает счет во втором счетмом триггере 32 (фиг, 2с), Одновременно переключается коммутатор 31, который соединяет с входом разрешение) счета третьего счетного триггера 33 инверсный выход второго D-тригге- ра 35, напряжение на котором имеет форму меандра (фиг. 2х) с периодом с , причем уровню логической 1 на этом выходе соответствует запаздывание синхроимпульса по ртношению к импульсу подстройки, а уровню О - опережение,

Если в момент появлений на выходе второго элемента И-НЕ 34 инверсного импульса подстройки с инверсного выхода второго D-триггера 35 на вход раэре1 ения счета третьего счетного триггера 33 подается 1 (фиг, 2х, фронт 2), то счет в третьем cчeтI эм триггере 33 разрешается, и при поступлении очередного тактирующего импульса состояние управляющего счетчика изменяется на 2 (фиг, 2с,т). Это эквивалентно добавлению одного дополнительного тактирующего импульса,

Если в момент появления импульса подстройки на инверсном выходе второго D-триггера 35 присутствует О, то счет в третьем счетном триггере 33 запрещается, и при поступлении очередного тактирующего импульса состояние управляемого счетчика не изменяется, что эквивалентно исключению одного тактирующего импульса,

В обоих случаях фаза меандра на прямом выходе третьего счетного триг

гера 33 приближается на один мелкий

40

шаг квантования к фазе импульса под- лтройки, В случае совпадения этих фаз датьнейшая подстройка блокируется с помощью третьего элемента И-ИЕ 36, с выхода которого на вход второго «с элемента И-НЕ 34 подается О (фиг,2у) при наличии логических 1 на прямых выходах второго 32 и третьего 33 счетных триггеров. Запрет подстройки логическим О на выходе третьего

50

элемента И-НЕ 36 возможен только в пределах окна, так как этот элемент открывается 1, поступающей на его вход с выхода делителя 17 (фиг,2м),

Для того, чтобы при подстройке в другом интервале квантования, сдвинутом относительно окна на С(з /2, не происходило скачков синхроимпульсов за счет смещения и сле, Q 5

0 5

о

5

0

«с

0

5

дующий крупный интеркап квантования относительного перепада импульса, формируемого на прямом выходе третьего счетного триггера 33, используется первый элемент И-НЕ 29, На выходе этого элемента О появляется (фиг,2ф) при наличии 1 на инверсных выходах второго 32 и третьего 33 счетных триггеров и, поступая на вход второго элемента И-НЕ 34, блокирует подстройку в течение соответствующего мелкого интервала квантования фазы, В результате запрещается подстройка по фронтам, запаздывающим относительно окна, если положительный перепад синхроимпульса находится в последней четверти окна. На вход первого элемента И-НЕ 29 сигнал с выхода делителя 17 подается через первый инвертор 23, и поэтому стро- бирование первого элемента И-НЕ 29 осуществляется со сдвигом во времени относительно моментов стробирования третьего элемента И-НЕ 36 (фиг,2у,ф)

Дпя уменьшения вызванных шумами случайных колебаний отрицательного перепада синхроимпульса внутри окна использованы первый D-триггер 28 и второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 30, В момент окончания импульса подстройки, поступающего с выхода первого элемента И 25 на тактовый вход первого D-триггера 28, в этот триггер записывается информация с инверсного выхода второго D-триггера 35, Так как логический уровень на выходе второго D-tpиггepa 35 в данный момент определяется положением импульса подстрой- ки относительно синхроимпульса, в первый D-триггер 28 записывается О при отставании импульса подстройки и 1 при опережении. На первый и второй входы второго элемента ИСКЛЮ- ЧАЩЕЕ ИЛИ 30 подаются напряжения с инверсных выходов первого 28 и второго 35 D-триггеров,

Если очередной и предыдущж фронты посьшок расположены по одну сторону от отрицательного перепада синхроимпульса, то в момент прихода импульса подстройки, соответствующего очередному фронту, логические уровни на первом и втором входах второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 30 различны, а на его выходе присутствует 1, при этом подстройка ие запрещается.

Если очередной и предыдущий фронты расположены по разные стороны от отрицат.ельного перепада синхроимпульса то в момент прихода очередного импулса подстройки логические уровни на входах второго элемента ИСКЛЮЧАЮЩЕЕ linn 30 одинаковы, и логическим О, поступающим с выхода этого элемента на вход второго элемента И-НЕ 34, подстройка запрещается, В результате уменьшаются случайные колебания фазы синхроимпульса в пределах окна, так как отклонения фронтов в противоположные стороны от действительных групп посылок, к которым приближаетс отрицательный перепад синхроимпульса могут быть вызваны только шумами.

В устройстве каждый инверсный импульс подстройки с выхода второго D-триггера 13 поступает на тактовый вход реверсивного счетчика 4I, на вход направления счета которого подается напряжение с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 43. Последний сравнивает логические уровни на выходах счетного триггера 38 и первого инвер тора 23. Состояние счетного триггера 38 определяется преобладающим направлением (знаком) подстройки, т.е. направлением изменения действительно фазы посылок. Выходное напряже.ние первого инвертора 23 противофазно напряжению на третьем выходе делителя 17.

Если направление очередной подстройки совпадает с направлением изменения действительной фазы посылок, то в момент появления инверсного импульса на тактовом входе реверсивног счетчика 41 логические уровни на выходе счетного триггера 38 и третьем выходе делителя 17 одинаковы, и на вход направления счета реверсивного счетчика 41 поступает с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 43 логическая 1. При этом реверсивньп счетчик 41 находится в режиме сложения, и эапи- санное в нем число увеличивается на единицу.

Если напра вление очередной подст- ройки противоположно направлению изменения действительной фазы посылок, то в момент появления инверсного импульса на тактовом входе реверсивного счетчика 41 на его вход направления счета поступает О, поэтому ревер- сивньй счетчик 4 J находится в режиме вычитания, и записанное в нем число уменьшается на единицу.

п

о 5 о

,

Q

5

Во время сеанса свйзи возможны подстройки как в направлении изменения действительной фазы посылок, так и в противоположном, причем последние наблюдаются, в основном, при расположении действительных фронтов посылок на границе двух соседних крупных интервалов квантовш ия фазы, что вызывает поочередный набор основного порога на этих интервалах. Поскольку в реверсивном счетчике 41 количество подстроек суммируется с учетом их знака, а количество подстроек в направлении изменения действительной фазы посылок преобладает, через определенные интервалы лреппи; реверсивный счетчик 41 переггалияотс.ч. Частота его переполнения np. ii- o пропорциональна средней скорости и -.меиоиия фазы меандра иа третьем выходе делителя 17 и, следовательно, скорости перемещения действителы1Ь х rpaiiini посылок. При модуле счета М реверсивного счетчика 41 период импульсов, появляющихся на его выходе переноса, равен времени, в течение ivoropor-o действительные границы посьпок перемещаются на М/2 крупных интервалов квантования фазы (или на М среллих интервалов квантования).

В начале сеанса связи, а также при изменении знака расстрор.ки частот задающих генераторов возможно несоответствие состояния счетпого триггера 38 и направления псремсцс- ния действительных rpaiuiu посыпок, При этом число в реверсмрнс м счетчике 41 постепенно уменычлегся, и после перехода его через нуль на выходе заема появляется импульс, которым инвертируется состояние счетного триггера 38. В результате устанавливается соответствие между состоя1П1ем счетного триггера 38 и преобладающим направлением подстройки. Однов)емен- но импульс заема поступает на вход разрешения параллельной записи реверсивного счетчика 41, гз --гмдшиГ разряд которого записывается с информационного входа параллельно; записи 1, а в остапьные разряды - О, т.е. реверсивный счетчик 41 переводится в исходное состояние, и н дальнейшем он работает в onncainioM режиме .

Период импульсов переноса на BI,коде реверсивного счетчика 41 }1змеряет- ся с помощью вычитающего счетчика 42,

Очередным импульсом переноса, подапа емььм на вход разрешения параллельной записи вычитающего счетчика 42, во все N разрядов этого счетчика с ин- формационных входов записываются 1 В промежутке между импульсами переноса реверсивного счетчика 41 в вычитающем счетчике 42 число уменьшается на единицу по каждому импульсу, пос- тупившему на его тактовьй вход с выхода второго делителя 46 частоты. Частота тактирующррс импульсов во много раз выше частоты импульсов на выходе переноса реверсивного счетчика 41, При появлении следу|эщ1го импульс переноса производится перезапись полученного в вычитающем счетчике 42 числа в N разрядов регистра 44 памяти, в (Н+1)-й разряд которого одно- временно записывается информация о знаке подстройки с выхода счетного триггера 38, и выполняется предустановка вычитающего счетчика 42 Число, записываемое в регистр 44 памяти, тем меньше, чем меньше расстройка частот задающих генераторов и скорость изменения действительной фазы посылок. При очень малых расстройках вычитающий счетчик 42 успе- вает достичь нулевого состояния всех разрядов за время между импульсами переноса реверсивного счетчика 41, после этого на выходе заема вычитающего счетчика 42 появляется импульс, который сбрасывает реверсивный счетчик 41 и регистр 44 памяти. При нулевом состоянии N разрядов регистра 44 памяти устанавливается максимальный период коррекции фазы синхроимпульсо во время перерывов связи, который опревышает наибольшую длительность пе 45ерывов,

С выходов регистра 44 памяти числ записанное в его N разрядов, подаетс на входы параллельной записи суммирующего счетчика 39, Число разрядов зтого счетчика также равно N, а частота импульсов, поступающих на его тактовый вход с выхода второго делителя 46 частоты, в М раз превышает частоту импульсов на тактовом входе а1читающего счетчика 42,

Во втором режиме работы устройства, когда качество связи достаточно хорошее, с второго выхода первого счетчика 19 на второй вход элемента ИЛМ 40 практически постоянно подает

ся

свидетельствующая о выполне0 о Q

с

5

0

5

нии условия трехкратного набора основного порога в течение интервала ана1И1за Т, С выхода элемента ИЛИ 40 на вход разрешения параллельной записи суммирующего счетчика 39 также поступает 1, поэтому суммирующий счетчик 39 находится в режиме параллельной записи, и импульсы на его выходе переноса отсутствуют. На выходе R-триггера 12 во втором режиме рабо- « ты устройства присутствует уровень логического О, и зтот триггер не влияет на автоподстройку по импульсам основного порога.

При кратковременном перерыве сеанса связи на втором выходе первого счетчика 19 и на выходе D-триггера 21 устанавливается уровень логического О, Логический О, поступающий на

вход третьего элемента И 9, запрещает подстройку не только по предварительному порогу, но и по основному. Благодаря этому устраняется возможность случайных отклонений фазы синхроимпульса на tj, /8 и более из-за набора основного порога за счет воздействия шумов в перерывах связи, Логический О появляется также на выходе элемента ИЛИ 40, н суммирующий счетчик 39 начинает подсчет тактирующих импульсов.

При переполнении суммирующего счетчика 39 на его выходе переноса появляется импульс, который поступает через элемент ИЛИ 40 на вход разрешения параллельной записи суммирующего счетчика 39, В peзyльтafe в этот счетчик вновь записывается число с выходов N разрядов регистра 44 памяти, и описанный цикл работы повторяется. Количество импульсов, поступивших на тактовый вход суммирующего счетчика 39 на интервал времени между двумя импульсами на его выходе переноса, равно количеству импульсов, поступающих на тактовый вход вычитающего счетчика в течение одного периода следования импульсов переноса реверсивного счетчика 41, Поскольку суммирующий счетчик 39 тактируется в М раз чаще, чем вычитающий счетчик 42, период следовшгия импульсов переноса суммирующего счетчика 39 равен интервалу времени, в течение которого действительные границы посылок перемещаются на один среднш щаг квантования . Эти импульсы используются

для коррекции фазы синхроимпульсов при перерыве связи.

Очередной корректирующий импульс с выхода переноса устанавливает R- триггер 12 в состояние Г .С выхода R-триггера 12 1 подается на вход элемента ИЛИ-НЕ I1, на выходе которого появляется О. При записи О в второй Б-триггер 13 на выходе послед него формируется инверсньй импульс подстройки, которым R-триггер 12 возвращается в состояние логического О. Так как во время перерыва связи с выхода D-триггера 21 на второй уп- равляющиь вход коммутатора 16 поступает О, при подстройке с входом разрешения счета делителя 17 частот i через коммутатор 16 соединяется выход (N+l)-ro разряда регистра 44 па-. мяти. Логический уровень на этом выходе такой же, какой был на входе разрешения счета делителя 17 во втором режиме работы устройства при подстройке синхроимпульсов в направлении перемещения действительных границ посылок. Поэтому и во время перерыва по каждому корректиру1ощему импульсу с выхода переноса суммирующего счетчика 39 производится сдвиг фазы меандра, формируемого на третьем выходе делителя 17, на один средний шаг квантования в этом же направлении, одновременно перемещается окно.

После поступления двух корректирующих импульсов фаза синхроимпульса, отрицательный перепад которого находится в пределах окна изменяется на один крупный шаг квантования. Так как за два периода импульсов коррек- ции действительные границы посыпок тоже смещается на один крепный шаг квантования, при перерывах связи максимальное отклонение фазы синхроимпульсов от действительной фазы посы- лок не превышает ,

Модель счета М реверсивного счетчика 41, число разрядов N вычитающего 42 и суммирующего 39 счетчиков и период следования Т, импульсов, поступающих на тактовый вход суммирующего счетчика 39, выбираются из

условий igJfT

М 2

е,81Т„- fT ,

)

N 2( - 1);

Тя т /

так п -

где Sf - наибольшая для данной систе- мз связи относительная рас-.

, ig 5 0 15 о

Q j

Q

5

стройка задающи с генераторов передатчика и приемника;

Т - максимальная длительность перерывов сеанса связи;

С J- усечение до целого числа. Перед началом сеанса связи (в первом режиме работы устройства) на входы сброса вычитающего 42 и суммирующего 39 счетчиков с выхода третьего счетчика подается 1, в результате чего измерение скорости перемещения границ посьлок и коррекция не производятся.

Таким образом, устройство поэлементной синхронизации обеспечивает безобрывность связи при расс;рпГ|кс частот задающих генералзрон передатчика и приемника. Это дослигаотся путем коррекш1и поло/кеш:; синхроимпульса во время перерывов связи в соответствии с измеренными и i-ечсние сеанса сзязи (при наличии п|1 1 п;млемого сигнала) скоростью и напраилением вызванного расстройкой иерсмсчцония действительных границ элеь ситариых посьиюк. Погрешность Koppc-Ki ifu яс. превышает , Поэтому пос.че окопча- ция перерыва связи фазг сиихрои. -шуль- сов с достаточно высокой точноегью соответствует действительно фазе принимаемых посылок, и сбоев поэлементной и цикловой синхг сниз ации не происходит.

Формула изобретения

1 , Устройство поэлемстпоп синхронизации, содержащее задающий генератор, первый делитель частоты, первый D-триггер, селектор tf POHTOB, счетчик, первый и второй элемент И, элемент ИЛИ, третий элемент И и элемент ИЛИ-НЕ, при этом первые входы первого и второго элемелтов И объединены, а выходы подключеиь соответственно к первому и BTopot-fy входа:- элемента ИЛИ, второй вход второго элемента И подключен к счетном входу счетчика, о т л и ч а ю щ с е с я тем, что, с целью повьшеиия помехоустойчивости путем обеспечения без- обрывности при расстройке частот задающих генераторов передатчика и приемника и снижения погре;1пости син- |Хронизации, введены первьп и в 1-орой элементы .И-НЕ, R-триггер, вто)1,е D- триггер и делитель частоты, управляемый счетчик, блок дискретной фазовой

автоподстронки, блок коррекции и блок выбора режимов работы, при этом выход первого D-триггера через последовательно соединенные селектор и счетчик подключен к второму входу первого элемента И, выход элемента ИЛИ через последовательно соединенные третий элемент И, элемент lilM-HE и второй D-триггер подключен к первому сигнальному входу управляемого счетчика, .объединенному с входом установки нуля R-триггера, первым уп- равлянлцим входом управляемого счетчика и первым информационным входом блока коррекции, второй иЯформацион- ннй вход которого подключен к -первому выходу блока дискретной фазовой автоподстройки, первый, второй и третий сигнальные входы блока коррекции .подключены соответственно к первому, второму и третьему выходам блока выбора режимов работы, первый и второй тактовые входы блока коррекции подключены соответственно к первому выходу второго делителя частоты и к тактовому выходу блока выбора режимов работы, первый и второй информационные выходы блока коррекции подключены соответственно к единичному входу R-триггера и первому информационному входу управляемого счетчика, к такто- BOf-ry входу которого подключены объединенные второй выход второго делителя частоты и тактовый вход второго D-триггера, к второму информационному входу управляемого счетчика подключены объединенные первый вход первого элемента И-НЕ, первъй информационный вход блока дискретной фазовой автоподстройки и первый выход упрадпяемо- „го счетчика, второй и третий выходы которого подключены соответственно к объединенным второму входу первого элемента И-НЕ и второму информационному входу блока дискретной фазовой автоподстройки и к объединенным тре- Tbet-iy входу первого элемента И-НЕ и третьему информационному входу блока дискретной фазовой автоподстройки, второй управляющий вход управляемого счетчика подключен к объединенным информационному выходу блока выбора режимов работы и второму входу третьего элемента И, четвертый выход упраааяемого счетчика подключен к четвертому входу первого элемента И-НЕ, выход которого подключен к третьему входу третьего элемента И,

5

0

5

0

5

0

5

0

5

четвертый вход которого подключен к объединенным второму входу селектора фронтов, первому входу первого делителя частоты и к третьему выходу второго делителя частоты, четвертый и пятый выходы которого подключены соответственно к первому и второму тактовому входу блока выбора режима работы, третий тактовый вход и первый и второй сигнальные выходы которого подключены соответственно к выходу первого элемента И, к третьему и четвертому входам второго элемента И, четвертый информационный вход и тактовый вход блока дискретной фазовой автоподстройки подключены соответственно к выходу первого D-триггера и к объединенным тактовым входам второго делителя частоты и первого D-триггера и к выходу задающего генератора, выход селектора фронтов подключен к входу сброса первого делителя частоты, выход которого через второй элемент И-НЕ подключен к объединенным счетному входу счетчика, второму входу второго элемента Ник третьему входу первого элемента И, первый вход которого объединен с тактовым входом счетчика и вторым входом второго элемента И-НЕ, выход R-триггера подключен к второму входу элемента ИЛИ-НЕ, при этом входом и выходом устройства являются соответственно информационный вход первого D-триггера и второй выход блока дискретной фазовой автоподстройки,

2, Устройство по п. 1, о т л и - чающееся тем, что блок коррекции содержит счетньй триггер и последовательно соединенные элемент ИСКЛЮЧАЩЕЕ ИЛИ, реверсивный счетчик, вычитающий счетчик, регистр памяти, суммирующий счетчик и элемент ИЛИ, выход которого подключен к счетному входу суммирующего счетчика, два других входа которого являются соответственно первым и вторым сигнальными входами блока коррекции, второй выход реверсивного счетчика подключен к объединенным своему счетному входу и входу счетного триггера, тактовый вход и входы направления счета и сброса реверсивного счетчика подключены соответственно к первому информационному входу блока коррекции, через элемент ИСЮПОЧАЩЕЕ ПТИ к второму информационному входу блока коррекции, к объединенным выходу заема

вычитающего счетчика и входу сброса регистра памяти, вход (п+1)-го разряда, вход разрешения и выход (N+l)-ro разряда регистра памяти подключены соответственно к объединенным выходу счетного триггера и второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, к первому выходу реверсивного счетчика и к второму информационному выходу блока коррекции, выход суммирующего счетчика является первым информационным выходом блока коррекции, первый и второ тактовые входы и третий сигнальный вход блока коррекции подключены соот- ветственно к тактовому входу и входу сброса вычитающего счетчика и к второму входу элемента ИЛИ,

3, Устройство по п. 1, отличающее ся тем, что блок диск- ретной фазовой аэтоподстройки содержит первый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, бчетный триггер, инвертор, элемент И-НЕ и последовательно соединенные второй инвертор, элемент И, первый D-триггер, второй элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, второй элемент И-НЕ, второй счетный триггер, коммутатор, третий счетный триггер и объединенные по первьш входам второй D-триггер и третш элемент И-НЕ, выход которого подключен к второму входу второго элемента И-НЕ третий и четвертый входы которого подключены соответственно к объединенным выходу элемента И, первому входу пер- вого D-триггера, первому входу первого счетного триггера и выходу первого элемента И-НЕ, первьй, второй и третий входы которого подключены соответственно к второму выходу второго счетного триггера, к второму выходу третьего счетного триггера и к выход первого инвертора, который является первым выходом блока дискретной фазовой автоподстройки, вход первого инвертора подключен к объединенным второму входу третьего элемента И-НЕ и второму входу второго D-трнггера, который является первым информационным входом блока дискретной фазовой автоподстройки, второй и третий информационные входы которого подключены соответственно к входу второго инвертора и к объединенным третьему входу D-триггера и второг-гу входу элемента И, выход первого счетного триггера через первый элемент ИС1ШЮЧАЮ- I lEE ИЛИ подключен к третьему входу элемента И, к второму входу первого счетного триггера подютючены объединенные вторые входы второго счетного триггера, третьего счетного триггера н тактовый вход блока дискретной фазовой автоподстройки, второй выход которого подключен к o67jeAnneHHuM выходу второго D-триггера, второму входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второму входу первого D-трнггера и второму входу коммутатора, третий вход которого подключен к выходу второго элемента И-НЕ, третий вход третьего элемента И-НЕ подключен к первому выходу второго счетного триггера, второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является четвертым информационным входом блока дискретной фазовой автоподстройкн.

а llllllllllllllllllllllllllllllllllllllinillMlllillllllllllll

б JlnnпплпnnлrmлшmлшlnnпгLnлnnлпnл

nnLnjnfTn rLrLrL ПП П П П

Фаг. 2

Редактор И.Шмакова

Составитель О.Мелькова Техред Л. Сердюкова

заказ 6402/57

Тираж 626

ВНИИПИ Государствеиного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, К-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Корректор Т.Палий

Подписное

| Устройство поэлементной синхронизации | 1985 |

|

SU1319301A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-10-23—Публикация

1987-09-21—Подача