Изобретение относится к технике электро- и радиосвязи и может использоваться в системах передачи и приема цифровой информации в каналах с замираниями и многолучевым распространением сигнала.

Цель изобретения - повышение точности и уменьшение времени синхронизации.

На чертеже представлена структурная электрическая схема устройства поэлементной синхронизации.

Устройство содержит селектор 1 фронтов, I регистров 2 сдвига, счетчик 3 тактовых импульсов, ш первых элементов 4, -4т сравнения, элемент ИЛИ-НЕ 5, первый регистр 6 памяти, второй элемент 7 сравнения, второй регистр 8 памяти, сумматор 9 одноразрядных чисел, третий элемент 10 сравнения, третий регистр 11 памяти, четвертый и пятый элементы 12 и 13 сравнения, первый элемент ИЛИ 14, элемент 15 задержки, задающий генератор 16, блок 17 добавления-вычитания импульсов, делитель 18 частоты, формирователь 19 синхроимпульсов, фазовый дискриминатор 20, первый, второй, третий и четвертый элементы И 21-24, второй элемент ИЛИ 25, счетчик 26 синхроимпульсов, триггер 27, инвертор 28.

Устройство работает следующим образом.

Импульсы тактовой частоты, следуя с периодом Т/п, поступают с задающего генератора 16 на счетный вход счетчика 3 тактовых импульсов, модуль счета которого равен п. На выходе счетчика 3 тактовых импульсов при этом появляются числа в двоичном коде, соответствующие номерам тактовых интервалов в посылке. Таким образом, посылка длительностью Т оказывается разделенной на п одинаковых вплотную примыкающих друг к другу тактовых интервалов, каждому из которых соответствует двоичное f-разрядное число (f fogin) на выходе счетчика 3 тактовых импульсов. Каждый разряд этого числа поступает на информационный вход последовательного ввода соответствующего регистра 2. Число ячеек каждого из регистров 2 равно т.

Селектор 1 фронтов выделяет фронты принимаемых элементарных посылок и формирует из них короткие импульсы, поступающие на сдвигающие входы всех регистров 2. При этом в первые ячейки регистров 2 с выходов счетчика тактовых импульсов 3 записывается поразрядно двоичное число, соответствующее номеру того тактового интервала, на который попадает фронт элементарной посылки. При поступлении следующего фронта в первые ячейки регистров 2 записывается номер тактового интервала, на который попал этот новый фронт, а записи номеров тактовых интервалов, на которые попали предыдущие фронты, сдви5

гаются на одну ячейку. В результате в течение всего сеанса связи в одноименных ячейках регистров 2 оказываются поразрядно записанными ш номеров тех тактовых интервалов, на которые попали m очередных фронтов принимаемых посылок.

При отсутствии помех фронты посылок, следуя с интервалами, кратными Т, попадают на один и тот же тактовый интервал,

поэтому в регистры 2 записывается одно и то же число, соответствующее номеру этого тактового интервала в посылке. Помехи вызывают краевые искажения и дробление посылок. Из-за этого интервалы между фронтами не всегда кратны Т, что приводит к записи в регистры 2 чисел, соответствующих разным номерам тактовых интервалов. Рассеяние оказывается тем больщим, чем меньще отношение сигнал/щум. Однако и в этом случае фронты чаще всего попадают

0 на тактовый интервал, в пределах которого находятся действительные границы посылок. Устройство синхронизации фазирует последовательность синхроимпульсов с тем тактовым интервалом, на который попало максимальное число фронтов (номер этого интервала максимальное число раз записан в регистрах 2), причем фазирование разрещается, если только среди пос тедних m фронтов число фронтов, попавших на один тактовый интервал, превышает сравQ нительно низкий уровень Ki. В начале сеанса связи фазирование, производится скачкообразно, сбросом в нулевое состояние делителя 18, из выходного напряжения которого формирователь 19 формирует синхроимпульсы, следующие с периодом Т. Пос5 ле первого в данном сеансе связи фазирования по достаточно высокому уровню К (это происходит, когда среди последних m фронтов более Кг фронтов попало на один и тот же TaKfoBbm интервал) дальнейшее

f, фазирование синхроимпульсов на выходе устройства осуществляется путем шаговой автоподстройки делителя 18 по импульсам, выработанным третьим элементом 10 сравнения.

5 При включении устройства поэлементной синхронизации в регистры 2 записываются номера m первых тактовых интервалов: в первые ячейки регистров 2 записывается номер нулевого интервала, во вторые - номер первого интервала, в тре0

тьи -- номер второго и т.д. Если, например.

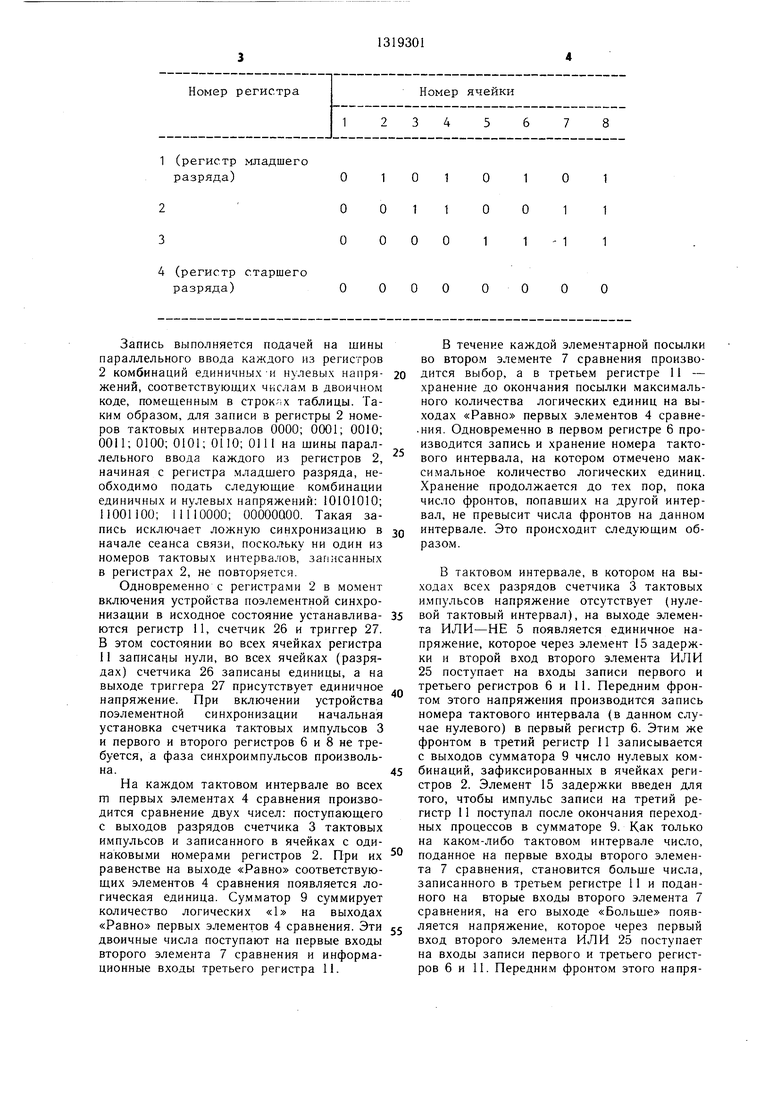

число ячеек каждого из регистров 2 т 8, а число тактовых интервалов, на которые разбивается каждая посылка, , (от нулевого до пятнадцатого интервала), чему 5 соответствует число регистров 2 , то в момент включения в ячейки регистров 2 необходимо записать в двоичном коде числа, помешенные в столбцах таблицы.

1(регистр младшего

разряда)

2

3

4(регистр старшего

разряда)

Запись выполняется подачей на шины параллельного ввода каждого из регистров 2 комбинаций единичных-и нулевых напря- жений, соответствующих числам в двоичном коде, помещенным в строклх таблицы. Таким образом, для записи в регистры 2 номеров тактовых интервалов 0000; 0001; 0010; ООП; 0100; 0101; ОНО; 0111 на щины параллельного ввода каждого из регистров 2, начиная с регистра младшего разряда, необходимо подать следующие комбинации единичных и нулевых напряжений: 10101010; 11001100; 11110000; OOOOOQOO. Такая запись исключает ложную синхронизацию в начале сеанса связи, поскольку ни один из номеров тактовых интервалов, записанных в регистрах 2, не повторяется.

Одновременно с регистрами 2 в момент включения устройства поэлементной синхронизации в исходное состояние устанавлива- ются регистр 11, счетчик 26 и триггер 27. В этом состоянии во всех ячейках регистра 11 записаны нули, во всех ячейках (разрядах) счетчика 26 записаны единицы, а на выходе триггера 27 присутствует единичное напряжение. При включении устройства поэлементной синхронизации начальная установка счетчика тактовых импульсов 3 и первого и второго регистров 6 и 8 не требуется, а фаза синхроимпульсов произвольна.

На каждом тактовом интервале во всех гп первых элементах 4 сравнения производится сравнение двух чисел: поступающего с выходов разрядов счетчика 3 тактовых импульсов и записанного в ячейках с одинаковыми номерами регистров 2. При их равенстве на выходе «Равно соответствующих элементов 4 сравнения появляется логическая единица. Сумматор 9 суммирует количество логических «1 на выходах «Равно первых элементов 4 сравнения. Эти двоичные числа поступают на первые входы второго элемента 7 сравнения и информационные входы третьего регистра 11.

0101 0011 11-11

О

О

О

О

5

0 о

В течение каждой элементарной посылки во втором элементе 7 сравнения производится выбор, а в третьем регистре 11 - хранение до окончания посылки максимального количества логических единиц на выходах «Равно первых элементов 4 сравне- .ния. Одновременно в первом регистре 6 производится запись и хранение номера тактового интервала, на котором отмечено максимальное количество логических единиц. Хранение продолжается до тех пор, пока число фронтов, попавщих на другой интервал, не превысит числа фронтов на данном интервале. Это происходит следующим образом.

В тактовом интервале, в котором на выходах всех разрядов счетчика 3 тактовых импульсов напряжение отсутствует (нулевой тактовый интервал), на выходе элемента ИЛИ-НЕ 5 появляется единичное напряжение, которое через эле.мент 15 задержки и второй вход второго элемента ИЛИ 25 поступает на входы записи первого и третьего регистров 6 и 11. Передним фронтом этого напряжения производится запись номера тактового интервала (в данном случае нулевого) в первый регистр 6. Этим же фронтом в третий регистр 11 записывается с выходов сумматора 9 число нулевых комбинаций, зафиксированных в ячейках регистров 2. Элемент 15 задержки введен для того, чтобы импульс записи на третий регистр 11 поступал после окончания переходных процессов Б сумматоре 9. Как только на каком-либо тактово.м интервале чиспо, поданное на первые входы второго элемента 7 сравнения, становится больше числа, записанного в третьем регистре 11 и поданного на вторые входы второго элемента 7 сравнения, на его выходе «Больше появляется напряжение, которое через первый вход второго элемента ИЛИ 25 поступает на входы записи первого и третьего регистров 6 и 11. Передним фронтом этого напряжения осуществляется запись в третий регистр 1 1 числа, находящегося в этот момент на его информационных входах, а также занись в первый регистр 6 номера текущего тактового интервала. Если же число, поданное на первые входы второго элемента 7 сравнения, меньще или равно числу, зафиксированному в третьем регистре 11 памяти, на выходе «Больще второго элемента 7 сравнения напряжение отсутствует и перезаписи новых чисел в первый и третий регистры 6 и 11 не происходит.

Таким образом, в конце каждого периода работы счетчика 3 тактовых И1мпульсов, т.е. перед появлением очередной комбинации, состоящей из одних нулей, в первом регистре 6 фиксируется номер тактового интервала, на который попало максимальное число из последних m фронтов, а в третьем регистре 11 количество фронтов, попавщих на данный интервал. Импульс, поступающий в конце каждого периода работы, равного длительности элементарной посылки, с выхода переноса счетчика тактовых импульсов 3, проходит через второй элемент И 22, если число фронтов, зафиксированное в третьем регистре 11, превыщает уровень К,, и с выхода счетчика 26 поступает единичное напряжение, либо через четвертый элемент И 24, если это число превышает уровень Кг- Далее импульс через первый элемент ИЛИ 14 поступает на вход записи второго регистра 8. Передним фронтом этого импульса осуществляется перезапись номера тактового интервала, хранящегося в первом регистре 6, в ячейки второго регистра 8. Номер тактового интервала, записанный во второй регистр 8, сравнивается третьи.м элементом 10 сравнения с номерами текущих тактовых интервалов, поступающими с выходов счетчика 3 тактовых импульсов. В момент их совпадения на выходе «Равно третьего элемент а 10 сравнения формируется импульс длительностью в один тактовый интервал, который поступает на второй вход фазового дискриминатора 20 и на первый вход первого элемента И 21. Этот импульс проходит на вход «Сброс делителя 18, если на второй вход первого элемента И 21 поступает единичное напряжение с. выхода триггера 27. При сбросе делителя 18 происходит скачкообразное фазирование последовательности синхроимпульсов с тем тактовым интервалом, номер которого записан во втором регистре 8.

В начале сеанса связи импульс с выхода переноса счетчика 3 тактовых импульсов всегда проходит на вход записи регистра 8 памяти, если число фронтов, зафиксированное в третьем регистре 11, превыщает уровень KI , а импульс с выхода «Равно третьего элемента 10 сравнения всегда поступает на вход «Сброс делителя 18, так как

в результате начальной установки на выходе счетчика 26 и триггера 27 напряжения присутствуют. При этом цепь автоподстройки, содержащая фазовый дискриминатор 20 и блок 17, в процессе синхронизации не участвует, так как фаза импульсов на первом и втором входах фазового дискриминатора 20 одинакова. Как только в данном сеансе связи число фронтов, попавщих на тактовый интервал, номер которого зафиксирован во втором регистре 8, в первый раз превысило уровень К, на выходе «Больше пятого элемента 13 сравнения появляется напряжение. Этим напряжением производится сброс счетчика 26 и изменение состояJ- ния триггера 27. Напряжение на выходе счетчика 26 и триггера 27 исчезает, а на выходе инвертора 28 появляется. Соответственно второй и первый элементы И 22 н 21 перестают пропускать импульсы, поступающие на их первые входы, а третий элемент И 23

0 начинает пропускать импульсы с выхода «Равно третьего элемента 10 сравнения на вход счетчика 26, который подсчитывает их число. Напряжение на выходе счетчика 26, отсутствует до тех пор, пока это число

5 не достигнет L. Напряжение на выходе триггера 27 отсутствует до конца сеанса связи. Следовательно, после фазирования по уровню, превышающему Kj., фазирование по уровню, не превыщающему К, запрещается на время LT, а фазирование синхроим0. пульсов путем сброса делителя 18 запрещается до конца сеанса связи. Дальнейшее фазирование последовательности синхроимпульсов во время сеанса связи производится путем шаговой автоподстройки их по импульсам с выхода «Равно третьего

5 элемента 10 сравнения.

Шаговая автоподстройка фазы синхроимпульсов по импульсам с выхода «Равно третьего элемента 10 сравнения производится путем подачи на первый вход фазового

Q дискриминатора 20 выходного напряжения делителя 18, а на второй вход фазового дискриминатора 20 - импульсов с выхода «Равно третьего элемента 10 сравнения.

Если импульс с выхода «Равно тре- 5 тьего элемента 10 сравнения опережает синхроимпульс на время, меньшее Т/2, на выходе опережения фазового дискриминатора 20 появляется сигнал, поступающий на соответствующий управляющий вход блока 17. При появлении этого сигнала блок 17 включает в последовательность импульсов, поступающих с выхода задающего генератора 16 через блок 17 на вход делителя 18, дополнительный импульс, смещая тем самым синхроимпульсы в сторону опе- 5 режения на величину, равную Т/п - периоду следования тактовых импульсов с задающего генератора 16 (здесь п - коэффициент деления делителя 18). Если же

0

импульс с выхода «Равно третьего элемента 10 сравнения отстает от синхроимпуль сов на время, меньшее Т/2, на выходе отставания фазового дискриминатора 20 появляется сигнал, который вызывает исключение одного импульса из пос тедовательности тактовых импульсов, следующих с задающего генератора 16 через блок 17 на вход делителя 18. Тем самым обеспечивается смещение синхроимпульсов на время Т/п в сторону отставания. Ескость L счетчика 26 выбирается такой, чтобы за время L- Т в используемом канале связи фронт посылки не мог сместиться больше, чем на Т/5. Благодаря этому во. время сеанса связи изменение положения фронтов посылок даже при замираниях сигнала вызывает скачки фазь импульсов с выхода «Равно третьего элемента 10 сравнения заведомо меньшие, чем Т/2, что гарантирует правильное определение фазовым дискриминатором 20 взаимного положения этих импульсов и синхроимпульсов. Действительно, если произошло замирание сигнала и в течение времени LT не поступали импульсы на перезапись- нового номера тактового интервала во второй регистр 8 памяти по уровню, превышающему Ki, то при появлении напряжения на выходе счетчика 26, а следовательно, и на третьем входе второго элемента И 22 вновь обеспечивается возможность передачи информации во второй регистр памяти 8 при условии превышения уровня Ki, которое выполняется и во время замирания сигнала. При этом возможны скачки фазы импульсов с выхода «Равно третьего элемента 10 сравнения, превышающие Т/2, за счет воздействия помех при синхронизации по уровням, не достигающим Ki. Однако такие скачки редки и некоррелированы между собой. Поэтому они будут сглажены цепью автоподстройки и слабо скажутся на синхроимпульсах.

Сохраняя все функциональные возможности известного, предлагаемое устройство поэлементной синхронизации обеспечивает уменьшение времени синхронизации при одновременном повышении ее точности. Первым фактором, уменьшаюшим время синхронизации при повышении ее точности, является то, что синхроимпульсы фазируются по тому тактовому -интервалу, на который попадает наибольшее число из m фронтов, записанных в регистрах 2, если это число превышает уровень К,. Такая оценка расположения границ элементарных посылок с большей вероятностью совпадает с их действительными границами, поэтому в данном устройстве практически всегда превышение уровня К лишь подтверждает и фиксирует ранее достигнутую синхронизацию.

В результате одновременно уменьшается время синхронизации и повышается ее точность. Другим фактором, уменьшающим время синхронизации при повышении ее точности, является то, что обновление информации о положении фронтов посылок

производится постепенно по мере поступления новых фронтов. Стирание информации производится поочередно: в момент прихода каждого нового фронта стирается (точнее выводится из регистров 2) инфор.мация о положении наиболее старого из m предшествующих фронтов. Это позволяет без всяких перерывов при поступлении каждого нового фронта уточнять действительное положение границ элементарных посылок.

15

Формула изобретения

Устройство поэлементной синхрони зации, содержащее селектор фронтов, последовательно соединенные задающий генератор, блок добавления-вычитания импульсов, к второму и третьему входам которого подключены соответственно выходы «Добавление и «Вычитание фазового дискриминатора, делитель частоты, к входу «Сброс которого подключен выход первого элемента И, и формирователь синхроимпульсов, к входу которого подключен первый вход фазового дискриминатора, последовательно соединенные счетчик синхроимпульсов, выход которого через второй элемент И подключен к первому входу первого элемента

ИЛИ, инвертор и третий элемент И, выход которого подключен к входу счетчика синхроимпульсов, вход «Сброс которого соединен через триггер с первы.м входом первого элемента И, отличающееся те.м, что, с целью повыщения точности и уменьшения

времени синхронизации, введены последовательно соединенные счетчик тактовых импульсов, I регистров сдвига (f ), где п - модуль счета счетчика тактовых импульсов), к сдвигающим входам которых

подключен выход селектора фронтов, m первых элементов сравнения, где m - число ячеек каждого регистра сдвига, сумматор одноразрядных чисел, второй элемент сравнения, второй элемент ИЛИ. первый регистр памяти, к информационным.входам которого

и к вторым входам первых элементов сравнения подключены выходы разрядов счет-- чика тактовых импульсов, второй регистр па.мяти, к входу записи которого подключен выход первого элемента ИЛИ, и третий элемент сравнения, выход которого подключен к вторым входам фазового дискриминатора и первого элемента И, при. этом выходы разрядов счетчика тактовых импульсов подключены к вторым входам третьего элемента сравнения и через введенные последовательно соединенные элемент ИЛИ- НЕ и элемент задержки к второму входу второго элемента ИЛИ, выход которого подключен к входу записи третьего регист1319301910

pa памяти, к информационным входам ко-элемента И и к входу «Сброс счетчика син- торого подключены выходы сумматора од-хроимпульсов, к третьему входу второго норазрядных чисел, причем к вторым входамэлемента И и второму входу четвертого эле- второго элемента сравнения подключенымента И подключен выход переноса счетчи- первые входы четвертого и пятого элемен- ка тактовых импульсов, выход четвертого тов сравнения, выходы которых подключе-элемента И подключен к второму входу пер- ны соответственно к второму входу второгового элемента ИЛИ, а вторые входы первоэлемента И и к первому входу четвертогого и третьего элементов И соединены.

.; , -Г.

. И . - .-

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство поэлементной синхронизации | 1981 |

|

SU987834A1 |

| Устройство поэлементной синхронизации | 1987 |

|

SU1517142A1 |

| Устройство для кодирования и декодирования сигналов в системах передачи цифровых данных | 1980 |

|

SU1046959A1 |

| Устройство для сопряжения цифровой вычислительной машины с каналом связи | 1991 |

|

SU1837301A1 |

| Устройство избирательного вызова | 1987 |

|

SU1496014A1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Устройство тактовой синхронизации | 1983 |

|

SU1099403A1 |

| Устройство синхронизации | 1988 |

|

SU1644398A1 |

| Устройство тактовой синхронизации | 1986 |

|

SU1411990A1 |

| Устройство для измерения преобладаний двоичных сигналов | 1986 |

|

SU1338102A2 |

Изобретение .может быть использовано в системах передачи и приема цифровой информации в каналах с замираниями и многолучевым распространением сигнала. Цель Вход изобретения - повышение точности и уменьшение времени синхронизации. Устройство содержит селектор фронтов 1, f регистров 2 сдвига, счетчик 3 тактовых и.мпу.тьсов, первые элементы сравнения 4,-4т, элемент ИЛИ-НЕ 5, регистры 6, 8 и 11 памяти, элементы 7, 10. 12 и 13 сравнения, сумматор 9 одноразрядных чисел, эт-ты ИЛИ 14 и 25, эл-т 15 задержки, задаюший г-р 16, блок 17 добавления-вычитания импульсов, делитель 18 частоты, формирователь 19 синхроимпульсов, фазовый дискриминатор 20, эл-ты И 21-24, счетчик 26 синхроимпульсов, триггер 27, инвертор 28. 1 табл., 1 ил. W со со со о

| Авторское свидетельство СССР № 1446814, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1987-06-23—Публикация

1985-05-27—Подача