(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ПАРАМЕТРОВ ИНТЕГРАЛЬНЫХ СХЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор для виброакустической диагностики вращающихся деталей | 1987 |

|

SU1483282A1 |

| Устройство для допускового контроля амплитудно-частотных характеристик четырехполюсников | 1980 |

|

SU938205A1 |

| Устройство для контроля параметров линейных интегральных микросхем | 1981 |

|

SU981906A1 |

| Устройство для контроля параметров электронных блоков | 1987 |

|

SU1471156A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ТЕХНИЧЕСКОГО СОСТОЯНИЯ ДВИГАТЕЛЕЙ ВНУТРЕННЕГО СГОРАНИЯ И ЭКСПЕРТНАЯ СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1999 |

|

RU2175120C2 |

| Устройство для допускового контроля амплитудно-частотной характеристики четырехполюсника | 1982 |

|

SU1114982A1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ ТЕХНИЧЕСКОГО СОСТОЯНИЯ ДВИГАТЕЛЯ ВНУТРЕННЕГО СГОРАНИЯ И ЭКСПЕРТНАЯ СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2005 |

|

RU2293962C1 |

| Устройство для контроля электрических параметров кварцевых резонаторов | 1978 |

|

SU779927A1 |

| Устройство для контроля границы теплогидравлической устойчивости парогенерирующего канала | 1984 |

|

SU1240152A1 |

| Устройство для контроля диаметров | 1983 |

|

SU1185082A1 |

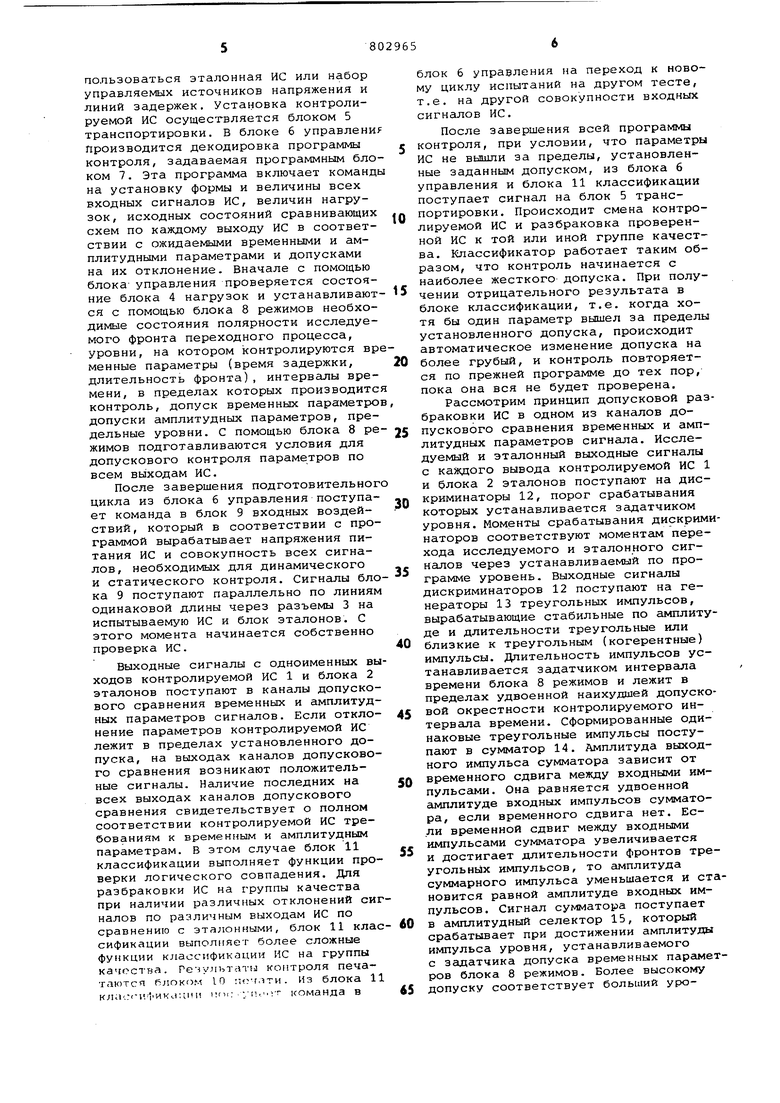

Изобретение относится к контроль но-измерительной технике контроля п раметров интегральных схем для разбраковки готовой продукции по классам допусков. Известно устройство для отыскани неисправных узлов электронной цифровой вычислительной машины, содержащее блок управления, схему сравне ния, эталонный узел и распределительный счетчик 1. Недостатком этого устройства является низкая пр изводительность контроля. Наиболее близким по сущности тех нического решения к изобретению является устройство для классификации интегральных схем, содержащее программный блок и блок управления, со диненный с выходом программного бло соединенные с первым и вторым.выходами блока управления соответственно блок входных воздействий и блок печати, блок классификации, выход которого соединен с входами блоков печати и управления, а первый вход с третьим выходом блока управления, блок эталонов, вход которого соединен с выходом блока входных воздайствий, блок транспортировки, соединенный с четвертым выходом блока уп равления, блок эквивалентных нагрузок, вход которого соединен с четвертым выходом блока управления, а первый и второй выходы - соответственно с выходом блока этгшонов и входом устройства, причем выход блока входных воздействий соединен с выходом устройства Г2. Основными недостатками этого устройства являются отсутствие возможности одновременного контроля временных параметров интегральных схем (ИС) и проверка работоспособности ИС без допусковой классификации. Целью изобретения является повышение производительности и упрощение процесса контроля по динамическим парг1метрам. Достигается это тем, что в устройство, содержащее программный блок и блок управления, соединенный с выходом программного блока, соединенные с первым и вторым вьрсодё№1И блока управления соответственно, блок входных воздействий и блок печати, блок классификации, выход которого соединен с входами блоков печати и управления, а первый вход - с третьим выходом блока управления, блок эталонов, вход которого соединен с выходом блока входных воздействий, блок транспортировки, соединенный с четвертым выходом блока управления, бло эквивалентных нагрузок, вход которог соединен с четвертым выходом блока управления, а первый и второй выходы - соответственно с выходом блока эталонов и входом устройства, причем выход блока входных, воздействий соединен с выходом устройства, введено по два дискриминатора уровней, первые входы которых соединены соответственно с первым и вторым выходами блока эквивалентных нагрузок, по два генератора треугольных импульсов первые входы которых соединены с выходами соответствующих им дискриминаторов уровней, сумматор, два входа которого соединены соответственно с выходами двух генераторов треугольных импульсов, амплитудный селектор, вход которого соединен с выходом сум матора, а выход - с вторым входом блока классификации, по два делителя напряжений, первые входы которых сое динены соответственно с первым и вто рым выходами блока эквивалентных нагрузок, по две схемы сравнения, первые входы которых соединены с выходами соответствующих делителей напряжения, а вторые - соответственно с вторым и первым выходами блока эквивалентных нагрузок , элемент И, два входа которого соединены с выходами схем сравнения, а выход - с третьим входом блока классификации, блок режимов, вход которого соединен с пя тым выходом блока управления, а выход - с вторыми входами обоих дискри минаторов уровней, генераторов треугольных импульсов, делителей напряжения и схем сравнения. На чертеже представлена блок-схема устройства. Оно содержит контролируемую ИС 1, блок 2 эталонов, разъ мы 3, блок 4 эквивалентных нагрузок блок 5 транспортировки, блок 6 управ ления, программный блок 7, блок 8 ре жимов, блок 9 входных воздействий, блок 10 печати, блок 11 классификации, дискриминаторы 12 уровней, гене раторы 13 треугольных импульсов, сум матор 14, амплитудный селектор 15, делители 16 напряжений, схемы 17 ср нения, элемент и 18. Устройство выполнено по многоканальной схеме сравнения в динамике и статике выходных сигналов контрол руемой и эталонной ИС или ее эквивалента. Число каналов сравнения ра но числу выходных контактов ИС. Контролируемая ИС 1 и блок 2 эта лонов подключены через разъемы 3 к блоку 4 эквивалентных нагрузок. Для смены контролируемой ИС и механичес кой сортировки используется блок 5 транспортировки, подключенный по си нальному в лходу к блоку 6 управлени Последний 1-вчяая с П{.ог|.:)ммным блоком 7, с блоком 4 эквивалентных нагрузок, блоком 8 режимов, содержащим в себе ряд задатчиков режимов контроля - задатчик полярности исследуемого фронта переходного процесса, задатчик уровня, задатчик интервала времени, задатчик допуска временных параметров, задатчик допуска амплитудных параметров, задатчик полярности, задатчик предельных уровней, а также с блоком 9 входных воздействий и блоком 10 печати. Каждый из задатчиков, представляющих собой управляемые источники напряжения, имеет количество выходов, равное числу выходов ИС. Все выходы задатчиков и блока 4 нагрузок подключены к каждому каналу допускового сравнения временных и амплитудных параметров так, что каждый канал связан с одним выходом контролируемой и эталонной ИС и с одним выходом каждого задатчика. Каждый канал сравнения со стороны выходов подключен к блоку 11 классификации, который в свою очередь соединен прямой и обратной связью с блоком .6 управления и с блоком 10 печати. Каждый канал допускового сравнения временных и амплитудных параметров сигналов включает два дискриминатора 12 уровней, подключенные к блоку 4 нагрузки и через разъемы 3 к контролируемой и эталонной ИС, а также к задатчику уровня блока 8 режимов. Выходы дискриминаторов уровней соединены с входами генераторов 13 треугольных импульсов, связанных также с задатчиком интервала времени блока 8 режимов, с помощью которого можно устанавливать необходимую длительность треугольных импульсов. Генераторы 13 треугольных импульсов подключены к сумматору 14, выходной сигнал которого поступает на вход амплитудного селектора 15, связанного с задатчиком допуска временных параметров блока режимов. Выход амплитудного селектора 15 подключен к входу блока 11 классификации. Каждый выход контролируемой и эталонной ИС подключен к делителям 16 напряжения и схемам 17 сравнения. Последние подключены по управляющим входам к задатчику допуска амплитудных параметров и к згщатчику полярности блока 8 режимов соответственно. Выходы схем сравнения поступают на элемент И 18, который подключен со стороны выхода к блоку 11 классификации. Работает устройство следующим образом. Контролируемая ИС 1 и блок 2 эталонов, помещенные в контейнеры и подключенные к их контактам, устанавливаются в контактные резъемы 3, соединенные со стороны выходов с: бплком 4 эквивaлeнтнtJx нагрузок, ими1и-рующим реальные условия pafjivnj и.;. В качестве блока -jTanoHCMi М1.«1г и-пользоваться эталонная ИС или набор управляемых источников напряжения и линий задержек. Установка контролируемой ИС осуществляется блоком 5 транспортировки. В блоке 6 управлен Производится декодировка программы контроля, задаваемая программным бл ком 7. Эта программа включает коман на установку формы и величины всех входных сигналов ИС, величин нагрузок, исходных состояний сравнивающи схем по каждому выходу ИС в соответ ствии с ожидаемыми временными и амплитудными параметрами и допусками на их отклонение. Вначале с помощью блока- управления проверяется состоя ние блока 4 нагрузок и устанавливают ся с помощью блока 8 режимов необходимые состояния полярности исследуемого фронта переходного процесса, уровни, на котором контролируются вр менные параметры (время задержки, длительность фронта), интервешы времени, в пределах которых производитс контроль, допуск временных параметро допуски амплитудных параметров, предельные уровни. С помощью блока 8 ре жимов подготавливаются условия для допускового контроля параметров по всем вь1ходам ИС. После завершения подготовительног цикла из блока б управления поступает команда в блок 9 входных воздействий, который в соответствии с программой вырабатывает напряжения питания ИС и совокупность всех сигналов, необходимых для динамического и статического контроля. Сигналы бло ка 9 поступают параллельно по линиям одинаковой длины через разъемы 3 на испытываемую ИС и блок эталонов. С этого момента начинается собственно проверка ИС. Выходные сигналы с одноименных вы ходов контролируемой ИС 1 и блока 2 эталонов поступают в каналы допускового сравнения временных и амплитудных параметров сигналов. Если отклонение параметров контролируемой ИС лежит в пределах установленного допуска, на выходах каналов допускового сравнения возникают положительные сигналы. Наличие последних на всех выходах каналов допускового сравнения свидетельствует о полном соответствии контролируемой ИС требованиям к временным и амплитудным параметрам. В этом случае блок 11 классификации выполняет функции проверки логического совпадения. Для разбраковки ИС на группы качества при наличии различных отклонений сиг налов по различным выходам ИС по сравнению с эталонными, блок 11 клас сификации выполняет более сложные функции классификации ИС на группы качества. Речультат 1 контроля печатаются блоком 10 :;от.1ти . Из блока 11 кла,:-1.гико;1и 11 1(и: гуц.игг команда в блок 6 управления на переход к новому циклу испытаний на другом тесте, т.е. на другой совокупности входных сигналов ИС. После завершения всей программы контроля, при условии, что параметры ИС не вышли за пределы, установленные заданным допуском, из блока 6 управления и блока 11 классификации поступает сигнал на блок 5 транспортировки. Происходит смена контролируемой ИС и разбраковка проверенной ИС к той или иной группе качества. Классификатор работает таким образом, что контроль начинается с наиболее жесткого допуска. При получении отрицательного результата в блоке классификации, т.е. когда хотя бы один параметр вышел за пределы установленного допуска, происходит автоматическое изменение допуска на более грубый, и контроль повторяется по прежней программе до тех пор, пока она вся не будет проверена. Рассмотрим принцип допусковой разбраковки ИС в одном из каналов допускового сравнения временных и амплитудных параметров сигнала. Исследуемый и эталонный выходные сигналы с кавдого вывода контролируемой ИС 1 и блока 2 эталонов поступают на дискриминаторы 12, порог срабатывания которых устанавливается задатчиком уровня. Моменты срабатывания дискриминаторов соответствуют моментciM перехода исследуемого и эталонного сигналов через устанавливаемый по программе уровень. Выходные сигналы дискриминаторов 12 поступают на генераторы 13 треугольных импульсов, вырабатывающие стабильные по амплитуде и длительности треугольные или близкие к треугольным (когерентные) импульсы. Длительность импульсов устанавливается задатчиком интервала времени блока 8 режимов и лежит в пределах удвоенной наихудшей допусковой окрестности контролируемого интервсша времени. Сформированные одинаковые треугольные импульсы поступают в сумматор 14. Амплитуда выходного импульса сумматора зависит от временного сдвига между входными импульсс1ми. Она равняется удвоенной амплитуде входных импульсов сумматора, если временного сдвига нет. Если временной сдвиг между входными импульсами сумматора увеличивается и достигает длительности фронтов треугольньах импульсов, то амплитуда суммарного импульса уменьшается и становится равной амплитуде входных импульсов. Сигнал сумматора поступает в амплитудный селектор 15, который срабатывает при достижении амплитуды импульса уровня, устанавливаемого с задатчика допуска временных парг1метров блока 8 режимов. Более высокому опуску соответствует больший уровень сравнения, однако, не превышающий удвоенной амплитуды треугольных импульсов. Срабатывание амплитудного селектора 15 свидетельствует о том, что сигналы контролируемой ИС и блока 2 эталонов смещены во времени на заданном уровне напряжений не более, чем на величину заданного допуска, Выходной сигнал амплитудного селектора 15 поступает в блок 11 классификации.

Для контроля статических параметров выходные сигналы с каждого выхода контролируемой ИС и блока 2 эталонов поступают на управляющие делители 16 напряжений и потенциальные схемы 17 сравнения. Коэффициент деления делителей 16 устанавливается задатчиком допуска амплитудных параметров блока 8 режимов. С помощью задатчика полярности на стадии подготоки испытаний устанавливается режим работы схем 17 сравнения для положительных или отрицательных сигналов.

Схемы 17 сравнения проверяют превышение неделенных выходных сигналов контролируемой ИС и блока 2 эталонов над деленными выходными сигналами соответственно блока 2 эталонов и контролируемой ИС. Одновременное сра батывание схем 17 сравнения свидетельствует о том, что амплитуда сигнала (или выходное напряжение ИС в измерительном промежутке времени) лежит в требуемой допусковой окрестности. Это проверяет элемент И 18, подключенный к схемам 17 сравнения. Выходные сигналы элемента И 18 поступают в блок 11 классификации, где производится анализ выходных сигналов всех каналов сравнения динамических и статических параметров ИС.

При практической реализации предлагаемого устройства основную трудность представляет выполнение высокочастотных дискриминаторов 12 и генераторов 13 треугольных импульсов. Для этого используются каскады на лавинных транзисторах, туннельных диодах и диодах с накоплением заряда

Формула изобретения

Устройство для контроля параметров интегральных схем, содержащее программный блок и блок управления, соединенный с выходом программного блока, соединенные с первым и вторым выходами блока управления соответственно, блок входных воздействий и

блок печати, блок классификации, выход которого соединен с входами блоков печати и управления, а первый вход - с третьим выходом блока управления, блок эталонов, вход которого соединен с выходом блока входных воздействий, блок транспортировки, соединенный с четвертым выходом блока управления, блок эквивалентных нагру зок, вход которого соединен с четвертым выходом блока управления, а первый и второй выходы - соответственно с выходом блока эталонов и входом устройства, причем выход блока входных воздействий соединен с выходом устройства, отличающееся тем, что, с целью повышения производительности и упрощения процесса контроля по динамическим параметрам для каждого из контролируемых параметров, в устройство введено по два дискриминатора уровней, первые входы которых соединены соответственно с первым и вторым выходами блока эквивалентных нагрузок, по два генератора треугольных импульсов, первые входы которых соединены с выходами соответствующих им дискриминаторов уровней, сумматор, два входа которого соединены соответственно с выходами двух генераторов треугольных импульсов, амплитудный селектор, вход которого соединен с выходом сумматора, а выход - с вторым входом блока классификации, по два делителя напряжений, первые входы которых соединены соответственно с первым и вторым выходами блока эквивалентных нагрузок, по две схемы сравнения, первые входы которых соединены с выходами соответствукяцих .делителей. напряжения, а вторые - соответственно с вторым и первьвд выходами блока эквивалентных нагрузок, элемент И, два входа которого соединены с выходами схем сравнения, а выход - с третьим входом блока классификации, блок режимов, вход которого соединен с пяты выходом блока управления, а выход - с вторыми входами обоих дискриминаторюв уровней, генераторов треугольных импульсов,делитель напряжения и схем сравнения.

Источники информации, принятые во внимание при экспертизе

G Об F 15/46, G 01 R 31/28, 1961.

17

/7

Ir

Tj

J5

J

Q

/5

канал ср обмени ft

Авторы

Даты

1981-02-07—Публикация

1972-11-16—Подача