(54) САМОНАСТРАИВАЮЩИЙСЯ РЕГУЛЯТОР ледовательно соединенные второй ам литудный детектор, пятый ключ, тре тий блок памяти и блок деления, вы которого соединен со вторым входом блока умножения, а второй вход чер первый амплитудный детектор - с вы дом второго полосового фильтра, вы ход первого полосового фильтра сое динён со входом второго амплитудно детектора, первый вход второго клю ча соединен с первым входом четвер того ключа и вторым входом пятого ключа, выход фазового детектора сое динен со вторыми входами второго и четвертого ключей, выход второго блока -памяти соединен со входом инт ратора, выход генератора пробных сигналов через первый ключ соединен со входом сумматора, выход генератора опорной частоты соединен со вторым входом первого ключа, а через первый формирователь импульсов со вторым входом третьего ключа, выходы первого и второго-блоков памяти соединены со вторыми сходами сооть ётствен.но второго и первого блоков сравнения. На фиг. 1 представлена блок-схем самонастраивающегося регулятора с подстройкой ФЧХ; на фиг. 2 - временная диаграмма работы формирователей импульсов. Выход генератора 1 пробных сигиа лов через первый ключ 2 и cy 4мaтop 3 соединен со входом блокгг 4 регулирования и со входом модели 5 замкнутой системы, а выходы блока 4 регулирования и модели 5 замкнутой система через первый б и второй 7 полосовые фильтры подключены ко входам фазового детектора 8, выход которого соединен с.коммутирующими входами второго .9 и четвертого 10 ключей; управляющие входы второго 9 четвертого-10.и пятого 11 ключей через второй формирователь 12 импульсов соединены с выходом генератора 13 опорной частоты, коммутирую щие входы второго 9 и четвертого 10 ключей подключены к выходу фазового детектора .8, коммутирукнцйй вход ПЯТО1-О кпюча 1 - к выходу вто рого амплитудного детектора 14, динен с выходом первого амплитудного детектора 22, вход которого сое.динен с Ьыходом второго полосового фильтра 7 и третьего блока 17 памяти, а выход блока 20 умножения чере второй функциональный преобразователь 23, второй блок 24 сравнения, второй вход которой подключен к вывыход соединен с выходом первого полосового фильтра 6; выход Бторого 9, четвертого 10 и пятого 11 ключей соответственно соединены со входами первого 15, второго 16 и третьего 17 блоков памяти, причем выходы первого 15 и второго 16 блоков памяти соединены через первый блок IS сравнения со входом первого функционального преобразователя 19, выход которого подключен на первый вход блока 20 умножения, второй вход которого через блок 21 деления, соеходу первого блока 15 памяти, третий ключ 25, управляющий вход которого соединен через первый формирователь 26 импульсов с выходом генератора 13 опорной частоты, и четвертый блок 27 памяти соединен со входом интегратора 28, выход которого подключен к управляющему входу блока 4 регулирования; управляющий вход первого ключа 2 соединен с выходом генератора 13 опорной частоты. Регулятор работает следующим образом. Когда первый ключ 2 замкнут, сигнал с генератора 1 пробных сигналов поступает через сумматор 3 на вход блока 4 регулирования, выходной сигнал которого имеет вид: y(t) Vo(t)(uJni t )f AjSiM.() Vo(t)- A3Mh(0 t-fvfa) A3 /A,,A,COs(.; ур.пг-лч-гг AjCOS fj YoU) - выходная координата, обусловленная задающим воздей; ствием ); А - амплитуда, обусловленная пробным сигналом; - частота пробного сигнала) 4 - значение ФЧХ основного контура на частоте Ai - амплитула, обусловленная наличием помех на частоте J, (помехи на других частотах на точность подстройки ФЧХ влияния практически не окажут, так как будут сильно ослабляться полосовыми фильтрами); - сдвиг ФЧХ, вносимый псяиехой на частоте U) После прохояадения сигналом первоо полосового фильтра 6 на первом ходе фазового детектора 8 сигнал меет вид: 2i(t)A,s(i (uJnt t j Усо), де f ф - фазовый сдвиг, вносимый псшосовым фильтром. Одновременно на второй вход фаового детектора 8 поступает пробный игнал с генератора 1, прошедший чеез модель 5 замкнутой системы и олосовой фильтр 7, определяемый по ормуле: )AMSiMiWntf M -t p), 1де - амплитуда сигнала после прохождения модели эамк нутои системы (коэффициент передачи основног контура на частоте и) равен коэффициенту пере дачи модели замкнутой системы; f - значение желаемой ФЧХ на частоте сОп,задаваемое моделью замкнутой системы. Тогда на выходе фазового детектора 8 будет сигнал вида: .u, ,-uJnt-V M-Sa,, И) который запоминается первым блоком 15 памяти. Когда первый ключ 2 разомкнут, пробный сигнал с генератора 1 пробных сигналов в блок 4 регулирования не поступает и на выходе первого полосового фильтра б сигнал Имеет -вид: Z,U) AjSmluJntt z + f го), а на выходе фазового детектора 8 имеем: u;,U)nt 4j 4 -Jn - H-44, .i Решая совместно уравнения(l) и(2 .-з-.„ .| ;11 11Й;а.., получаем алгоритм Д -Qrc5 n - S«nlДl-Л), который позволяет устранить влия-. ние помехи на подстройку ФЧХ основного контура на. частоте д)п Значение А2 запоминается вторым блоком 16 памяти. Амплитуда А , А выделяется первым амплитудным детектором 22,а амплитуда Л - вторым амплитудным детектором 14 и запоминаетря третьим блоком 17 памяти. В- первом блоке 18- сравнения опре деляется разность Л),в первом функциональном преобразователе 19 определяется функция синуса от дан ной разности. Блок 21 деления вычи ляет отношение Aj/A. На блоке 20 умножения происходит вычисление пр изведения {Aj-u,),H вы;«одиой сйгнёьл подается на второй функцион ный преобразователь 23, где берется функция 4 5 п{д1-д). На втором блоке 24 сравнения опр деляется разность

vf -vf A -QrCS«l1 l- uintAj.-AlV. Сигнал, пропорциональный этой разнести, через третий ключ 25 поступает 5

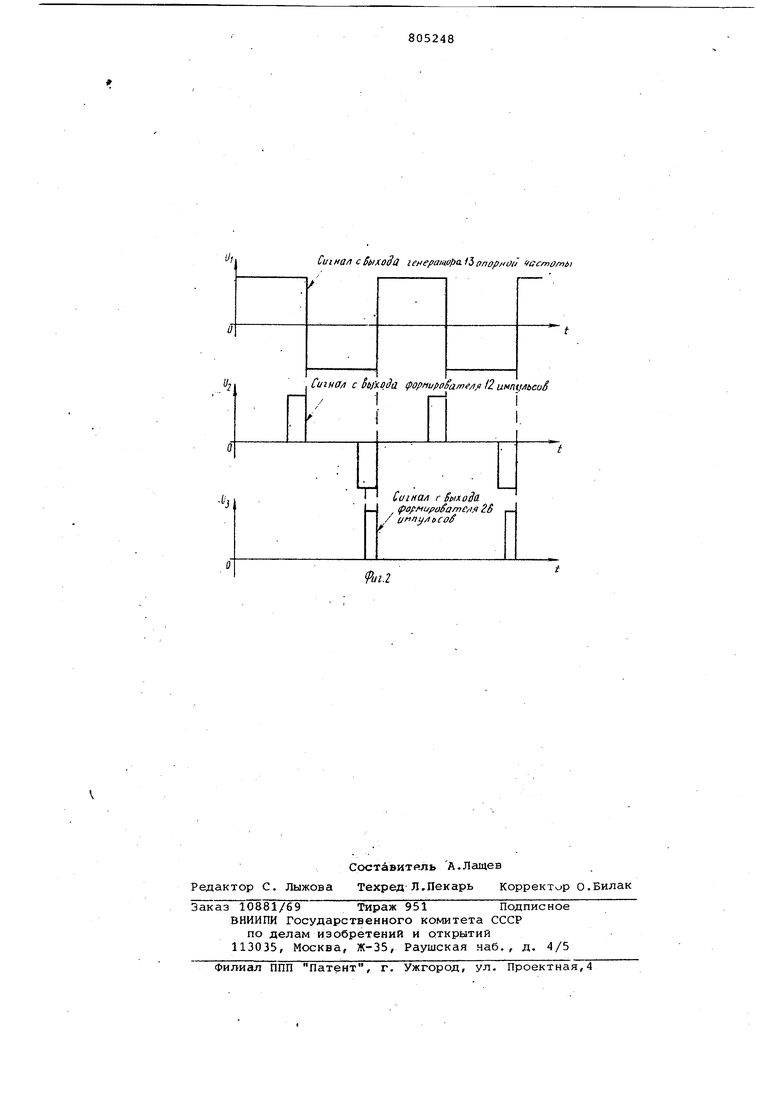

Формула изобретения на четвертый блок 27 памяти, выход которого соединен со входом интегратора 28, выходной сигнал которого через управляющий вхгц перестраивает з.начение постоянной ьремени в блоке 4 регулирования. Ключи 9 - 11 служат для того, чтобы в зависимости от сигнала с ге-/ нератора 13 опорной частоты подключать к выходу фазового детектора 8 входы блоков памяти 15(когда первый ключ 2 замкнут, замкнут и второй ключ 9J и 14, когда первый ключ 2 разомкнут (второй ключ 9 размыкается, а четвертый ключ 10 за1 икается, Одновременно, когда первый ключ 2 разомкнут, подключается и выход второго амплитудного детектора 14(пятый ключ 11 замыкается)ко входу блока 17 памяти. Формирователи 12 и 26 И1 4п:льсов служат для того, чтобы запоминание значений соответствующих величин происходило после того, как закончатся переходные процессы в основном контуре и первом полосовом фильтре 6. Временная диаграмма работы этих формирователей приведена на фиг. 2. Ключи 2,9 и 10 пои положительных импульсах замыкаются, а при нулевом и отрицательном значении управляющих сигналов размыкаются; пятый ключ 11 замыкается при отрицательньзх импульсах. Импульсы с формирователя 26 идут Меньшей .плительности, 1ем с формирователя 12. Это объясняется наличием переходных процессов и конечным быстродействием устройств, реализующих данньй алгоритм. Длительность импульсов генератора 13 опорной частоты выбирается из расчета, чтобы переходные процессы из-за коммутации ключей в основном контуре , полосовом фильтре ( и устройствах, реализующих данньлй алгоритм, успевали заканчиваться. Предложенная самонастраивающаяся САР с подстройкой ФЧХ позволяет повысить помехозащищенность системы, что в свою очередь приводит к повышению точности подстройки ФЧХ и применительно к каналу регулирования частоты вращения вал. , ..зотурбинного двигателя позволит уменьшить погрешность подстройки ФЧХ до 17 , что приводит к уменьшению перерегулирования на 6% и уменьшению времени регулирования на 0,5 с, это обеспечивает увеличение тяги на 0,5%, вследствие чего ожидаемая экономическгч эффективность составит 2-3 тыс.р в год на один двигатель. Самонастраивающийся регулятор, содержащий интегратор, последовательно соединенные сумматор, блок регулирования, первый полосовой фильтр и фазовый детектор и последовательно соединенные генератор пробных синалов, модель блока регулнрованич и второй полосовой фильтр, выход .которого соединен со вторым входом фазового детектора, а вы.ход интегратора соединен со вторым входом блока регулирования, о тличающийся тем, что, с целью повьЕиения помехоустойчивости регулятора, он содержит первый ключ первый формирователь импульсов, первый амплитудный детектор, последовательно соединенные генератор опорной .частоты, второй формирователь импульсов, второй ключ, первый блок памяти, первый блок сравнения, первый функциональный преобразователь, блок умножения, второй функциональный преобразователь, второй блок сравнения, третий ключ и второй блок памяти, последователькр соединенные четвертый ключ и второй блок и последовательно соединенные второй амплитудный детектор, ПЯТЫЙ ключ, третий блок памяти и блок деления, выход которого соединен со вторым входом блока умножения, а второй вход через первый амплитудный детектор - с выходо.м второго полосового фильтра, выход первого полосового фильтра соединен со входом второго амплитудного детектора, первый вход второго ключа соединен с первым входом четвертого ключа и вторым входом пятого ключа, выход фазового детектора соединен со вторыми входами второго и четвертого ключей, выход второго блока памяти соединен со входом интегратора, выход генератора пробных сигналов через первый ключ соединен со входом сумматора, выход генератора опорной частоты соединен со вторым входом первого ключа, а через первый формирователь импульсов - со вторым входом третьего ключа, выходы первого и второго блоков памяти соединены со вторыми входами соответственно второго и первого блоков сравнения .

Источники информации, принятые во внимание при экспертизе

1.Патент США № 3287615 , кл.318-2 опублик. 28.11.66.

2.Кухтенко В. И. Динамика самонастраивающихся систем со стабилизацией частотных характеристик. М., Машиностроение, 1970, с. I

(прототип) .

Ji

Сигнал сBiiixoda leHepamofta.ibonopfaiJ facma/nti

| название | год | авторы | номер документа |

|---|---|---|---|

| АДАПТИВНАЯ СИСТЕМА УПРАВЛЕНИЯ | 2007 |

|

RU2339988C1 |

| Устройство для измерения фазочастотных характеристик | 1985 |

|

SU1385097A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СИГНАЛОВ СТАНЦИИ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1991 |

|

RU2014630C1 |

| САМОНАСТРАИВАЮЩАЯСЯ СИСТЕМА УПРАВЛЕНИЯ | 1992 |

|

RU2068196C1 |

| ФАЗОВЫЙ ПАРАМЕТРИЧЕСКИЙ ГИДРОЛОКАТОР | 1995 |

|

RU2097785C1 |

| Устройство для измерения уровней высокочастотных и сверхвысокочастотных гармонических сигналов | 1983 |

|

SU1177753A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ РАБОТЫ РАДИОСТАНЦИЙ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2016 |

|

RU2617112C1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ РАБОТЫ РАДИОСТАНЦИЙ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2008 |

|

RU2357363C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО РАЗДЕЛЕНИЯ РАДИОИМПУЛЬСОВ ПО НЕСУЩЕЙ ЧАСТОТЕ | 1983 |

|

SU1840996A1 |

| Синтезатор частоты с частотной модуляцией | 1986 |

|

SU1345343A1 |

Сигна/i с etuKoJa форнираёате/ 12 и мльсиб

Л I

Г Cm нал г SModa. fafMLtfiafarne/ifl 26 / i/fny/tucoe

Авторы

Даты

1981-02-15—Публикация

1978-09-29—Подача