дополнительного элемента И, выход которого соедннен с единичным входом первого триггера, прямой и инверсный выходы которого соединены соответственно со вторыми входами пятого и вто|зого дополнительных элементов И, выЬоды которых соединены с соответст- , вующими входс1ми первого элемента ИЛИ, а выход первого дополнительного элемента И соединен с единичным входом второго триггера, прямой и инверсный выходы которого соединены соответственно со вторыми входами третьего и шестого элементов И, выходы которых соединены с соответствующими входами второго элемента ИЛИ.

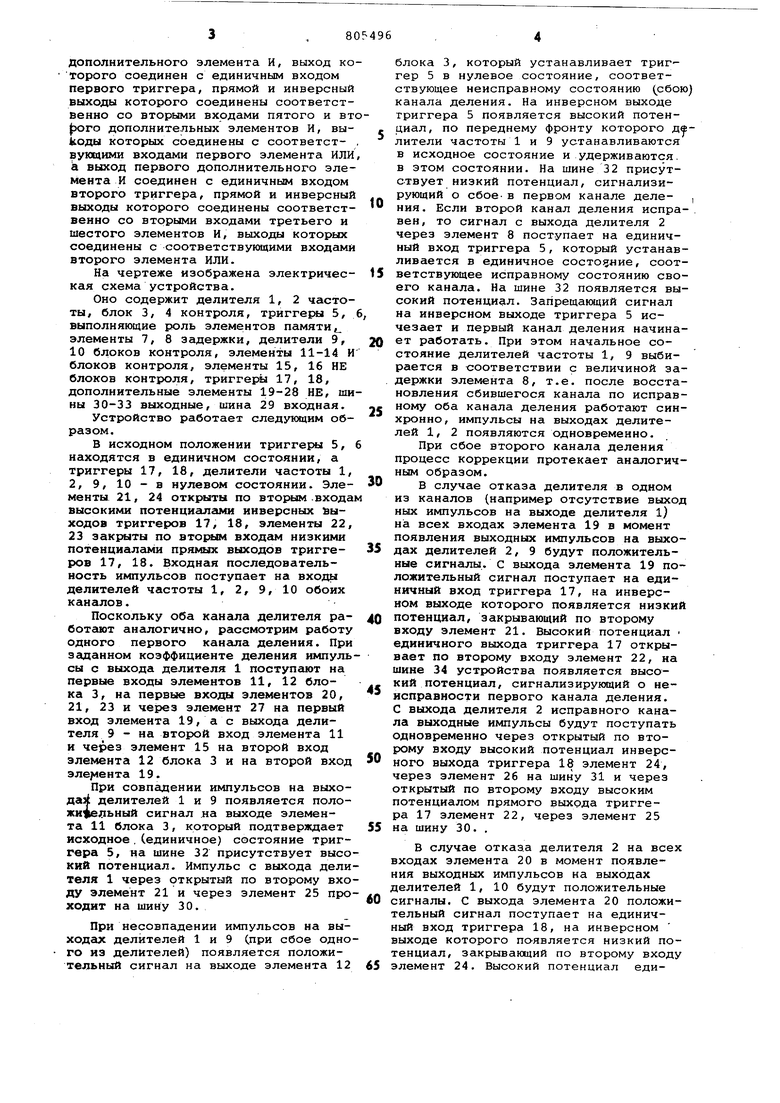

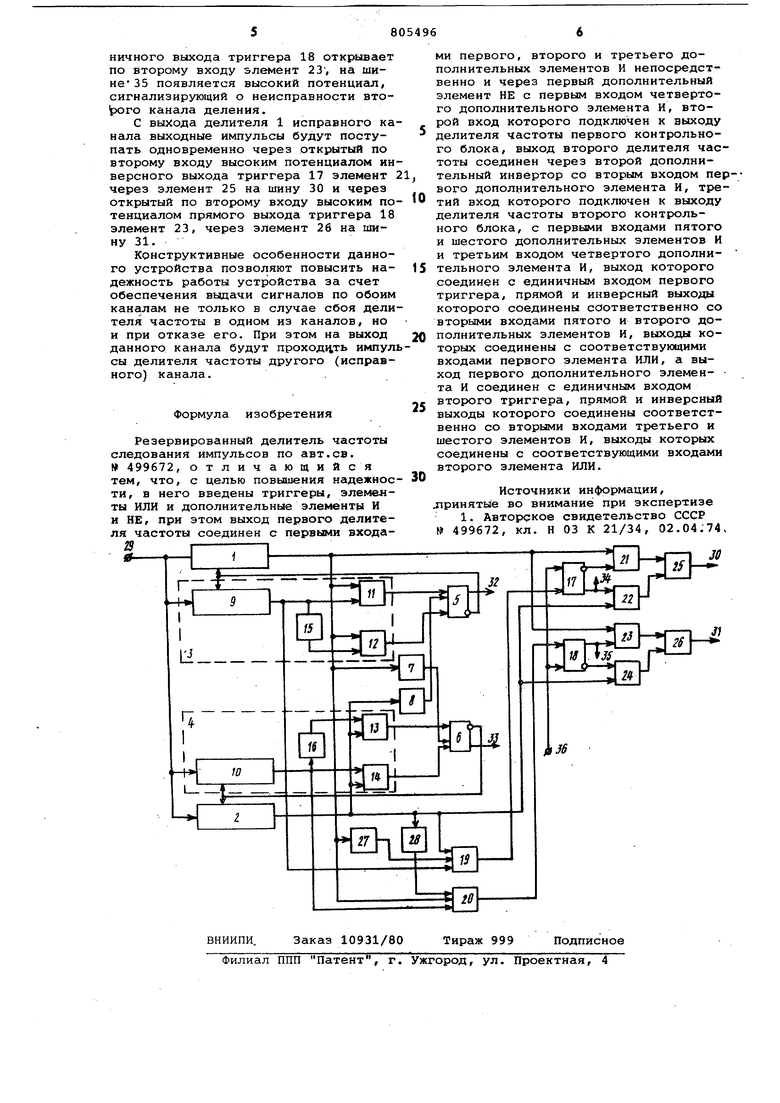

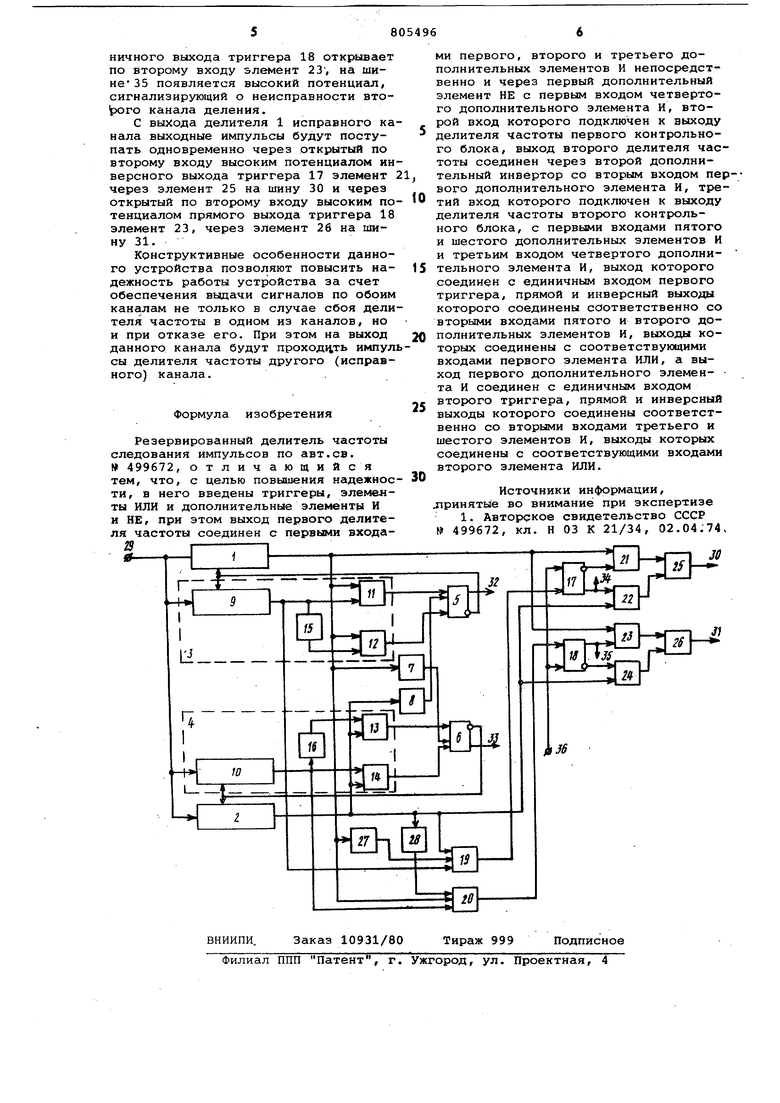

На чертеже изображена электрическая схема устройства.

Оно содержит делителя 1, 2 частоты, блок 3, 4 контроля, триггеры 5, 6 выполняющие роль элементов памяти, элементы 7, 8 задержки, делители 9, 10 блоков контроля, элементы 11-14 И блоков контроля, элементы 15, 16 НЕ блоков контроля, триггеры 17, 18, дополнительные элементы 19-28 НЕ, шины 30-33 выходные, шина 29 входная.

Устройство работает следующим образом.

В исходном положении триггеры 5, 6 находятся в единичном состоянии, а триггеры 17, 18, делители частоты 1, 2, 9, 10 - в нулевом состоянии. Элементы 21, 24 открыты по вторым .входам высокими потенциалами инверсных выходов триггеров 17, 18, элементы 22, 23 закрыты по ВТОЕКДМ низкими потенциалами прямых выходов триггеров 17, 18. Входная последовательность импульсов поступает на входы делителей частоты 1, 2, 9, 10 обоих каналов.

Поскольку оба канала делителя работгиот аналогично, рассмотрим работу одного первого кангша деления. При заданном коэффициенте деления импульсы с выхода делителя 1 поступают на первые входы элементов 11, 12 блока 3, на первые входы элементов 20, 21, 23 и через элемент 27 на первый вход элемента 19, а с выхода делителя 9 - на второй вход элемента 11 и через элемент 15 на второй вход элемента 12 блока 3 и на второй вход эле иента 19.

При совпадении импульсов на выхода делителей 1 и 9 появляется положиуе 11ьный сигнал .на выходе элемента 11 блока 3, который подтверждает исходное,(единичное) состояние триггера 5, на шине 32 присутствует высокий потенциал. Импульс с выхода делителя 1 через открытый по второму входу элемент 21 и через элемент 25 проходит на шину 30.

При несовпадении импульсов на выходах делителей 1 и 9 (при сбое одного из делителей) появляется положительный сигнал на выходе элемента 12

блока 3, который устанавливает триггер 5 в нулевое состояние, соответствующее неисправному состоянию (сбою канала деления. На инверсном выходе триггера 5 появляется высокий потенциал, по переднему фронту которого д лители частоты 1 и 9 устанавливаются в исходное состояние и удерживаются, в этом состоянии. На шине 32 присутствует низкий потенциал, сигнализирующий о сбое-в первом канале деления. Если второй канал деления исправен, то сигнал с выхода делителя 2 через элемент 8 поступает на единичный вход триггера 5, который устанавливается в единичное состояние, соответствующее исправному состоянию своего канала. На шине 32 появляется высокий потенциал. Запрещающий сигнал на инверсном выходе триггера 5 исчезает и первый канал деления начинает работать. При этом начальное состояние делителей частоты 1, 9 выбирается в соответствии с величиной задержки элемента 8, т.е. после восстановления сбившегося канала по исправному оба канала деления работают синхронно, импульсы на выходах делителей 1, 2 появляются одновременно.

При сбое вторюго канала деления процесс коррекции протекает аналогичным образом.

В случае отказа делителя в одном из каналов (например отсутствие выход ных импульсов на выходе делителя 1) на всех входах элемента 19 в момент появления выходных импульсов на выходах делителей 2, 9 будут положительные сигналы, с выхода элемента 19 положительный сигнал поступает на единичный вход триггера 17, на инверсном выходе которого появляется низкий потенциал, закрывающий по второму входу элемент 21. Высокий потенциал единичного выхода триггера 17 открывает по второму входу элемент 22, на шине 34 устройства появляется высокий потенциал, сигнализирующий о неисправности первого канала деления. С выхода делителя 2 исправного канала выходные импульсы будут поступать одновременно через открытый по второму входу высокий потенциал инверсного выхода триггера 18 элемент 24, через элемент 26 на шину 31 и через открытый по второму входу высоким потенциалом прямого выхода триггера 17 элемент 22, через элемент 25 на шину 30. .

В случае отказа делителя 2 на всех входах элемента 20 в момент появления выходных импульсов на выходах делителей 1, 10 будут положительные сигналы. С выхода элемента 20 положительный сигнал поступает на единичный вход триггера 18, на инверсном выходе которого появляется низкий потенциал, закрывающий по второму входу элемент 24. Высокий потенциал единичного выхода триггера 18 открывает по второму входу элемент 23, на шине 35 появляется высокий потенцигш, сигнализирующий о неисправности канала деления. С выхода делителя 1 исправного ка нала выходные импульсы будут поступать одновременно через открытый по второму входу высоким потенциалом ин версного выхода триггера 17 элемент через элемент 25 на шину 30 и через открытый по второму входу высоким по тенциалом прямого выхода триггера 18 элемент 23, через элемент 26 на шину 31. Конструктивные особенности данного устройства позволяют повысить иадежность работы устройства за счет обеспечения выдачи сигналов по обоим каналам не только в случае сбоя дели теля частоты в одном из каналов, но и при отказе его. При этом на выход данного канала будут проходцть импул сы делителя частоты другого (исправного) канала. Формула изобретения Резервированный делитель частоты следования импульсов по авт.св. 499672, отличающий с я тем, что, с целью повышения надежнос ти, в него введены триггеры, элементы ИЛИ и дополнительные элемент(:1 И и НЕ, при этом выход первого делителя частоты соединен с первыми входами первого, второго и третьего дополнительных элементов И непосредственно и через первый дополнительный элемент НЕ с первым входом четвертого дополнительного элемента И, второй вход которого подключен к выходу делителя частоты первого контрольного блока, выход второго делителя частоты соединен через второй дополнительный инвертор со вторым входом первого дополнительного элемента и, третий вход которого подключен к выходу делителя частоты второго контрольного блока, с первыми входами пятого и шестого дополнительных элементов И и третьим входом четвертого дополнительного элемента И, выход которого соединен с единичным входом первого триггера, прямой и инверсный выходы которого соединены соответственно со вторыми входами пятого и второго дополнительных элементов И, выходы которых соединены с соответствующими входами первого элемента ИЛИ, а выход первого дополнительного элемен- та И соединен с единичным входом второго триггера, прямой и инверсный выходы которого соединены соответственно со вторыми входами третьего и шестого элементов И, выходы которых соединены с соответствующими входами второго элемента ИЛИ. Источники информации, принятые во внимание при экспертизе 1. Авторркое свидетельство СССР 499672, кл. Н 03 К 21/34, 02.04.74.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный делитель частоты | 1979 |

|

SU822375A1 |

| Устройство для контроля резервированного генератора | 1980 |

|

SU892740A2 |

| Резервированный трехканальный генератор импульсов | 1981 |

|

SU946019A1 |

| Резервированный делитель частоты | 1985 |

|

SU1330756A1 |

| Трехканальный резервированный синхронизатор | 1984 |

|

SU1190558A1 |

| Резервированный счетчик | 1982 |

|

SU1040603A1 |

| Устройство для контроля -разрядного счетчика | 1977 |

|

SU664298A1 |

| Резервированный делитель частоты | 1978 |

|

SU752809A1 |

| Резервированный делитель частоты | 1984 |

|

SU1188882A1 |

| Генератор импульсов с управляемойчАСТОТОй СлЕдОВАНия | 1979 |

|

SU813796A2 |

Авторы

Даты

1981-02-15—Публикация

1979-04-27—Подача