(54) РЕЗЕРВИРОВАННЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированный делитель частоты | 1977 |

|

SU696607A2 |

| Резервированный делитель частоты | 1974 |

|

SU499672A1 |

| Резервированный двухканальный делитель частоты | 1982 |

|

SU1108625A1 |

| Резервированное счетное устройство | 1977 |

|

SU705687A1 |

| Резервированный делитель частоты сле-дОВАНия иМпульСОВ | 1979 |

|

SU805496A2 |

| Резервированный делитель частоты | 1979 |

|

SU822375A1 |

| Многоканальный резервированныйгЕНЕРАТОР | 1979 |

|

SU817720A1 |

| Резервированный генератор импульсов | 1981 |

|

SU999186A1 |

| Многоканальный резервированный генератор | 1982 |

|

SU1072051A1 |

| Резервированный формирователь импульсов | 1985 |

|

SU1272510A1 |

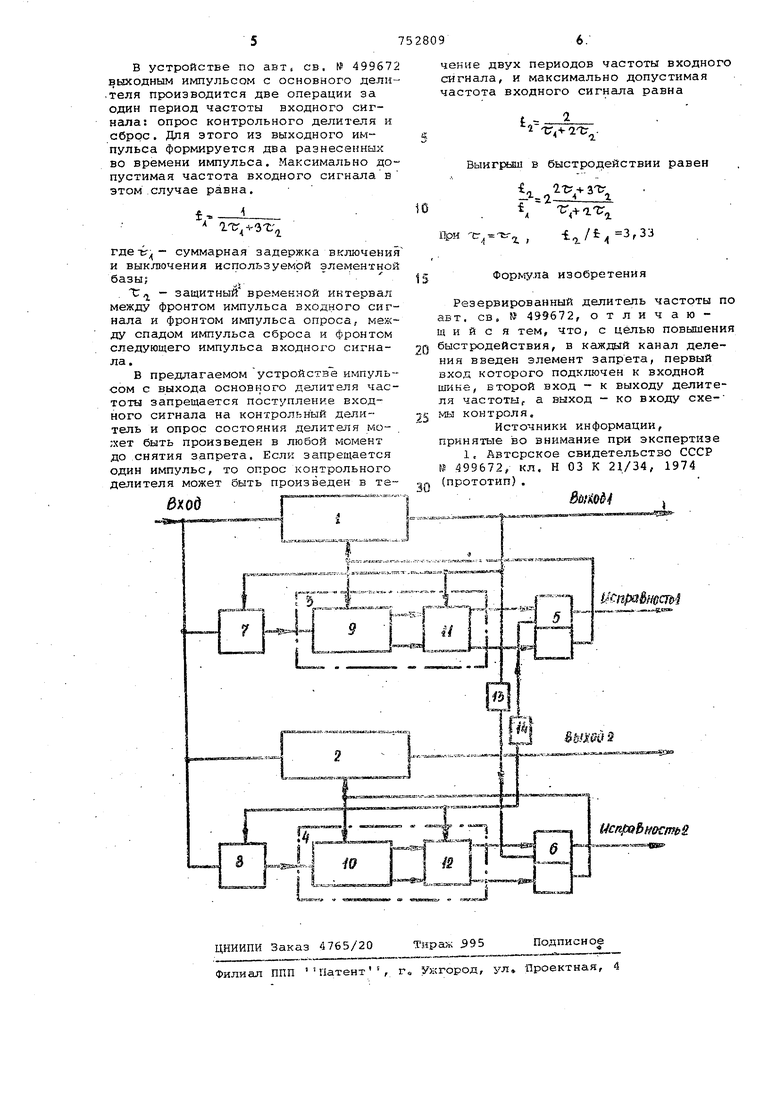

Изобретение относится к электронным цифровым системам с резервировани ем и может быть использовано в качестве хранителя времени в сочетании с высокостабильным генератором. По основному авт.св. № 499672 известен резервированный делитель частоты, содержащий два канала деления, каждый из которых состоит из делителя частоты, схемы контроля и элемента памяти, причем входы элемента памяти каждого канала подключены к выходам схемы контроля, а выход - ко входусхемы контроля и входу установ ки делителя частоты,, выход которого соединен со входом элемента памяти другого канала деления. Схема контроля включает в себя контрольный делитель частоты и выходную логическую 1 . Дпя эффективности контроля исправ ности делителя частоты, входящего в .состав контроля, делают взаимно прос по отношению к коэффициенту деле ния основного делителя частоты. При этом, если оба делителя перед началом, работы устанавливаются в нулевое состояние, то при появлении на выходе основного делителя частоты выходного импульса на контрольном делителе зафиксируется состояние, зависящее от соотношения коэффициентов деления основного и контрольного делителей частоты. С помощью выходной схемы контрольного делителя частоты импульсов с основного делителя.частоты спрашивается это состояние и формируется сигнал, свидетельствующий об исправной работе канала. Для того, чтобы на следующем цикле деления, т.е. при появлении следующего импульса с выхода основного делителя частоты, было зафиксировано то же состояние, необходимо, чтрбы следующий цикл деления начинался снова при нулевых состояниях основного и контрольного делителей частоты. Следовательно, за один период частоты вход входного сигнала по импульсу с выхода основного делителя частоты необходимо осуществлять и опрос состояния контрольного делителя частоты, и сброс его в исходное состояние. Это накладывает ограничение сверху на частоту входного сигнала при заданном быстродействии элементной базы и требует построения сложных схем сброса контрольных делителей частоты, включающих в себя дифференцирующие

цепи, элементы задержки и логические схекы,

Цель изобретения - повышение быстродействия,

Цель достигается тем, что в резервированном делителе частоты, содержащем два канала деления, каждый из которых состоит из делителя частоты, схемр контроля и элемента памяти, в каждый канал деления введен элемент запрета, первый вход которого подключен к входной шине, второй вход к выходу делителя частоты, а выход ко входу схемы контроля.

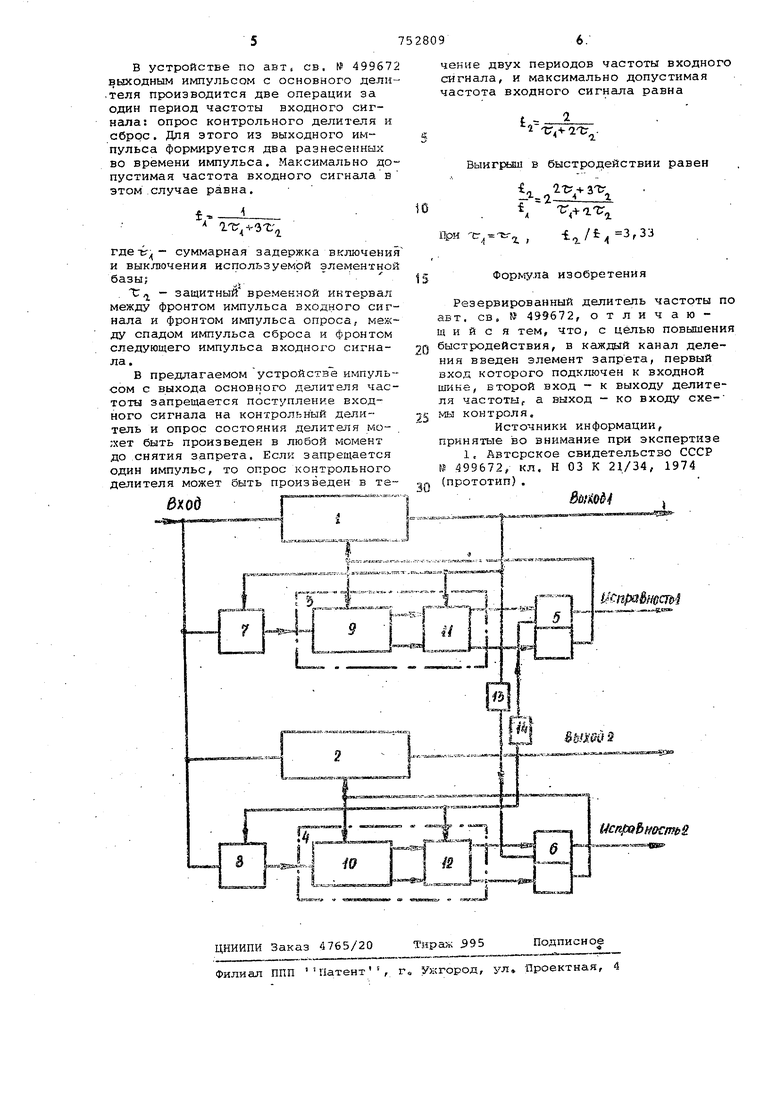

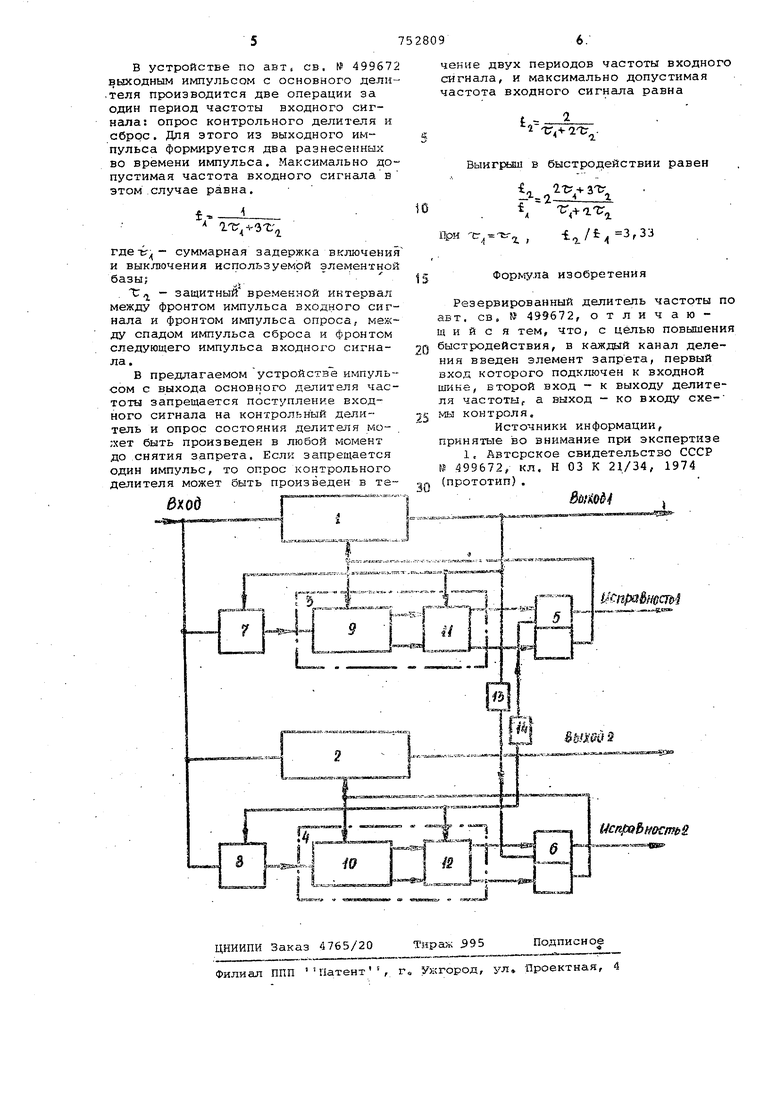

На чертеже представлена структурная схема резервированного делителя частоты.

Делитель состоит из делителей 1 и 2 частоты, схем 3 и 4 контроля, элементов 5 к б памяти, элементов 7 и 8 запрета, контрольных делителей 9 и 10 частоты, выходных схем 11 и 12, элементов 13 и 14 задержки.

Входная последовательность импульсов поступает на входы делителей 1 и 2 частоты и через элементы 7 и 8 запрета на входы контрольных делителей 9 и 10 частоты и схем 3 и 4 контроля Выходы делителей 1 и 2 частоты соединены соответственно с входами выходных схем 11 и 12, схем 3 и 4 кони 8 э

троля и входами элементов

прет.а своего канала деления и с. входами элементов 5 и б памяти другого канала деления. Выхо.цы контрольных делителей 9 и 10 соединены соответственно со зхс.цами выходных схем 11 и 12 и элементов 13 и 14 задержки, выходы схем 11 и 12 соединены со входами элеь.ексов 5 и б памяти ка кдого канала через элементы 13 и 14 задержки. Выходы элементов 5 и б памяти соединены соответственно со вход;ами делителей 1 и 2 частоты и элемеТ Чон 3 и 4 контроля,

Резервированный делитель частоты работает следующим образом.

Поскольку оба канала работают аналогично, рассмотрим работу одного какала. Входная последователькрсть импульсов поступает па вход делителя 1.частоты и через элемент 7 запрата на вход контрольного делителя 9„ Км Пульс с выхода делителя 1 частоть7 поступает на вход выходной схемы 11 и вход элемента 7 запрета. На другие ВХОДЫ выходной схемы 11 поступают с разрядов контрольного дзлителя 9, Если на момент прихода импульса с выхода делителя 1 частоты выходная cxBiMa i 1 фиксирует требуемое, состояние контрольного делителя 9 частоты, равное остатку от деления основного дапителя на коэффициент .деления контро1;ьного делителя,.то на выходе выходной cxsMta 11 вырабатываются сигналы, подтверух:даювдие состояние элемента 5 памяти.

соответствую11№ е исправной работе данного канала деления. Элемент 7 запрета при поступлении импульса с выхода делителя 1 частоты запрещает поступление импульсов входного сигнала на вход контрольного делителя 9 частоты. Число запрещенных импульсов соответствует состоянию контрольного делителя 9, фиксируемому при исправной работе. Запрет такого числа импульсов эквивалентен установке контрольного делителя 9 частоты в исходное состояние. Следующий цикл деления протекает аналогично. Если на момент прихода импульса с выхода делителя 1 частоты на вход схемы 11 фиксируется состояние контрольного делителя 9, отличное от требуемого, то на выходе выходной схемы 11 появляются сигналы, устанавливающие элемент 5 памяти в состояние, соответствующее неисправной работе данного канала. При этом сигнал с выхода элемента 5 памяти устанавливает делитель 1 частоты и контрольный делитель 9 частоты в исходное состояние и .держит их в этом состоянии (делители останавливаются). Если второй канал исправен,.то сигнал с выхода делителя 2 частоты устанавливает элемент 5 памяти в состояние, соответств оощее исправному состоянию своего канала, сигнал на выходе элемента 5 исчезает и первый канал деления начинает работг1ть синфазко со вторыг. При сбое второго канала процесс Koppeicirv-iH протекает аналогично.

П р и м е р. Пусть коэффициенты деления основного и контрольного делителей 1 и 5 частоты равны, соответственно, 1000000 и 13, В этом случае состояние, фиксируемое в контрольном делителе 9 частоты, равно . Оно вычисляется как остаток от деления коэффициента деления основного делителя 1 частоты на коэффициент деления контрольного делителя 9 частоты. Следовательно схема 7 запрета должна осуществлять запрет орпого иь;пул)Са при подаче сигнала с выхода .де.лите.;1Я 1 частоты 7„ В этом случае с.хема запрета реализуется с ;-;спользояанием одного О К-триггера. На вход ti-триг гера подается биг- нал с выхода оснозного делителя, на вход К - .входной сигнал. С инверсного выхода триггера снимается сигнал запрета, который поступает на входы - и К первого триггера контрольного делителя. Такая схема обеспечивает заир.эт одного импульса входного сигнала при появлении ..импульса на вхо.це осноЕНого делителЯе Введение схе0 мы-запрета позволяет исключить операцию сбр.оса контрольных делителей частоты в каждом .цикле деления, что позволяет повысить быстродействие устройства иИСКЛЮЧИТЬ схемы сброса 5 контрольных делителей. .

Авторы

Даты

1980-07-30—Публикация

1978-01-24—Подача