(54) РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования последовательности временных сигналов | 1975 |

|

SU525074A1 |

| Многоканальный формирователь временных меток | 1973 |

|

SU511686A1 |

| РЕЗЕРВИРОВАННЫЙ СЧЕТЧИК ДЛЯ ФОРМИРОВАНИЯ МЕТОК ВРЕМЕНИ | 2008 |

|

RU2379829C1 |

| Устройство для обмена информацией синхронных каналов | 1982 |

|

SU1072037A1 |

| Устройство для синхронизацииКАНАлОВ | 1979 |

|

SU842767A1 |

| Счетное резервированное устройство | 1986 |

|

SU1354413A1 |

| Автоматизированная радиолиния | 1987 |

|

SU1443189A1 |

| Резервированный счетчик импульсов | 1986 |

|

SU1370778A1 |

| Устройство контролируемого пункта | 1983 |

|

SU1211784A1 |

| Устройство для контроля мажоритарных схем | 1983 |

|

SU1117643A1 |

1

Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке надежных распределителей импульсов с наперед задан; ной программой, а также программно-временных устройств. .

Известно устройство для распределения импульсов, содержащее счетчик, шаговый распределитель, генератор записи уставки, датчик уставки, причем выход задающего генератора соединен со входом счетчика, выход которого подключен ко входу щагового распределителя и первому входу генератора записи уставки, выходы шагового распределителя соединены со входами датчика уставки, выход которого подключен ко второму входу генератора записи уставки, выход которого подключен ко второму входу счетчика и входу датчика уставки 1.

Недостатками этого устройства являются малое быстродействие, обусловленное последовательной записью в счетчик числа, соответствующего разности между полной емкостью счетчика и отсчитываемым интервалом времени, а также ограниченные функциональные возможности, заключающиеся

в том, что выходной сигнал может присутствовать последовательно только на одном выходе.

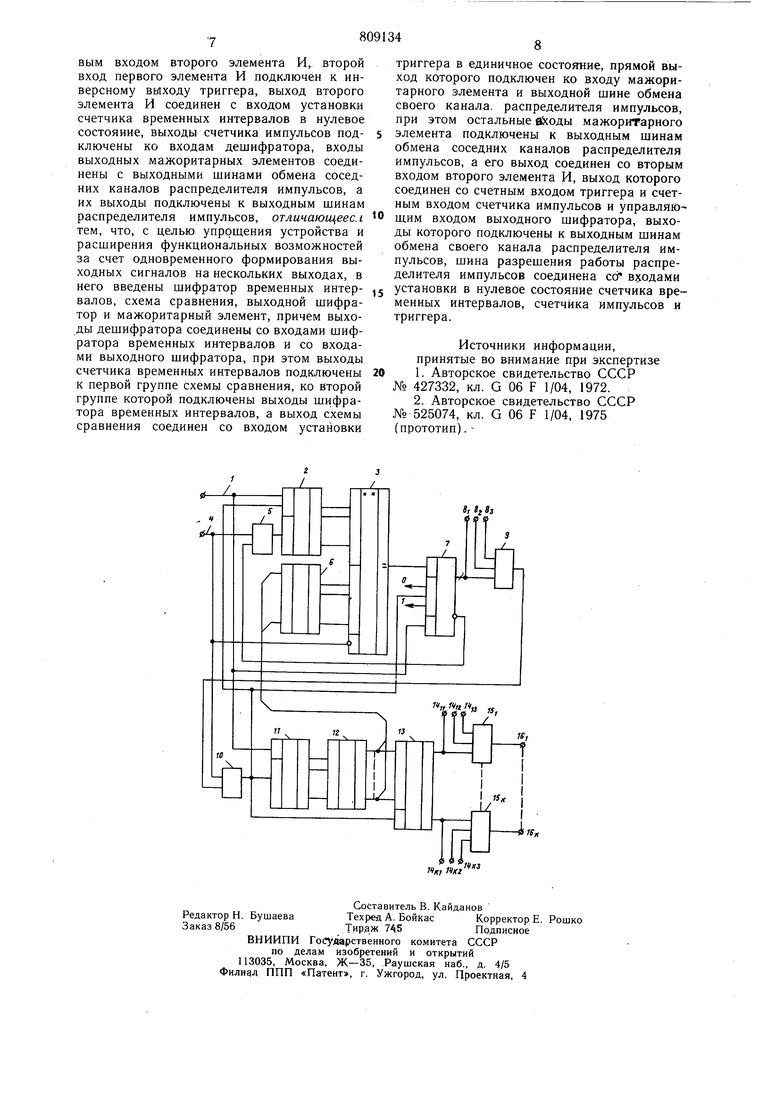

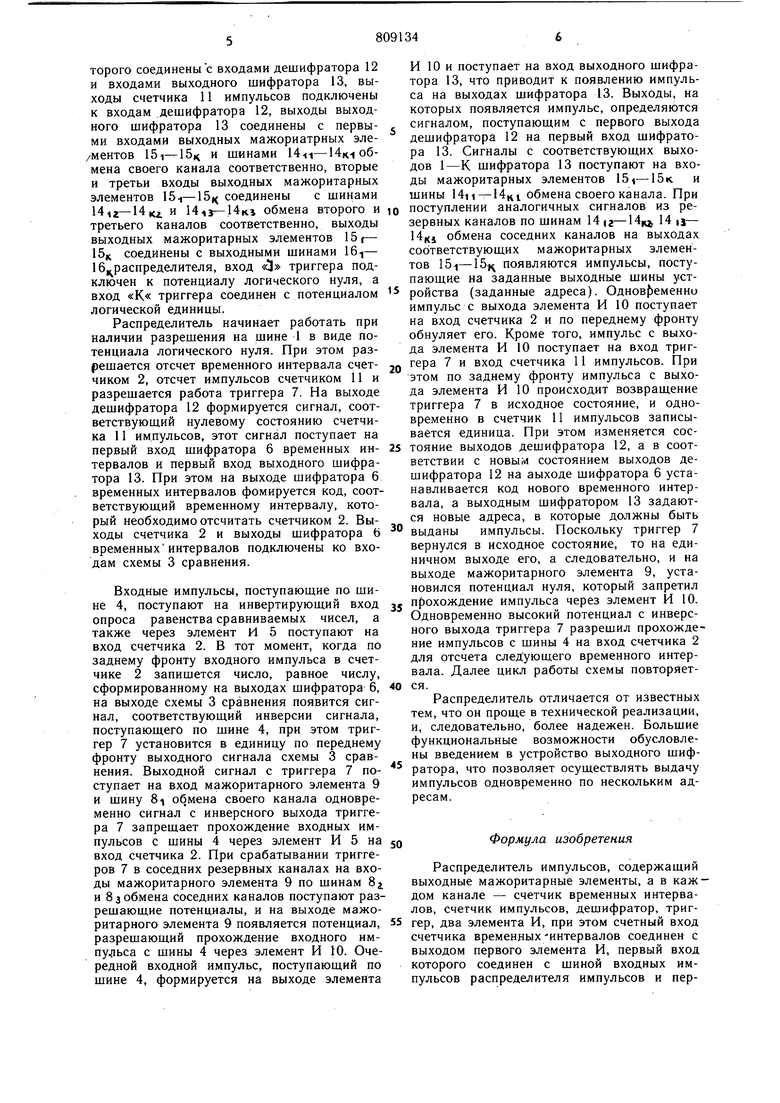

Известен распределитель импульсов, содержащий в каждом канале счетчик времени, дещифратор, счетчик вре.менных меток, дешифратор временных меток, триггер, три элемента И, два элемента ИЛИ, элемент НЕ, триггер формирования временной метки, мажоритарные элементы, причем первый вход счетчика времени соединен с выходом первого элемента И и первым входом триггера, первый вход первого элемента И объдинен со входом инвертора, первым входом второго элемента И и шиной входных импульсов, а второй вход первого элемента И соединен с инверсным выходом триггера формирования временной метки, при этом выход второго элемента И соединен со вторым входом триггера и входом установки в ноль счетчика времени, а выходы счетчика времени подключены к первым входам дешифратора, вторые входы дешифратора соединены с выходами счетчика временных меток и входами дешифра- ора временных меток, а еще один вход дешифратора объединен с выходом инвертора и входом третьего элемента И, второй вход которого соединен с выходом триггера, инверсный выход которого соединен со входом дешифратора временных меток, при этом выход третьего элемента И подключен ко входу счетчика временных меток и входу установки в нуль триггера формирования временной метки, прямой выход которого соединен со входом дешифратора временных меток, а вход установки в единицу триггера формирования временной метки подключен к выходу первого элемента ИЛИ, входы которого соединены с входами дешифратора, причем выходы дешифратора временных меток соединены с первыми входами мажоритарных элементов и шинами обмена своего канала, остальные входы мажоритарных элементов соединены с шинами обмена соседних каналов, а выходы мажоритарных элементов подключены к выходным шинами устройства и ко входам второго элемента ИЛИ, выход которого соединен со вторым входом второго элемента И 1. Недостатком этого распределителя импульсов являются его большая сложность и, следовательно, низкая надежность, а также ограниченные функциональные возможности, заключающиеся в том, что формируется выходной сигнал только на одном выходе и не допускает одновременного формирования выходных сигналов на нескольких выходах распределителя. Цель изобретения - упрощение и расширение функциональных возможностей распределителя за счет возможности одновременного формирования выходных сигналов на нескольких выходах. Поставленная цель достигается тем, что в распределитель импульсов, содержащий выходные мажоритарные элементы, в каждом канале - счетчик временных интервалов, счетчик импульсов, дешифратор, триггер, два элемента И, при этом счетный вход счетчика временных интервалов соединен с выходом первого элемента И, первый вход которого соединен с шиной входных импульсов распреде.лителя импульсов и первым вхо дом второго элемента И, второй вход первого элемента И подключен к инверсному- вы ходу триггера, выход второго элемента И соединен с входом установки счетчика временных интервалов в нулевое состояние, вь1ходы счетчика импульсов подключены ко , входам дешифратора, входы выходных мажоритарных элементов соединены с выходными шинами обмена соседних каналов распределителя импульсов, а их выходы подключены к выходным шинам распределителя импульсов, введены шифратор временных интервалов, схема сравнения, выходной шифратор и мажоритарный элемент, причем выходы дешифратора соединены со входами шифратора временных интервалов и со входами выходного шифратора, при этом выходы счётчика временных интервалов подключены к первой группе схемы сравнения, ко второй группе которой подключены выходы шифратора временных интервалов, а выход схемы сравнения соединен со входом установки триггера в единичное состояние, прямой выход которого подключен ко входу мажоритарного элемента и выходной шине обмена своего канала распределителя импульсов, при этом остальные входы мажоритарного элемента подключены к выходным шинам обмена соседних каналов распределителя импульсов, а его выход соединен со вторым входом второго элемента И, выход которого соединен со счетным входом триггера и счетным входом счетчика импульсов и управляюш,им входом выходного шифратора, выходы которого подключены к выходным шинам обмена своеГО канала распределителя импульсов шина разрешения работы распределителя импульсов соединена со входами установки в нулевое состояние счетчика временных интервалов, счетчика импульсов и триггера. На чертеже представлена функциональная схема одного канала распределителя. Распределитель содержит шину 1 разрешения работы устройства, счетчик 2 временных интервалов, схему 3 сравнения, шину 4 входных импульсов, элемент И 5, шифратор 6 временных интервалов, триггер 7, шину 8 обмена своего канала, шины 8г и 8 3 обмена соседних каналов, мажоритарный элемент 9, элемент И 10, счетчик 11 импульсов, дешифратор 12, выходной шифратор 13, выходные шины выходного шифратора - шины 14(1-14(11 обмена своего канала, шины 14-12- Ki 14ii-14кз обмена соседних каналов, мажоритарные элементы 15t-15ц, выходные шины распредителя. Шина 1 разрешения работы распределителя соединена с первым входом счетчика 2 временных интервалов и со входами триггера 7 и счетчика 11 импульсов, шина 4 входных импульсов соединена с первыми входами элементов И 5 и 10, инвертирующим входом схемы 3 сравнения, второй вход элемента И 5 подключен к инверсному входу триггера 7, прямой выход которого соёдинен с первым входом мажоритарного элемента 9 и шиной 8 обмена своего канала, а второй и третий входы мажоритарного элемента 9 соединены соответственно с шинами 8г и 8 3 обмена соседних каналов, выход мажоритарного элемента 9 соединен со вторым входом элемента И 10, выход которого подключен ко второму входу счетчика 2 временных интервалов и к входам триггера 7, счетчика 11 импульсов, выходного шифратора 13, выход элемента И 5 соединен со входом счетчика 2 временных интервалов, выходы которого подключены к первым входам схемы 3 сравнения, вторые входы схемы 3 сравнения соединены с выходами шифратора 6 временных интервалов, входы которого соединеныс входами дешифратора 12 и входами выходного шифратора 13, выходы счетчика 11 импульсов подключены к входам дешифратора 12, выходы выходного шифратора 13 соединены с первыми входами выходных мажориатрных эле/ментов 15i-15ц и шинами обмена своего канала соответственно, вторые и третьи входы выходных мажоритарных элементов 15-1-15 соединены с шинами 14 2-14ict и 14 3-14к1 обмена второго и третьего каналов соответственно, выходы выходных мажоритарных элементов 15 - 15к соединены с выходными шинами 1б распределителя, вход «3 триггера подключен к потенциалу логического нуля, а вход «К« триггера соединен с потенциалом логической единицы. Распределитель начинает работать при наличии разрешения на шине 1 в виде потенциала логического нуля. При этом разрешается отсчет временного интервала счетчиком 2, отсчет импульсов счетчиком 11 и разрешается работа триггера 7. На выходе дешифратора 12 формируется сигнал, соответствующий нулевому состоянию счетчика 11 импульсов, этот сигнал поступает на первый вход шифратора 6 временных интервалов и первый вход выходного шифратора 13. При этом на выходе шифратора б временных интервалов фомируется код, соответствующий временному интервалу, который необходимо отсчитать счетчиком 2. Выходы счетчика 2 и выходы шифратора Ь временныхинтервалов подключены ко входам схемы 3 сравнения. Входные импульсы, поступающие по шине 4, поступают на инвертирующий вход опроса равенства сравниваемых чисел, а также через элемент И 5 поступают на вход счетчика 2. В тот момент, когда по заднему фронту входного импульса в счетчике 2 запишется число, равное числу, сформированному на выходах шифратора 6, на выходе схемы 3 сравнения появится сигнал, соответствующий инверсии сигнала, поступающего по шине 4, при этом триггер 7 установится в единицу по переднему фронту выходного сигнала схемы 3 сравнения. Выходной сигнал с триггера 7 поступает на вход мажоритарного элемента 9 и шину 8 ( обмена своего канала одновременно сигнал с инверсного выхода триггера 7 запрешает прохождение входных импульсов с шины 4 через элемент И 5 на вход счетчика 2. При срабатывании триггеров 7 в соседних резервных каналах на входы мажоритарного элемента 9 по шинам 8 и 8зобмена соседних каналов поступают разрешающие потенциалы, и на выходе мажоритарного элемента 9 появляется потенциал, разрешающий прохождение входного импульса с шины 4 через элемент И 10. Очередной входной импульс, поступающий по шине 4, формируется на выходе элемента И 10 и поступает на вход выходного шифратора 13, что приводит к появлению импульса на выходах шифратора 13. Выходы, на которых появляется импульс, определяются сигналом, поступающим с первого выхода дешифратора 12 на первый вход шифратора 13. Сигналы с соответствующих выходов 1-К шифратора 13 поступают на входы мажоритарных элементов и шины 14ii -14щ обмена своего канала. При поступлении аналогичных сигналов из резервных каналов по шинам 14 ij-14nj 14 ij- HKJ обмена соседних каналов на выходах соответствуюших мажоритарных элементов 15i-15д появляются импульсы, поступающие на заданные выходные шины устройства (заданные адреса). Однов{)еменно импульс с выхода элемента И 10 поступает на вход счетчика 2 и по переднему фронту обнуляет его. Кроме того, импульс с выхода элемента И 10 поступает на вход триггера 7 и вход счетчика 11 импульсов. При этом по заднему фронту импульса с выхода элемента И 10 происходит возвращение триггера 7 в исходное состояние, и одновременно в счетчик 11 импульсов записывается единица. При этом изменяется состояние выходов дешифратора 12, а в соответствии с новым состоянием выходов дешифратора 12 на аыходе шифратора 6 устанавливается код нового временного интервала, а выходным шифратором 13 задаются новые адреса, в которые должны быть выданы импульсы. Поскольку триггер 7 вернулся в исходное состояние, то на единичном выходе его, а следовательно, и на выходе мажоритарного элемента 9, установился потенциал нуля, который запретил прохождение импульса через элемент И 10, Одновременно высокий потенциал с инверсного выхода триггера 7 разрешил прохождение импульсов с шины 4 на вход счетчика 2 для отсчета следующего временного интервала. Далее цикл работы схемы повторяетРаспределитель отличается от известных тем, что он проще в технической реализации, и, следовательно, более надежен. Большие функциональные возможности обусловлены введением в устройство выходного шифратора, что позволяет осуществлять выдачу импульсов одновременно по нескольким адресам. Формула изобретения Распределитель импульсов, содержащий выходные мажоритарные элементы, а в каждом канале - счетчик временных интервалов, счетчик импульсов, дешифратор, триггер, два элемента И, при этом счетный вход счетчика временныхинтервалов соединен с выходом первого элемента И, первый вход которого соединен с шиной входных импульсов распределителя импульсов и пер

Авторы

Даты

1981-02-28—Публикация

1979-01-08—Подача