тета, элемент сравнения, генератор тактовых импульсов, формирователь тактовых импульсов, счетчик номера команд, шифратор, элемент ИДИ, эле- мент И, элемент задержки и триггер, выход генератора тактовых импульсов соединен с первым входом формирователя тактовых импульсов, второй вход которого является входом блока, выход формирователя тактовых импульсов соединен с нулевым установочным входом триггера и с первым входом регистра управляющих сигналов, управляющие вход и выход формирователя тактовых импульсов соединены соответственно с первым входом и выходом дешифратора команд, вторые вход и выход которого соединены соответственно с входом и выходом регистра команд, третий и четвертый входы депмф ратора команд соединены соответственно с прямым выходом триггера и с выходом элемента сравнения, третий и четвертый выходы дешифратора коман соединены соответственно с входами элемента суммирования и вычитания и первого элемента согласования, пятый выход дешифратора команд соединен с первыми входами второго элемента согласования, регистра адреса, блока регистров и счетчика номера команд, второй вход которого является входом блока, объединенные вход и выход счетчика номера команд соединены с объединенными входом и выходом блока регистров, выход счетчика номера ксжанд соединен с вторым входом регистра адреса, выход которого соединен с вторым входом второго элемента согласования и с входом селектора адреса , выход которого соединен с первым входом элемента И, второй вход которого является объединенным управляющим входом-выходом блока, выход первого элемента И соединен с первым входом регистра приоритета, второй вход которого соединен с объединенньии входами и выходами элемента суммирования и вычитания, блока регистров и первого элемента согласования, с входами регистра команд, с входами регистра управлякнцих сигналов и с первым выходо шифратора, первый вход которого объединен с первым входом элемента ИЛИ и соединен с первым выходом регистра управляющих сигналов, второй выход которого соединен с первым

входом дешифратора управляющих сиг- налов, выходы которого являются вто рьм объединенным входов-выходом блока, второй вход дешифратора управляющих сигналов через элемент задержки подключен к инверсному выходу триггера, единичный установочный вход которого соединен с выходом элемента ИЛИ, второй вход которого и входы регистра запроса являются объединенным управлянлцим входом-выходом блока, третий вход элемента ИЛИ соединен с выходом элемента И, выход регистра запроса соединен с входом селектора приоритета, выход которого соединен с вторым входом шифратора, второй выход которого соединен с первым входом элемента сравнения, второй вход которого соединен с выходом регистра приоритета, объединенный выход второго элемента согласования является объединенным выходом блока, объединенньй вход-выход первого элемента согласования является первым объединенным входом-выходом данных блока.

3. Устройство по п. 1, о т л и- чающееся тем, что блок обмена данными содержит программируемый коммутатор, элемент памяти данных, формирователь сигналов запроса, элемент ввода-вывода данных и элемент памяти команд, адресный вход, вход-вьисод данных и управляющие вход-выход элемента памяти данных являются соответствующими

объединенными входом и объединенными входами-выходами блока, линейный вход и вьгход которого являются соответственно первыми входом и выходом элемента ввода-вывода данных, первый вход блока является установочным входом программируемого коммутатора, первый вход-выход которого соединен с выходом элемента памяти команд, с вторым входом-выходо элемента ввода-вывода данных и с певым входом-выходом элемента памяти данных, второй вход-выход программируемого коммутатора соединен с входом-выходом элемента памяти команд, с третьим входом-выходом элемента ввода-вывода данных, с первым выходом формирователя сигналов запроса и с вторым входом-выходом элемента памяти данных, первый выход программируемого коммутатора соединен с

первыми входами элемента памяти ко- манд, элемента ввода-вывода данных и элемента памяти данных, второй выход программируемого коммутатора соединен с .вторыми входами элемента памяти данных и элемента ввода- вывода данных, третий, четвертый и пятый выходы программируемого коммутатора соединены соответственно с третьим входом элемента памяти данных, с вторым.входом элемента памяти команд и с третьим входом элемента ввода-вывода данных, первый, второй, третий, четвертьй и пятый выходы элемента памяти данных соединены с соответствующими входами формирователя сигналов запроса, второй выход которого является управляющим входом-выходом блока.

4. Устройство по п. 1, отличающееся тем, что второй блок памяти содержит элемент памяти, элементы согласования, селектор адреса, регистр адреса, элемент ИЛИ, элементы И, формирователи сигналов, элементы задержки, резервный источник питания, диод, конденсатор и резистор, входы питания элемента памяти, регистра адреса, элементов И, формирователей сигналов и первого элемента задержки через включенный в обратном направлении диод соединены с шиной основного питания и через резистор - с резервным источником питания, катод диода и первый вывод резистора соединены с первым выводом конденсатора, второй вывод которого .соединен с шиной нулевого потенциа- ;ла, вход первого элемента согласования является объединенным входом блока, выход первого элемента согласования соединен с входом селектора адреса и с первым входом регистра адреса, выход которого соединен с адресным входом элемента памяти, выход селектора адреса соединен с первыми входами элементов И и второго элемента согласования, второй и третий входы которого, второй вход второго элемента И, входы элемента ИЛИ и выход первого элемента задержки являются первым объединенным входом-выходом блока, первый вход- выход второго элемента согласования является вторым объединенным входом- выходом блока, второй вход-выход второго элемента согласования соединен с входом-выходом данных элемента памяти, вход режима работы которого соединен с выходом второго элемента И, управляющий вход элемента памяти соединен с выходом второго формирователя сигналов, вход которого через второй элемент задержки и второй вход регистра адреса подключе к выходу первого формирователя сигналов , вход которого и вход первого элемента задержки соединены с выходом первого элемента И, второй вход .первого элемента И соединен с выходо элемента ИЛИ, третьи входы элементов И являются входом блока.

5. Устройство по п. 1, о т л и- чающееся тем, цто таймер содержит селектор адреса, дешифратор, элементы согласования, регистр счетчики, триггер, элементы И, элементы ИЛИ, элементы задержки, гене ратор тактовых импульсов, резервный источник питания, диод, конденсатор и резистор, входы питания генератора тактовых импульсов и первого счетчика через включенный в обратном направлении диод соединены с шиной основного питания и через резистор - с источником резервного питания, катод диода и первый вывод резистора соединены с первым выводом конденсатора, второй выход которого соединен с шиной нулевого потенциала, адресные входы дешифратора и селектора адреса являются объединенным входом таймера, выход селектора адреса соединен с первыми входами элементов И и первым входом первого элемента согласования, вторые входы первого и второго элементов И соединены с первым выходом дешифратора, второй и третий выходы которого соединены с вторыми входами соответственно третьего и четвертого элементов И, третьи входы первого, третьего и четвертого элементов И и второй вход первого элемента согласования являются первым объединенным входом-выходом таймера, третий вход второго элемента И и третий вход первого элемента согласования являются первым объединенным входом-выходом таймера, выход первого элемента И соединен с первыми входами первого элемента ШШ и первого счетчика, второй вход которого соединен с выходом генератора тактовых импульсов и с первым входом второго счетчика, второй вход которого сое121

динен с выходом регистра, первый вход которого, третий вход первого счетчика и первый вход-выход первого элемента согласования соединены с выходом второго элемента согласования, второй вход-выход первого элемента согласования является вторым объединенным входом-выходом таймера, выход первого элемента ИЛИ соединен с входом первого элемента задержки, выход которого является первым объединенным входом-выходом таймера, выход третьего элемента И соединен с вторыми входами элементов ИЛИ и регистра, выход четвертого элемента И соединен с третьим входом первого элемента ИЛИ и с нулевым установочным входом триггера, выход второго элемента И соединен с четвертым входом первого элемента ИЛИ и с первым входом второго элемента согласования, второй вход ко- Ьорого соединен с выходом первого счетчика, выход второго счетчика соединен с единичным установочным входом триггера и через второй элемент эадержки - с первым входом второго элемента ИЛИ, выход которого соединен с третьим входом второго счетчика, выход триггера является первым объединенным входом-выходом таймера

6. Устройство по п. 1, о т л и- ч ающ.е ее я тем, что шифратор признака запуска содержит селектор адреса, элементы И и элемент задержки, вход селектора адреса является адресным входом шифратора, выход селектора адреса соединен с первым входом первого элемента И, второй вход которого и выход элемента задержки являются объединенным входомИзобретение относится к телемеханике и может быть использовано в автоматизированных системах управления рассредоточенными объектами,, например в нефтедобывающей промьшшенности.

Целью изобретения является расширение функциональных возможностей устройства путем осуществления гиб- сой программы опроса.

784

выходом шифратора, выход первого элемента И соединен с выходом элемента задержки и с первым входом второго элемента И, второй вход и выход которого являются соответственно вторым входом и выходом данных .шифратора.

7.Устройство.по п. 1, о т л и- чающееся тем, что первый формирователь сигналов содержит делитель напряжения, триггер, элемент НЕ, элемент эадержки, обмотку реле и замыкающие контакты реле, подключенные к первому выводу делителя напряжения и первому выводу обмотки реле, соединенному с шиной основного питания, вторые выводы обмотки реле и делитель напряжения подключены к шине нулевого потенциала, выход делителя напряжения соединен с нулевым установочным входом триггера и с выходом элемента НЕ, выход которого через элемент задержки соединен с единичным установочным входом триггера, инверсный выход которого является выходом формирователя.

8.Устройство по п. 1, о т л и- . чающееся тем, что второй формирователь сигналов содержит компаратор, элемент НЕ, элемент И и элемент задержки, вход, компаратора соединен с шиной основного питания, вьссод компаратора - с первым входом элемента И и с входом элемента задержки, выход которого является первым выходом формирователя сигналов, вход элемента НЕ является входом формирователя сигналов, выход элемента НЕ соединен с вторым входом элемента И, выход которого является вторым выходом формирователя сигналов.

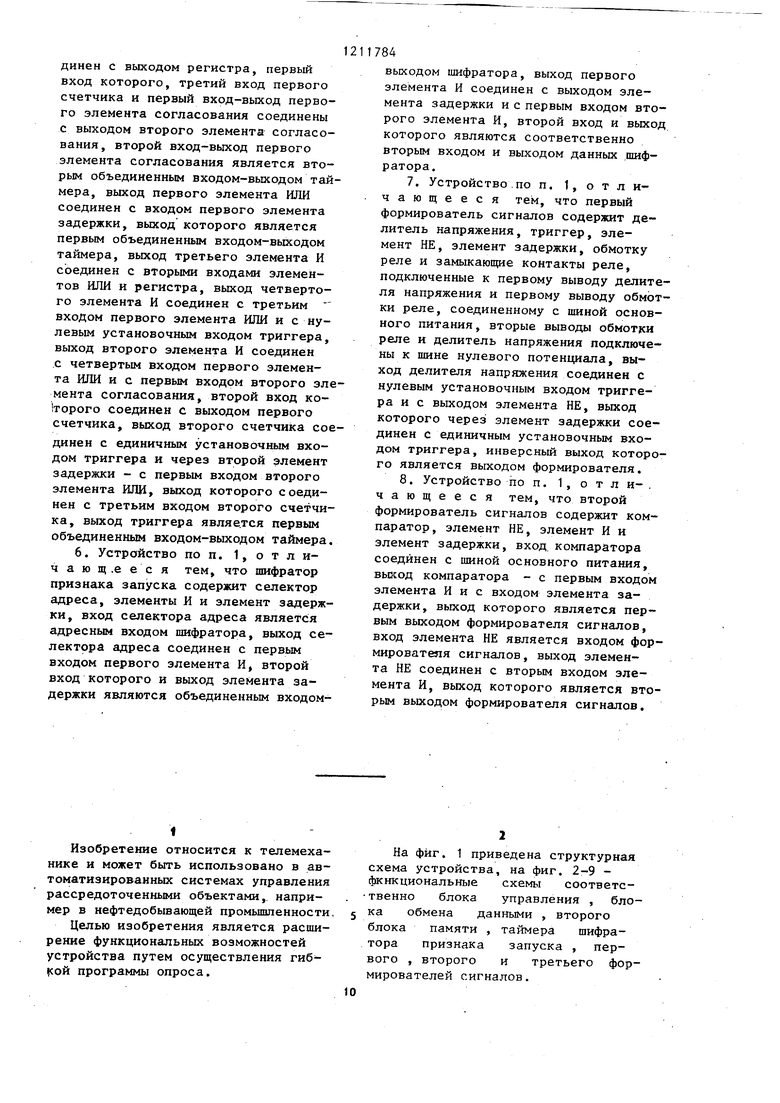

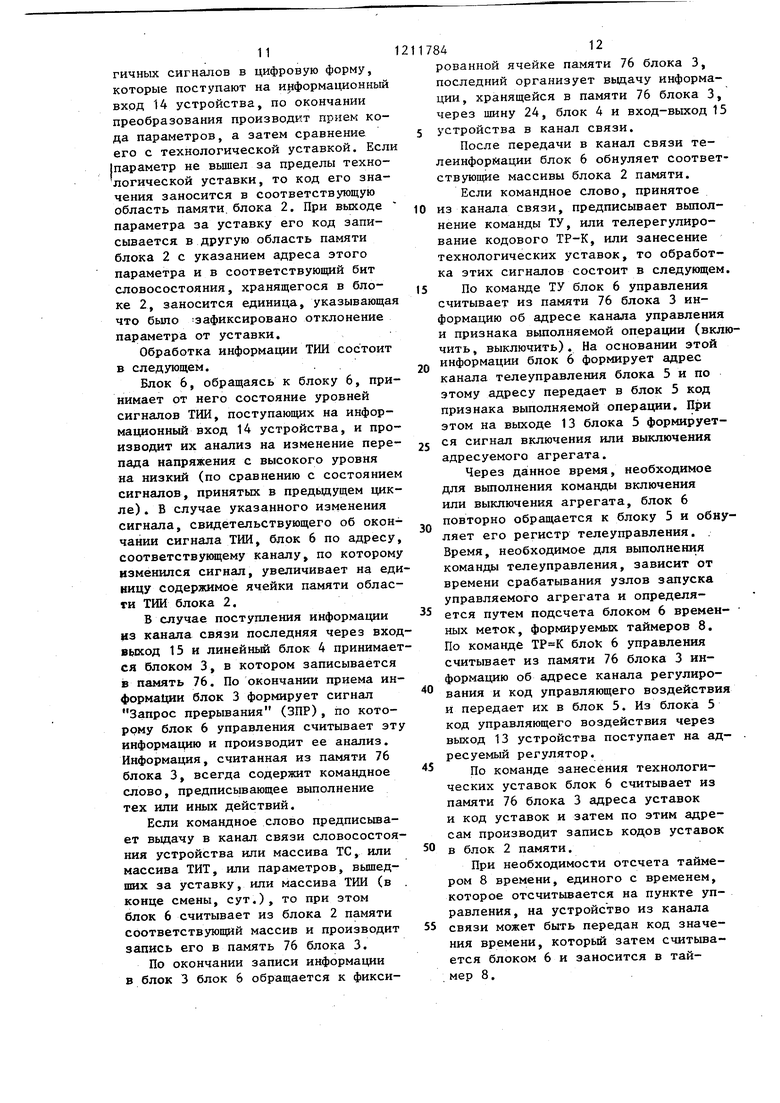

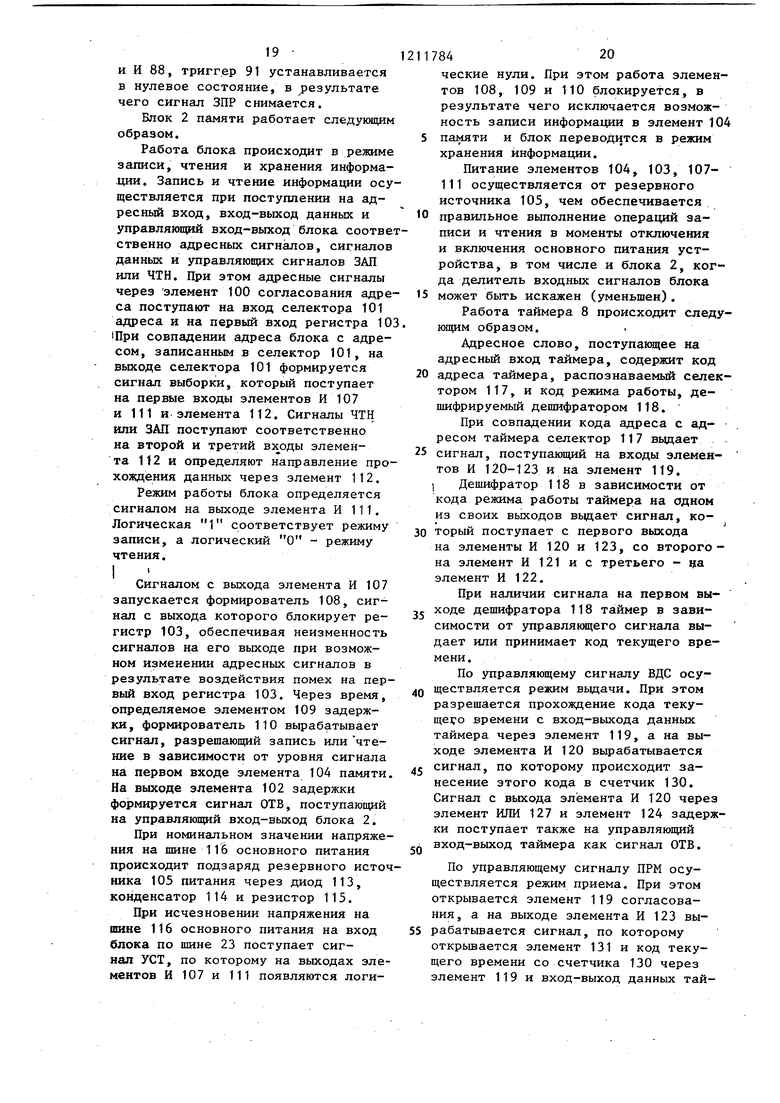

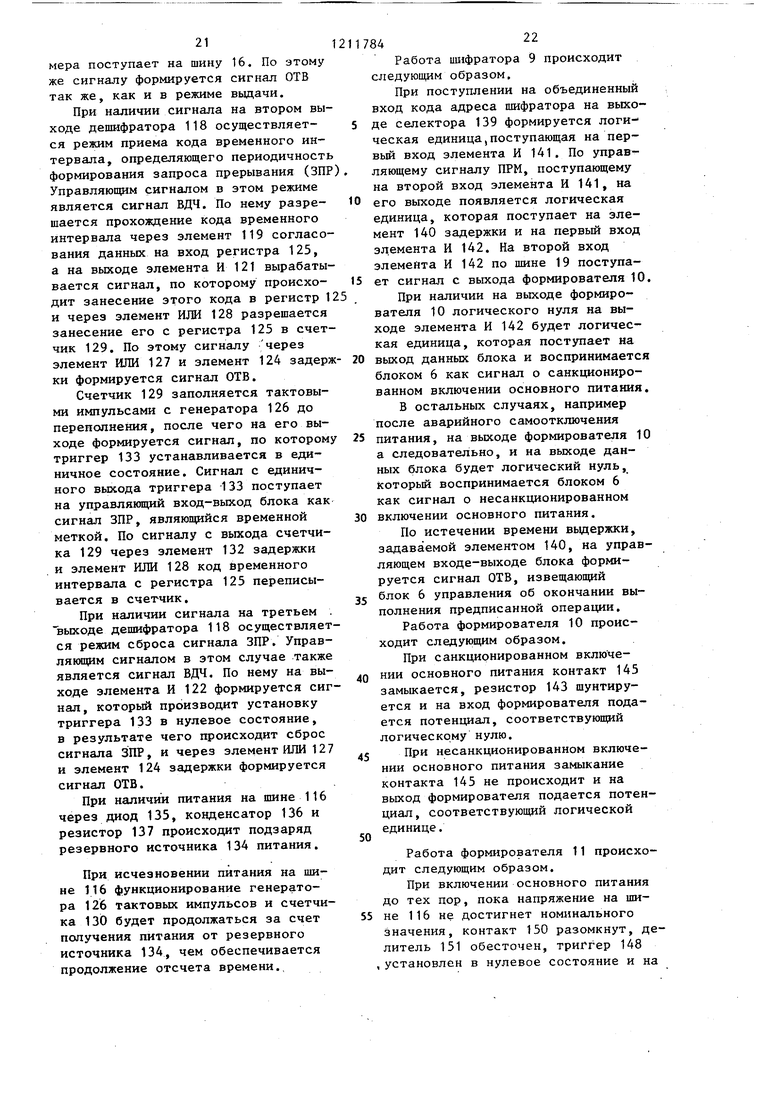

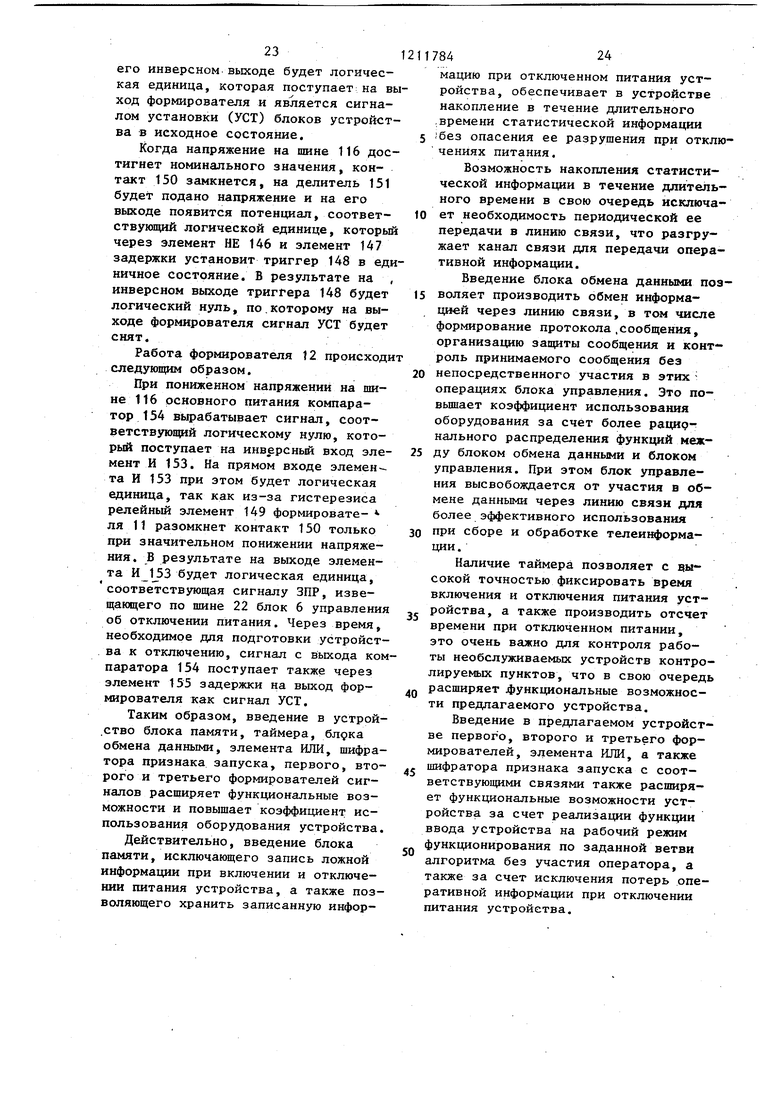

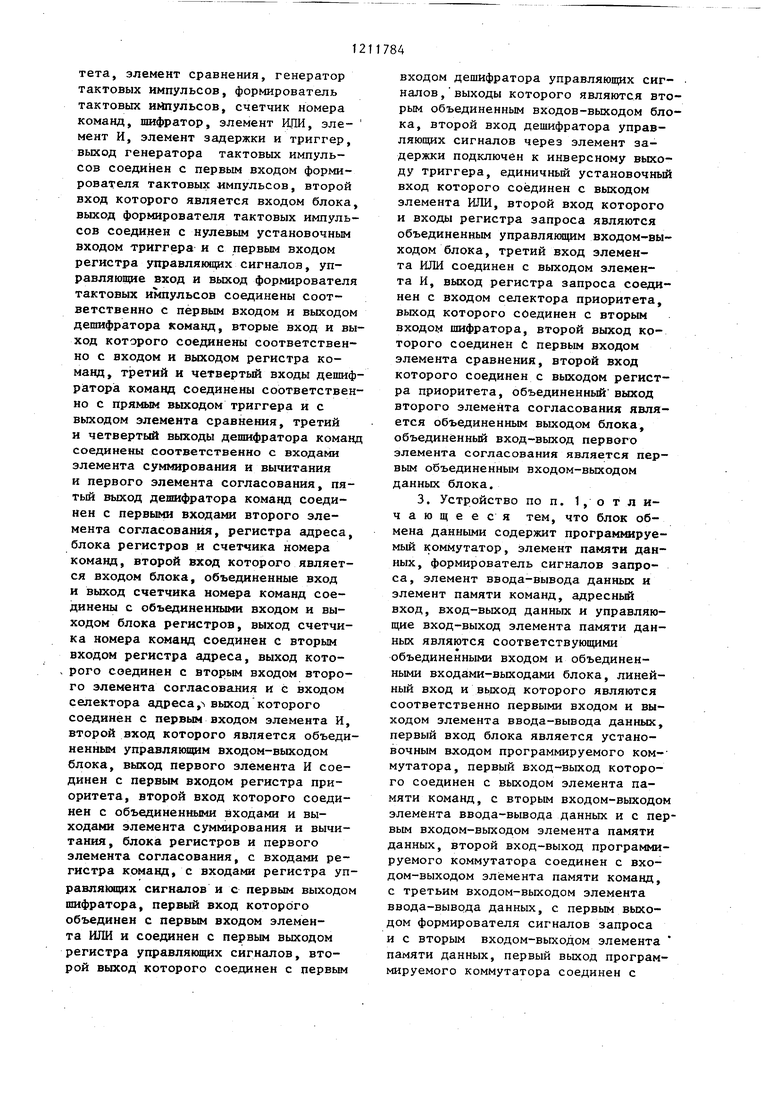

На фиг. 1 приведена структурная схема устройства, на фиг. 2-9 - фкнкциональные схемы соответс- твенно блока управления , блока обмена , второго блока памяти , таймера шифратора признака запуска , первого , второго и третьего формирователей сигналов.

Устройство контролируемого пункта (фиг. 1) содержит блоки 1 и 2 памяти, блок 3 обмена данными, линейный блок 4, блок 5 согласования, блок 6 управления, элемент ИЛИ 7, таймер 8, шифратор 9 признака запуска, формирователи 10-12 сигналов, управляющий выход 13, информационный вход 14, линейный вход-выход 15 шину 16 данных, шину 17 адреса, шину 18 управления, шины 19-24 межблочного соединения.

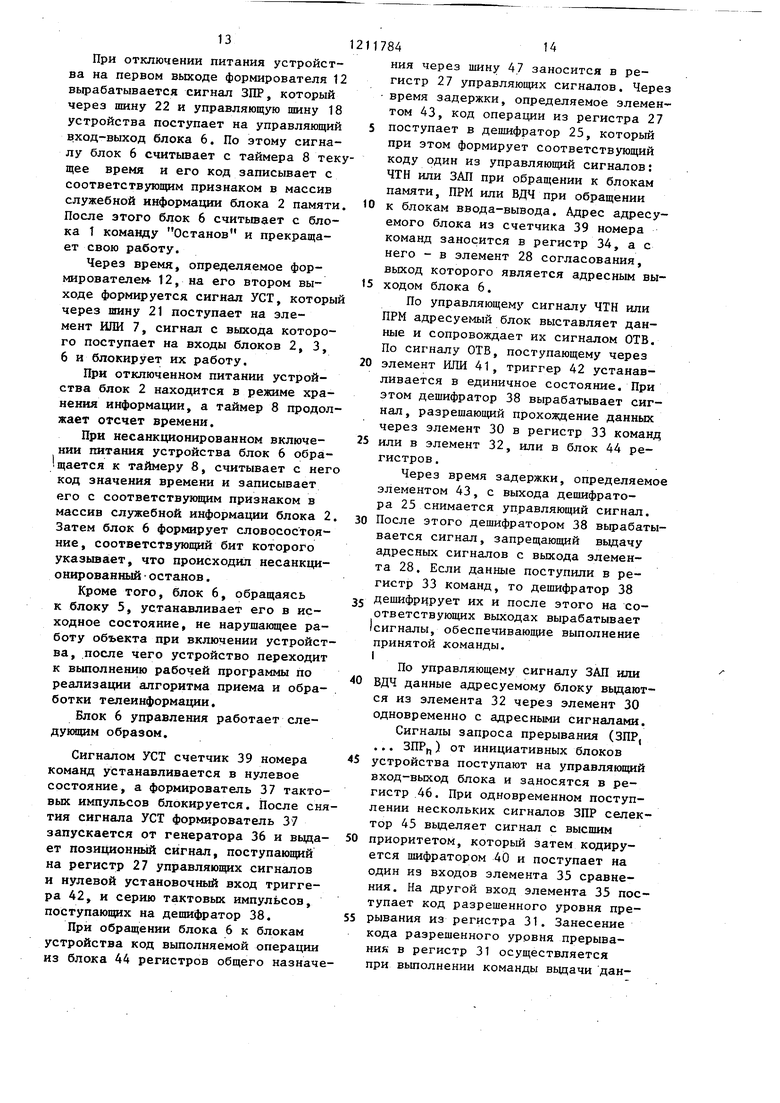

Блок 6 управления (фиг. 2) содержит дешифратор 25 управляющих сигна лов, элемент И 26, регистр 27 управ лякмцих сигналов, элемент 28 согласования, селектор 29 адреса, элемент 30 согласования, регистр 31 приоритета, элемент 32 суммирования и вычитания, регистр 33 команд, регистр 34 адреса, элемент 35 сравнения , генератор 36 тактовых импульсов, формирователь 37 тактовых импульсов, дешифратор 38 команд, счетчик 39 номера команд, шифратор 40, элемент ИЛИ 41, триггер 42, элемент 43 задержки, блок 44 регистров, селектор 45 приоритета, регистр 46 запроса и шину 47.

Блок 6 управления предназначен для реализации алгоритма функционирования устройства по программе, хранящейся в блоке памяти, в результате выполнения которой производится координация работы блоков устройства. Блок 6 выполняет определенный список команд, включакиций в себя команды чтения, записи при работе с блоками 1, 2 и 3, команды приема, выдачи при работе с блоками 5, IB и 9| логической и арифметической Iобработки данных, условных и безусловных ветвлений, а также организует предписанный порядок обработки запросов прерываний, поступающих от блоков устройства.

Генератор 36 совместно с формирователем 37 вырабатывают тактовые сигналы, синхронизирующие работу составных частей блока.

Счетчик 39 номера команд пред назначен для приема формирования и хранения адреса текущей команды.

Регистр 34 адреса осуществляет хранение адреса блока или ячейки памяти блока на время обмена данными с адресуемым блоком.

Элемент 30 согласования предназначен для развязки внутренней ши15

20

25

2117844

1ны 47, через которую осуществляется обмен данными между регистрами блока 6, шины 16 данных устройства, через которую происходит обмен дан- , ными между блоком 6 и другими блоками устройства.

Элемент 28 согласования осуществляет вЬщачу кода адреса из регистра 34 адреса при обращении блока 6 0 к другим блокам устройства.

Регистр 33 команд осуществляет прием кода команды, поступившего из первого блока 1 памяти, и хранение его в течение выполнения команды.

Дешифратор 38 команд расшифровывает код команды и формирует микрокоманды управления в соответствии с принятой командой. Элемент 32 суммирования и вычитания осуществляет обработку двоично-кодированной информации.

Блок 44 регистров общего назначения предназначен для приема, хранения и выдачи различной информации, )гчаствующей в процессе выполнения программы.

Регистр 31 служит для хранения кода разрешенного уровня приоритета запроса прерывания от блоков устрой ства.

Регистр 46 осуществляет прием и хранение запросов прерывания, поступивших от инициативных блоков устройства.

Селектор 45 приоритета предназначен для выделения сигнала запроса прерывания с высшим уровнем приоритета среди сигналов, поступивших на вход регистра 46.

Шифратор 40 преобразует позиционный сигнал запроса прерывания с высшим приоритетом в код запроса прерывания для выдачи на элемент 35 сравнения с кодом заданного уровня приоритета прерывания, хранящегося в регистре 31.

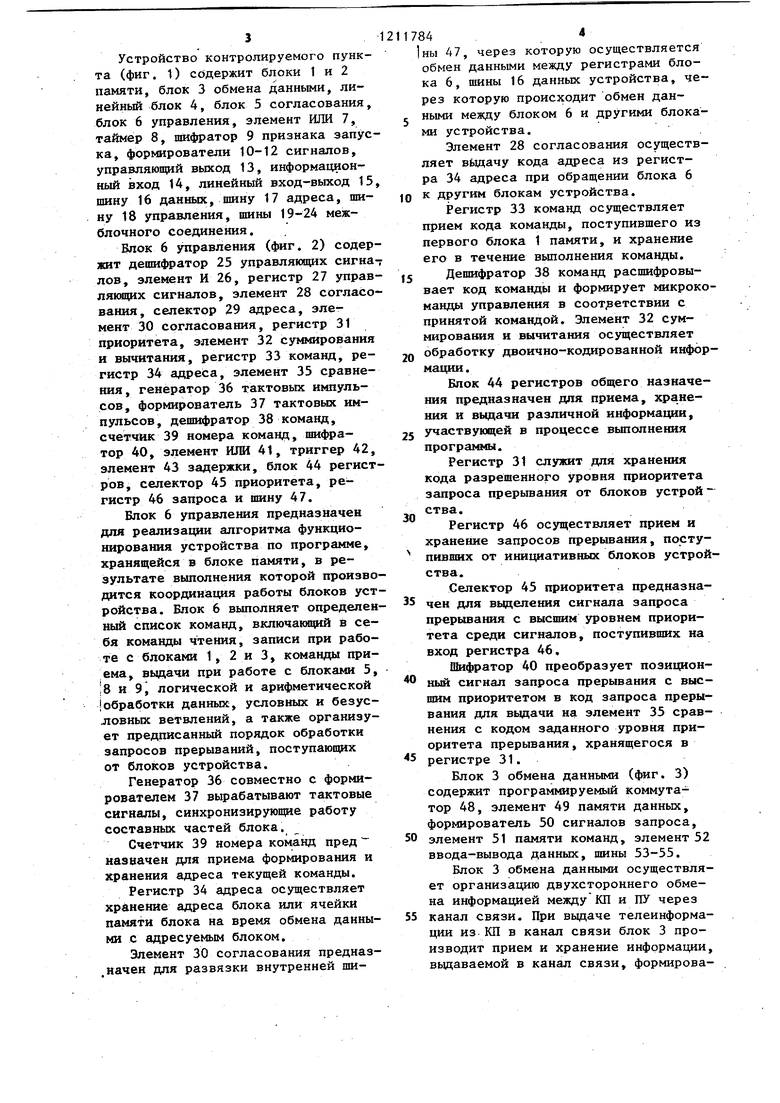

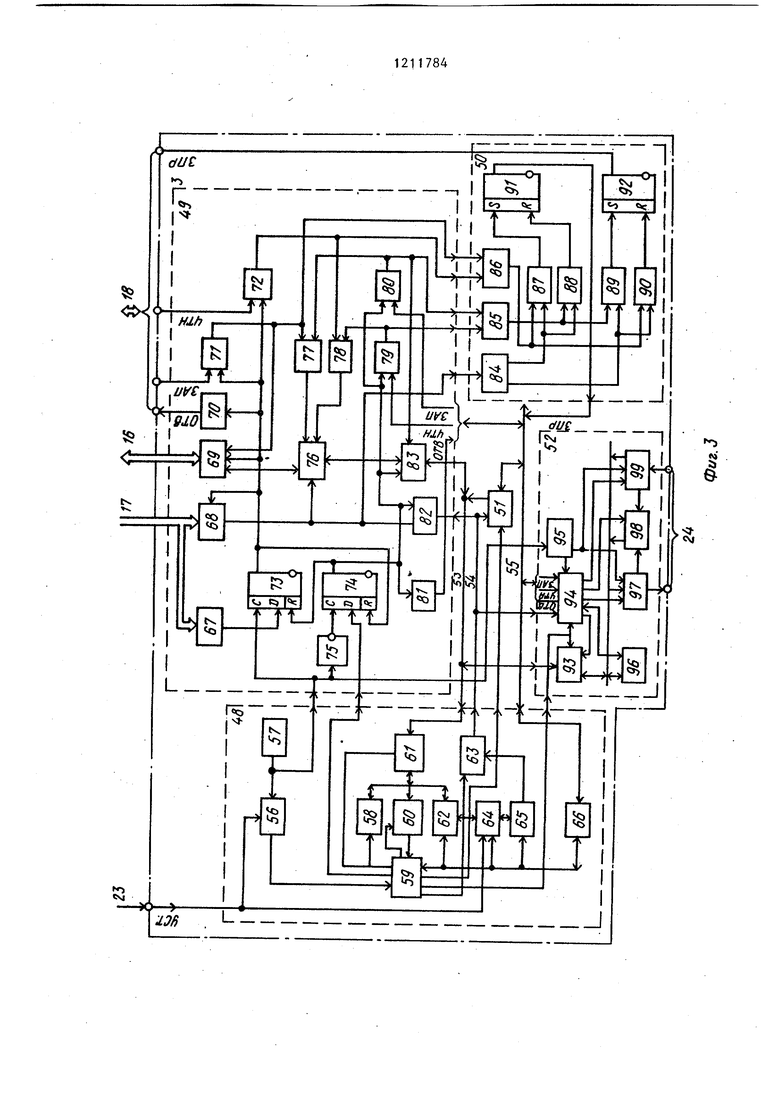

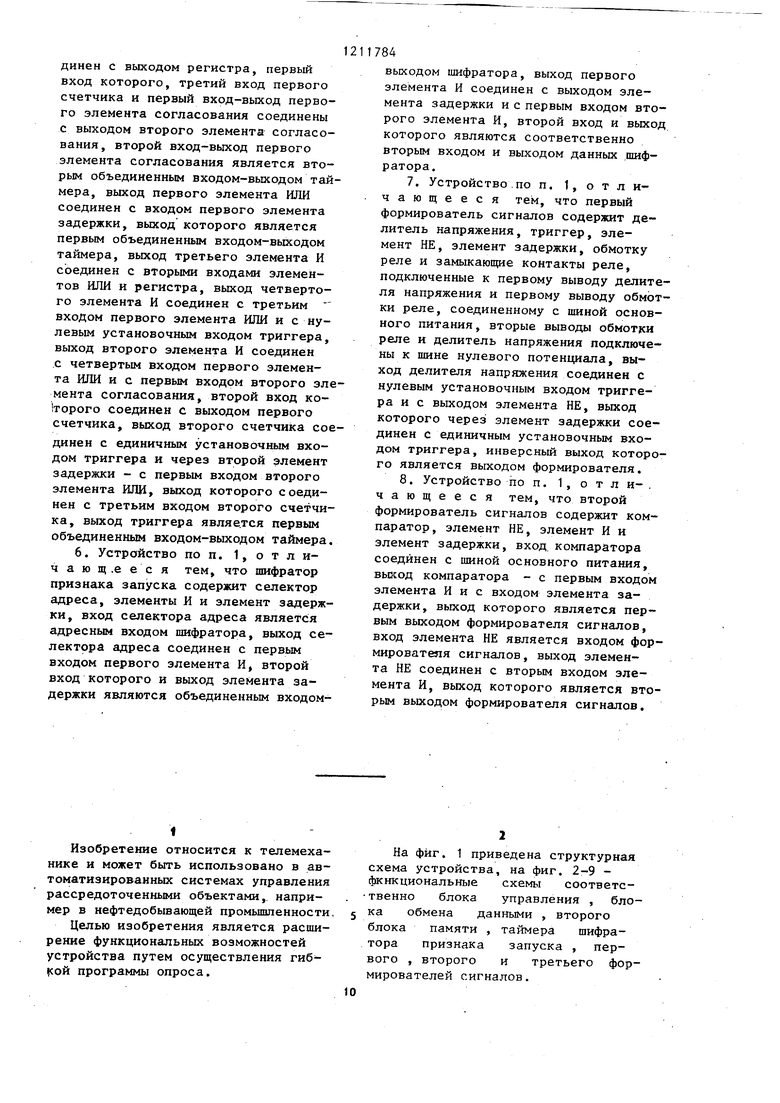

Блок 3 обмена данными (фиг. 3) содержит программируемый коммутатор 48, элемент 49 памяти данных, формирователь 50 сигналов запроса, элемент 51 памяти команд, элемент 52 ввода-вывода данных, шины 53-55.

Блок 3 обмена данными осуществляет организацию двухстороннего обмена информацией между КП и ПУ через 55 канал связи. При выдаче телеинформации из КП в канал связи блок 3 производит прием и хранение информации, выдаваемой в канал связи, формирова30

35

40

45

50

ние заданного протокола и формата сообщения. При приеме информации из канала связи блок 3 осуществляет контроль сообщения в соответствии с заданным методом контроля, хранение информации на время приема, формирование сигнала запроса прерывания, через упявляющий вход-выход блока, извещающего блок 6 управления об окончании приема данных из канала связи и готовности ввдачи их блоку 6 управления.

Программируемый коммутатор 48 состоит из формирователя 56, генератора 57 тактовых импульсов, элемента 58 суммирования и вычитания, дешифратора 59, регистра 60 команд, элемента 61 согласования, регистров 62, элемента 63 согласования, счетчика 64 команд, регистра 65 адреса, регистра 66 управляиицих сигналов.

Програмнируемый коммутатор 48 может быть реализован, например, на микросхеме К580ИК80 и служит для реализации программы, предназначенной для координации работы элемен тов блока 3. Программа хранится в элементе 51 памяти блока 3 и включает такие команды как чтение, запись логическую и арифмети ескую обработку данных, условные и безусловные ветвления.

Элемент 58 осуществляет обработку двоично-кодированных данных.

Блок 62 регистров осуществляет хранение и выдачу данных, участвующих в процессе обработки и выполнения заданной команды.

Регистр 60 осуществляет прием кода команды, поступающего из элемента 31 памяти, хранение его в течение выполнения команды.

Дещифратор 59 преобразует коды команд в управлякяцие сигналы.

Счетчик 64 команд предназначен для приема, формирования и хранения адреса текущей команды.

Регистр 65 адреса осуществляет прием и хранение адреса команды, считываемой из элемента 51 памяти, или адреса узлов блока и вьщачу его на элемент 63 согласования в течение цикла обращения к з лементу памяти или к узлам блока.

Формирователь 56 тактовых импульсов предназначен для выработки тактовых импульсов, синхронизирукмцих

работу составньпс частей коммутатора 48.

Элемент 61 предназначен для раз- вязки коммутатора 48 и шины 53, через которую осуществляется обмен данными между узлами блока.

Регистр 66 управляющих сигналов осуществляет формирование управляю-

щих сигналов при обмене с элементами 49, 52 и элементом 51 памяти и прием сигналов ОТВ и ЗПР соответственно от элементов 49 и 50.

Элемент 49 памяти данных состоит

из селектора 67, элементов 68 и 69 согласования, элемента 70 задержки, элементов И 71, 72, триггеров 73, 74, элемента НЕ 75, элемента 76 памяти, элементов ИЛИ 77, 78, элементов И 79, 80, элемента 81 задержки, элементов 82, 83 согласования. Формирователь 50 сигналов запроса состоит из селектора 84 адреса, элементов ИЛИ 85 и 86, элементов И 87-90 и триггеров 91, 92.

Элемент 52 ввода-вывода данных состоит из элемента 93 .согласования, дешифратора 94, формирователя 95 тактовых импульсов, регистра 96 режима, регистра 97 передачи, регистра 98 состояния, регистра 99 приема.

Элемент 52 может быть реализован, например, на микросхеме К580ИК51 и предназначен для приема и передачи

последовательных данных при работе с линией связи.

Преобразование последовательного кода в параллельный код данных и наоборот производится в регистре 99

приема и регистре 97 передачи соответственно при работе элемента 52 с линией связи.

Определение окончания преобразования осуществляется через регистр 98 состояния, соответствующий разряд которого указывает на готовность элемента 52 либо к приему, либо к передаче очередного слова данных. Регистр 96 режима предназначен для задания режима работы элемента 52 на прием или передачу данных при работе с линией связи.

Формирование сигналов выборки одного из регистров элемента 52, а также сигналов, определяющих направление движения данных через элемент 93 при работе с линией связи.

осуществляется дешифратором 94 по командам от коммутатора 48.

Синхронизация работы составных частей элемента 52 производится от формирователя 95 тактовых импульсов.

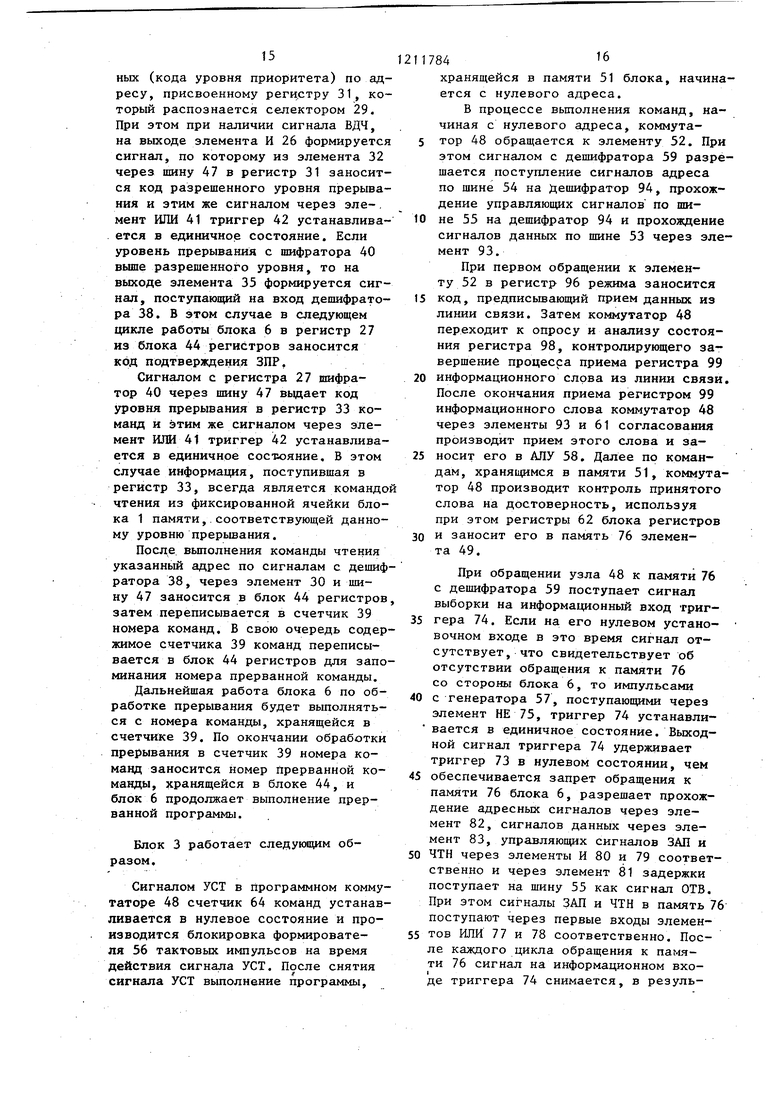

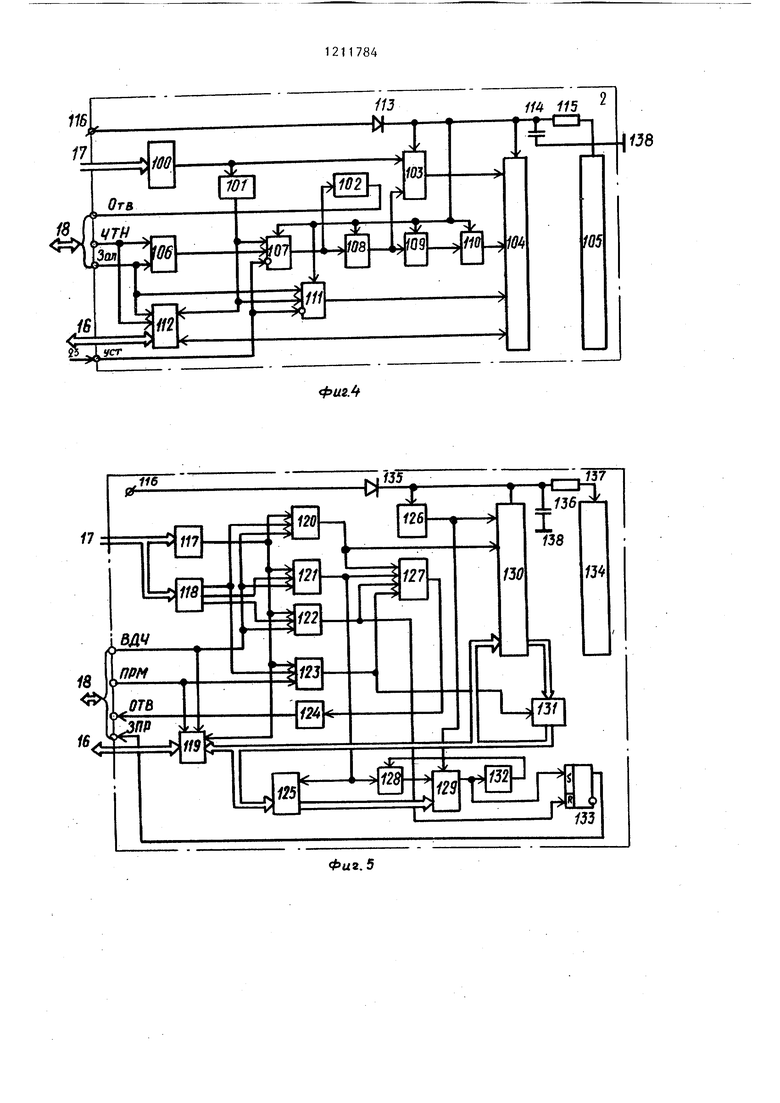

Блок 2 памяти (фиг. 4) содержит элемент 100 согласования, селектор 101 адреса, элемент 102 задержки, регистр 103, элемент 104 памяти, резервный источник 105 питания, элемент ИЛИ 106, элемент И 107 и формирователь 108 сигналов, элемент 109 задержки, формирователь 1Ш сигналов, элемент И 111, элемент 112 согласования, диод 113, конденсатор 114, резистор 115, шину 116 основного питания.

Блок 2 является энергозависимым оперативным запоминающим устройством и предназначен для хранения оперативной информации, выдаваемой в канал связи и принимаемой из него, для хранения интегральных значений параметров, для хранения уставок технологических параметров при их оперативном задании с ПУ, а также для хранения промежуточных результатов вычисления в процессе выполнения рабочей программы устройства.

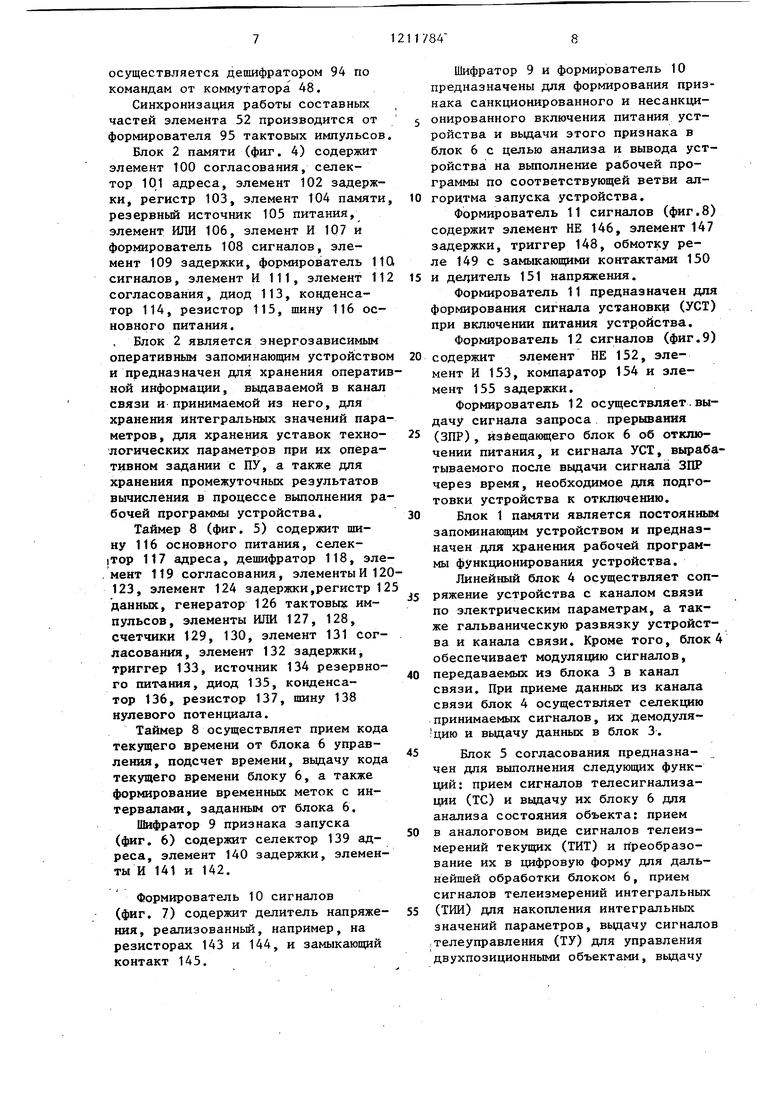

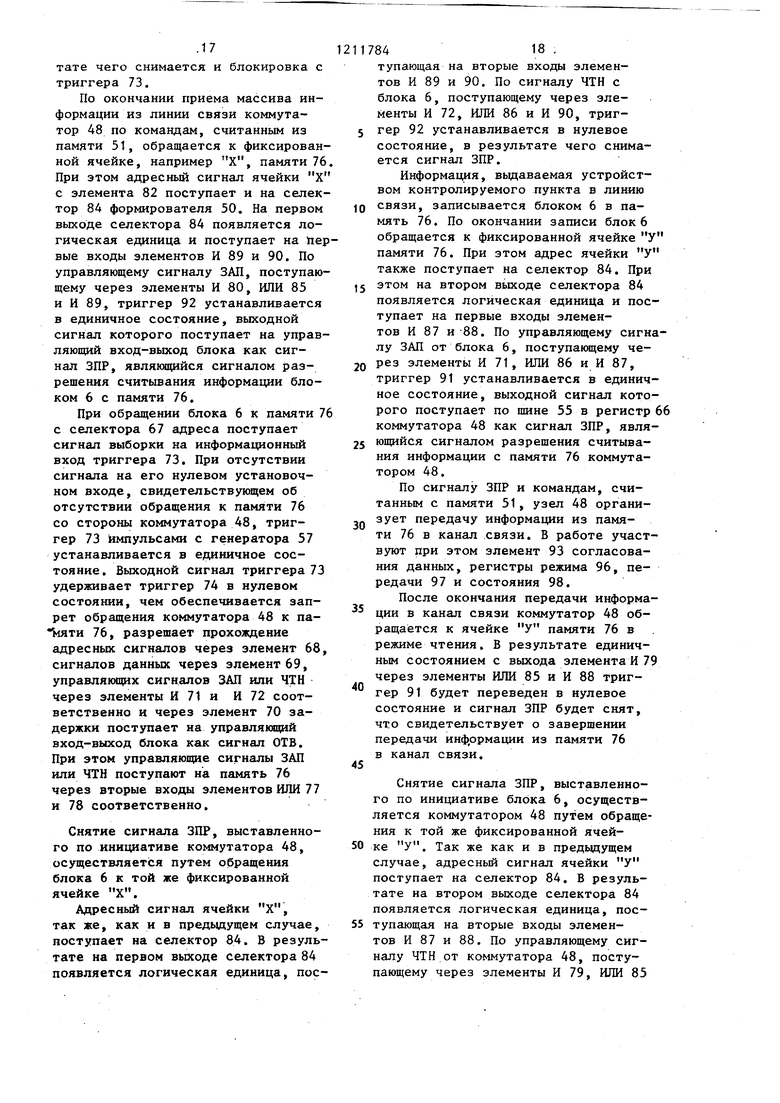

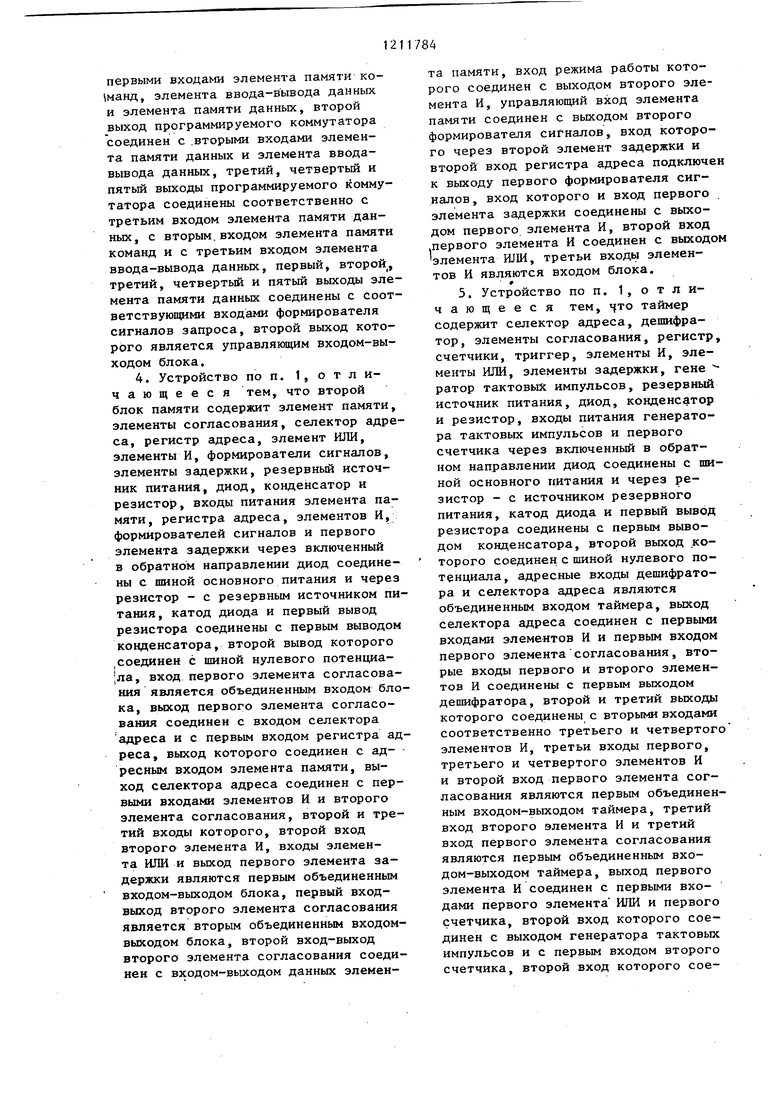

Таймер 8 (фиг. 5) содержит шину 116 основного питания, селек- Top 117 адреса, дешифратор 118, эле- мент 119 согласования, элементыИ120- 123, элемент 124 задержки,регистр 125 данных, генератор 126 тактовых импульсов, элементы ИЛИ 127, 128, счетчики 129, 130, элемент 131 согласования, элемент 132 задержки, триггер 133, источник 134 резервного пит-ания, диод 135, конденсатор 136, резистор 137, шину 138 нулевого потенциала.

Таймер 8 осуществляет прием кода текущего времени от блока 6 управления, подсчет времени, выдачу кода текущего времени блоку 6, а также формирование временных меток с интервалами, заданным от блока 6.

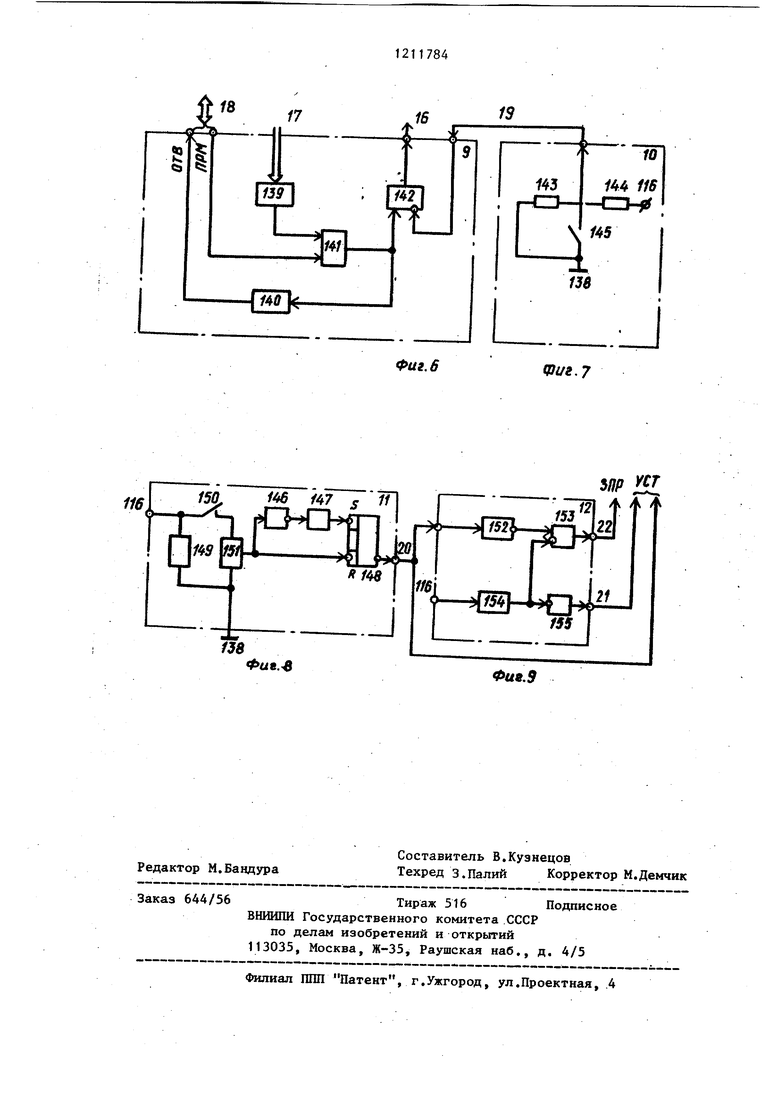

Шифратор 9 признака запуска (фиг. 6) содержит селектор 139 адреса, элемент 140 задержки, элементы И 141 и 142.

Формирователь 10 сигналов (фиг. 7) содержит делитель напряжения, реализованный, например, на резисторах 143 и 144, и замыкающий контакт 145.

Шифратор 9 и формирователь 10 предназначены для формирования признака санкционированного и несанкци- 5 онированного включения питания устройства и выдачи этого признака в блок 6 с целью анализа и вывода устройства на выполнение рабочей программы по соответствующей ветви ал- 10 горитма запуска устройства.

Формирователь 11 сигналов (фиг.8) содержит элемент НЕ 146, элемент 147 задержки, триггер 148, обмотку реле 149 с замыкающими контактами 150 15 и дедитель 151 напряжения.

Формирователь 11 предназначен для формирования сигнала установки (УСТ) при включении питания устройства.

Формирователь 12 сигналов (фиг.9) 20 содержит элемент НЕ 152, элемент И 153, компаратор 154 и элемент 155 задержки.

Формирователь 12 осуществляет.выдачу сигнала запроса прерывания 5 (ЗПР), йзйещающего блок 6 об отключении питания, и сигнала УСТ, вырабатываемого после выдачи сигнала ЗПР через время, необходимое для подготовки устройства к отключению. 0 Блок 1 памяти является постояниым запоминающим устройством и предназначен для хранения рабочей программы функционирования устройства.

Линейный блок 4 осуществляет соп- 5 ряжение устройства с каналом связи по электрическим параметрам, а также гальваническую развязку устройства и канала связи. Кроме того, блок 4 обеспечивает модуляцию сигналов, 0 передаваемых из блока 3 в канал связи. При приеме данных из канала связи блок 4 осуществляет селекцию принимаемых сигналов, их Демодуля- : цию и выдачу данных в блок 3.

5 Блок 5 согласования предназначен для выполнения следующих функций: прием сигналов телесигнализации (тс) и выдачу их блоку 6 для анализа состояния объекта: прием

0 в аналоговом виде сигналов телеизмерений текущих (ТИТ) и преобразование их в цифровую форму для дальнейшей обработки блоком 6, прием сигналов телеизмерений интегральньгх

5 (ТИИ) для накопления интегральных значений параметров, вьщачу сигналов : телеуправления (ТУ) для управления двухпозиционными объектами, вьщачу

сигналов телерегулирования кодового () для управления цифровыми регуляторами.

По информационному входу 14 блок 5 подключается к датчикам сигналов ТС, ТИТ, ТИИ объекта и пультам ручного ввода, при необходимости, а по выходу 13 управления соединяется с исполнительными устройствами объекта.

Обмен данными в блоком 6 управления осуществляется при поступлении на адресный вход и управляющий вход выход блока 5 соответствующих адресных и управлякицих сигналов от блока 6 и может производиться как по инициативе блока 6 в процессе вьшол- нения программы, хранящейся в блоке 1, так и по инициативе блока 5 при формировании им сигнала ЗПР.

Устройство контролируемого пункта работает следующим образом.

При включении питания устройства формирователь 11 вырабатывает кратковременный сигнал установки (УСТ), который через элемент ИЛИ 7 блокирует в блоке 2 памяти запись информации при переходном процессе нарастания напряжения питания до номинального уровня, а в блоке 3 обмена данными и в блоке 6 управления осуществляет сброс счетчиков адреса в нулевое состояние. После достижения напряжением питания номинального значения формирователь 11 сигнал УСТ снимает

После снятия сигнала УСТ блок 3 начинает свою работу со считывания команд, начиная с нулевого адреса своей памяти 76, и настраивается на прием данных из канала связи через вход-выход 15 и блок 4, а блок 6 начинает свою работу со считывания команды с нулевого адреса блока 1 памяти,

Команда, считанная с блока 1 по нулевому адресу, предписывает блоку 6 обращение к блоку 9 с целью приема с него бита данных, определяющего по выходному сигналу формирователя 10, было ли включение устройства санкционированным или нет. По адресному сигналу и управляющему сигналу ПРИ (Прием) от блока 6 блок 9 формирует на входе-выходе дан ных бит данных, а на управляющем входе-выходе сигнал Ответ (ОТВ).

После приема бита данных от блока 9 блок 6 по следующим командам, считанным из блока 1, переходит к 5 г о анализу. При этом состояние логической единицы указывает, что включение было санкционированным, т.е. производилось оператором, а состояние логического нуля свидетель- 10 ствует о том, что включение питания устройства произошло без участия оператора.

При санкционированном включении питания блок 6 обращается к блоку 8 15 и по шине 16 данных вводит в него значение времени, равное нулю дпя отсчета относительного времени. Кроме того, блок 6 настраивает блок 8 на формирование временных меток 20 через заданные интервалы времени.

Обращением к блоку 2 блок 6 обнуляет его массивы памяти, используемые для накопления интегральных значений параметров, и ячейки па- 25 мяти, необходимые для выполнения основной программы работы устройства. Обращением к блоку 5 блок 6 устанавливает его в исходное состояние, не нарушающее ряботу Объекта 30 ри включении питания устройства. После этого блок 6 переходит к реализации программы, включающей прием и обработку информации телесигнализации (ТС), телеизмерений текущих J (ТИТ), телеизмерений интегральных (ТИИ), формирование и вьщачу команд телеуправления (ТУ), телерегулирования кодрвого (), прием и занесение уставок технологических пара- Q метров, прием и выдачу служебной информации.

Обработка сигналов ТС содержит

следующие этапы. I

Прием блоком 6 от блока 5 сигна5 лов ТС, сравнение их с принятыми в предьщущем цикле, выявление изменившихся сигналов и Формирование словосостояния, единица в одном из битов которого указывает, что было

0 зафиксировано изменение одного или нескольких сигналов ТС. Словосостоя- ние заносится в одну из ячеек блока 2 для последующей передачи в линию связи.

5 Обработка сигналов ТИТ состоит в следующем.

Блок 6, обращаясь к блоку 5, за- пускает его на преобразование анапо

11

гичных сигналов в цифровую форму, которые поступают на информационный вход 14 устройства, по окончании преобразования производит прием кода параметров, а затем сравнение его с технологической уставкой. Если параметр не вышел за пределы техно- логической уставки, то код его значения заносится в соответствующую область памяти, блока 2. При выходе параметра за уставку его код записывается в другую область памяти блока 2 с указанием адреса этого параметра и в соответствующий бит словосостояния, хранящегося в бло- ке 2, заносится единица, указывающая что было :зафиксировано отклонение параметра от уставки.

Обработка информации ТИИ состоит в следующем..

Блок 6, обращаясь к блоку 6, принимает от него состояние уровней сигналов ТИИ, поступающих на информационный вход 14 устройства, и производит их анализ на изменение пере- пада напряжения с высокого уровня на низкий (по сравнению с состоянием сигналов, принятых в предыдущем цикле) . В случае указанного изменения сигнала, свидетельствующего об окончании сигнала ТИИ, блок 6 по адресу, соответствующему каналу, по которому изменился сигнал, увеличивает на еди ницу содержимое ячейки памяти области ТИИ блока 2.

В случае поступления информации из канала связи последняя через вход выход 15 и линейный блок 4 принимает ся блоком 3, в котором записывается S память 76. По окончании приема ин- форма1щи блок 3 формирует сигнал Запрос прерывания (ЗПР), по которому блок 6 управления считывает эту информацию и производит ее анализ. Информация, считанная из памяти 76 блока 3, всегда содержит командное слово, предписывающее выполнение тех или иных действий.

Если командное слово предписывает вьщачу в канал связи словосостояния устройства или массива ТС, или массива ТИТ, или параметров, вьшед- ших за уставку, или массива ТИИ (в конце смены, сут.), то при этом блок 6 считывает из блока 2 памяти соответствующий массив и производит запись его в память 76 блока 3.

По окончании записи информации в блок 3 блок 6 обращается к фикси

20

11

5 Q jj

25

5

30

5

0

5

0

78412

рованной ячейке памяти 76 блока 3, последний организует вьщачу информации, хранящейся в памяти 76 блока 3, через шину 24, блок 4 и вход-выход 15 устройства в канал связи.

После передачи в канал связи те- леинфорйации блок 6 обнуляет соответствующие массивы блока 2 памяти.

Если командное слово, принятое из канала связи, предписывает выполнение команды ТУ, или телерегулирование кодового ТР-К, или занесение технологических уставок, то обработка этих сигналов состоит в следующем.

По команде ТУ блок 6 управления считывает из памяти 76 блока 3 ин- формахщю об адресе канала управления и признака выполняемой операции (включить, выключить). На основании этой информации блок 6 формирует адрес канала телеуправления блока 5 и по этому адресу передает в блок 5 код признака выполняемой операции. При этом на выходе 13 блока 5 формируется сигнал включения или выключения адресуемого агрегата.

Через данное время, необходимое для выполнения команды включения или выключения агрегата, блок 6 повторно обращается к блоку 5 и обнуляет его регистр телеуправления. . Время, необходимое для выполнения команды телеуправления, зависит от времени срабатывания узлов запуска управляемого агрегата и определяется путем подсчета блоком 6 времен- ных меток, формируемых таймеров 8. По команде блок 6 управления считывает из памяти 76 блока 3 информацию об адресе канала регулирования и код управляющего воздействия и передает их в блок 5. Из блока 5 код управляющего воздействия через выход 13 устройства поступает на ад- ресуемый регулятор.

По команде занесения технологических уставок блок 6 считывает из памяти 76 блока 3 адреса уставок и код уставок и затем по этим адресам производит запись кодов уставок в блок 2 памяти.

При необходимости отсчета таймером 8 времени, единого с временем, которое отсчитывается на пункте управления, на устройство из канала связи может быть передан код значения времени, который затем считывается блоком 6 и заносится в таймер 8.

При отключении питания устройства на первом выходе формирователя 12 вьфабатывается сигнал ЗПР, который через шину 22 и управляющую шину 18 устройства поступает на управляющий вход-выход блока 6. По этому сигналу блок 6 считывает с таймера 8 текущее время и его код записывает с соответствующим признаком в массив служебной информации блока 2 памяти После этого блок 6 считьшает с блока 1 команду Останов и прекращает свою работу.

Через время, определяемое формирователем- 12, на его втором вы- ходе формируется сигнал УСТ, который через шину 21 поступает на элемент ШШ 7, сигнал с выхода которого поступает на входы блоков 2, 3, 6 и блокирует их работу.

При отключенном питании устройства блок 2 находится в режиме хранения информации, а таймер 8 продолжает отсчет времени.

При несанкционированном включе- НИИ питания устройства блок 6 обра- .щается к таймеру 8, считывает с него код значения времени и записывает его с соответствующим признаком в массив служебной информации блока 2. Затем блок 6 формирует словосостоя- ние, соответствующий бит которого указывает, что происходил несанкционированный останов .

Кроме того, блок 6, обращаясь к блоку 5, устанавливает его в исходное состояние, не нарушающее работу объекта при включении устройства, после чего устройство переходит к выполнению рабочей программы по реализации алгоритма приема и обработки телеинформации.

Блок 6 управления работает сле- дукнцим образом.

Сигналом УСТ счетчик 39 номера команд устанавливается в нулевое состояние, а формирователь 37 тактовых импульсов блокируется. После снятия сигнала УСТ формирователь 37 запускается от генератора 36 и выда- ет позиционный сигнал, поступающий на регистр 27 управляющих сигналов и нулевой установочный вход триггера 42, и серию тактовых импульсов, поступающих на дешифратор 38.

При обращении блока 6 к блокам устройства код выполняемой операции из блока 44 регистров общего назначения через шину 47 заносится в регистр 27 управляющих сигналов. Чере время задержки, определяемое элементом 43, код операции из регистра 27 поступает в дешифратор 25, который при этом формирует соответствующий коду один из управляющий сигналов: ЧТН или ЗАП при обращении к блокам памяти, ПРИ или ВДЧ при обращении к блокам ввода-вывода. Адрес адресуемого блока из счетчика 39 номера команд заносится в регистр 34, а с него - в элемент 28 согласования, выход которого является адресным выходом блока 6.

По управляющему сигналу ЧТН или ПРМ адресуемый блок выставляет данные и сопровождает их сигналом ОТВ. По сигналу ОТВ, поступающему через элемент ИЛИ 41, триггер 42 устанавливается в единичное состояние. При этом дешифратор 38 вырабатывает сигнал, разрешающий прохождение данных через элемент 30 в регистр 33 команд или в элемент 32, или в блок 44 регистров .

Через время задержки, определяемо элементом 43, с выхода дешифратора 25 снимается управляющий сигнал. После этого дешифратором 38 вьфабатывается сигнал, запрещающий вьщачу адресных сигналов с выхода элемента 28. Если данные поступили в регистр 33 команд, то дешифратор 38 дешифрирует их и после этого на соответствующих выходах вырабатывает сигналы, обеспечивающие выполнение принятой команды. I

По управляющему сигналу ЗАП или

ВДЧ данные адресуемому блоку вьщают- ся из элемента 32 через элемент 30 одновременно с адресными сигналами. Сигналы запроса прерывания (ЗПР, ... ЗПР„) от инициативных блоков устройства поступают на управляющий Вход-выход блока и заносятся в регистр 46. При одновременном поступлении нескольких сигналов ЗПР селектор 45 вьщеляет сигнал с высшим приоритетом, который затем кодируется шифратором 40 и поступает на один из входов элемента 35 сравнения. На другой вход элемента 35 поступает код разрешенного уровня прерывания из регистра 31. Занесение кода разрешенного уровня прерывания в регистр 31 осуществляется при выполнении команды выдачи дан13

ных (кода уровня приоритета) по адресу, присвоенному регистру 31, который распознается селектором 29. При этом при наличии сигнала ВДЧ, на выходе элемента И 26 формируется сигнал, по которому из элемента 32 через шину 47 в регистр 31 заносится код разрешенного уровня прерывания и этим же сигналом через эле-, мент ИЛИ 41 триггер 42 устанавливается в единичное состояние. Если уровень прерывания с шифратора 40 выше разрешенного уровня, то на выходе элемента 35 формируется сигнал, поступающий на вход дешифратора 38. В этом случае в следующем цикле работы блока 6 в регистр 27 из блока 44 регистров заносится код подтверждения ЗПР,

Сигналом с регистра 27 шифратор 40 через шину 47 вьщает код уровня прерывания в регистр 33 команд и этим же сигналом через элемент ИЛИ 41 триггер 42 устанавливается в единичное состояние. В этом случае информация, поступившая в регистр 33, всегда является командо чтения из фиксированной ячейки блока 1 памяти,.соответствующей данному уровню прерьшания.

После выполнения команды чтения указанный адрес по сигналам с дешифратора 38, через элемент 30 и шину 47 заносится в блок 44 регистров затем переписывается в счетчик 39 номера команд. В свою очередь содержимое счетчика 39 команд переписывается в блок 44 регистров для запоминания номера прерванной команды.

Дальнейшая работа блока 6 по обработке прерывания будет выполняться с номера команды, хранящейся в счетчике 39. По окончании обработки прерывания в счетчик 39 номера команд заносится номер прерванной команды, хранящейся в блоке 44, и блок 6 продолжает выполнение прерванной программы.

Блок 3 работает следующим образом.

Сигналом УСТ в программном коммутаторе 48 счетчик 64 команд устанавливается в нулевое состояние и производится блокировка формирователя 56 тактовых импульсов на время действия сигнала УСТ. После снятия сигнала УСТ выполнение программы.

11784

хранящейся в памяти 51 блока, начинается с нулевого адреса.

В процессе выполнения команд, начиная с нулевого адреса, коммута- 5 тор 48 обращается к элементу 52. При этом сигналом с дешифратора 59 разрешается поступление сигналов адреса по шине 54 на Дешифратор 94, прохождение управляющих сигналов по ши10 не 55 на дешифратор 94 и прохождение сигналов данных по шине 53 через элемент 93.

При первом обращении к элементу 52 в регистр 96 режима заносится

15 код, предписывающий прием данных из линии связи. Затем коммутатор 48 переходит к опросу и анализу состояния регистра 98, контролирующего завершение процесса приема регистра 99

20 информационного слова из линии связи. После окончания приема регистром 99 информационного слова коммутатор 48 через элементы 93 и 61 согласования производит прием этого слова и за-

25 носит его в АЛУ 58. Далее по командам, хранящимся в памяти 51, коммутатор 48 производит контроль принятого слова на достоверность, используя при этом регистры 62 блока регистров

30 и заносит его в память 76 элемента 49.

При обращении узла 48 к памяти 76 с дешифратора 59 поступает сигнал выборки на информационный вход триг35 гера 74. Если на его нулевом установочном входе в это время сигнал отсутствует, что свидетельствует об отсутствии обращения к памяти 76 со стороны блока 6, то импульсами

40 с генератора 57, поступающими через элемент НЕ 75, триггер 74 устанавливается в единичное состояние. Выходной сигнал триггера 74 удерживает триггер 73 в нулевом состоянии, чем

45 обеспечивается запрет обращения к памяти 76 блока 6, разрещает прохождение адресных сигналов через элемент 82, сигналов данных через элемент 83, управляющих сигналов ЗАП и

50 ЧТН через элементы И 80 и 79 соответственно и через элемент 81 задержки поступает на шину 55 как сигнал ОТВ. При этом сигналы ЗАП и ЧТН в память 76 поступают через первые входы элемен55 тон ИЛИ 77 и 78 соответственно. После каждого цикла обращения к памяти 76 сигнал на информационном входе триггера 74 снимается, в резуль.17

тате чего снимается и блокировка с триггера 73.

По окончании приема массива информации из линии связи коммутатор 48 по командам, считанным из памяти 51, обращается к фиксированной ячейке, например X, памяти 76. При этом адресный сигнал ячейки X с элемента 82 поступает и на селектор 84 формирователя 50. На первом выходе селектора 84 появляется логическая единица и поступает на Первые входы элементов И 89 и 90. По управляющему сигналу ЗАП, поступающему через элементы И 80, ИЛИ 85 и И 89, триггер 92 устанавливается в единичное состояние, выходной сигнал которого поступает на управяющий вход-выход блока как сигнал ЗПР, являющийся сигналом разрешения считывания информации блоком 6 с памяти 76.

При обращении блока 6 к памяти 76 с селектора 67 адреса поступает сигнал выборки на информационный вход триггера 73. При отсутствии сигнала на его нулевом установочном входе, свидетельствующем об отсутствии обращения к памяти 76 со стороны коммутатора 48, тригер 73 импульсами с генератора 57 устанавливается в единичное сосояние. Выходной сигнал триггера 73 удерживает триггер 74 в нулевом остоянии, чем обеспечивается запет обращения коммутатора 48 к па- ти 76, разрешает прохождение дресных сигналов через элемент 68, игналов данных через элемент 69, правляющих сигналов ЗАП или ЧТН ерез элементы И 71 и И 72 соотетственно и через элемент 70 заержки поступает на управлякщий ход-выход блока как сигнал ОТВ. ри этом управляющие сигналы ЗАП ли ЧТН поступают на память 76 ерез вторые входы элементов ИЛИ 77 78 соответственно.

Снятие сигнала ЗПР, выставленного по инициативе коммутатора 48, осуществляется путем обращения блока 6 к той же фиксированной чейке X.

Адресный сигнал ячейки X, ак же, как и в предыдущем случае, оступает на селектор 84. В резульате на первом выходе селектора 84 оявляется логическая единица, пос1211784

ту тов бло ме

5 гер сос етс

вом

0 свя мя обр пам так

5 это поя туп тов лу

20 рез три ное рог ком

25 ющи ния тор

тан зуе ти вую ния ред

ции ращ реж ным чер гер сос что пер

в к 45

го ляе ния

50 ке слу пос тат поя

55 туп тов нал паю

30

35

40

18 .

тупающая на вторые входы элементов И 89 и 90. По сигналу ЧТН с блока 6, поступающему через элементы И 72, ИЛИ 86 и И 90, триггер 92 устанавливается в нулевое состояние, в результате чего снимается сигнал ЗПР.

Информация, выдаваемая устройством контролируемого пункта в линию

связи, записывается блоком 6 в память 76. По окончании записи блок 6 обращается к фиксированной ячейке У памяти 76. При этом адрес ячейки У также поступает на селектор 84. При

этом на втором выходе селектора 84 появляется логическая единица и поступает на первые входы элементов И 87 и 88. По управляющему сигналу ЗАП от блока 6, поступающему через элементы И 71, ИЛИ 86 и И 87, триггер 91 устанавливается в единичное состояние, выходной сигнал которого поступает по шине 55 в регистр 66 коммутатора 48 как сигнал ЗПР, являющийся сигналом разрешения считывания информации с памяти 76 коммутатором 48.

По сигналу ЗПР и командам, считанным с памяти 51, узел 48 организует передачу информации из памяти 76 в канал связи. В работе участвуют при этом элемент 93 согласования данных, регистры режима 96, передачи 97 и состояния 98.

После окончания передачи информации в канал связи коммутатор 48 обращается к ячейке У памяти 76 в режиме чтения. В результате единичным состоянием с выхода элемента И 79 через элементы ИЛИ 85 и И 88 триггер 91 будет переведен в нулевое состояние и сигнал ЗПР будет снят, что свидетельствует о завершении передачи информации из памяти 76

в канал связи.

Снятие сигнала ЗПР, выставленного по инициативе блока 6, осуществляется коммутатором 48 путем обращения к той же фиксированной ячейке У. Так же как и в предыдущем случае, адресньш сигнал ячейки У поступает на селектор 84. В результате на втором выходе селектора 84 появляется логическая единица, поступающая на вторые входы элементов И 87 и 88. По управляющему сигналу ЧТИ от коммутатора 48, поступающему через элементы И 79, ИЛИ 85

19

и И 88, триггер 91 устанавливается в нулевое состояние, в дзезультате чего сигнал ЗПР снимается.

Блок 2 памяти работает следующим образом.

Работа блока происходит в режиме записи, чтения и хранения информации. Запись и чтение информации осуществляется при поступлении на адресный вход, вход-выход данных и управляющий вход-выход блока соотвественно адресных сигналов, сигналов данных и управляющих сигналов ЗАЛ или ЧТН. При этом адресные сигналы через элемент 100 согласования адре са поступают на вход селектора 101 адреса и на первый вход регистра 10 111ри совпадении адреса блока с адресом, записанным в селектор 101, на выходе селектора 101 формируется сигнал выборки, который поступает на первые входы элементов И 107 и 111 и элемента 112. Сигналы ЧТН или ЗАЛ поступают соответственно на второй и третий входы элемен- та 112 и определяют направление прохождения данных через элемент 112.

Режим работы блока определяется сигналом на выходе элемента И 111. Логическая 1 соответствует режиму записи, а логический О - режиму чтения.

I

Сигналом с выхода элемента И 107

запускается формирователь 108, сигнал с выхода которого блокирует ре- гистр 103, обеспечивая неизменность сигналов на его выходе при возможном изменении адресных сигналов в результате воздействия помех на первый вход регистра 103. Через время, определяемое элементом 109 задержки, формирователь 110 вьфабатывает сигнал, разрешающий запись или чтение в зависимости от уровня сигнала на первом входе элемента 104 памяти. На выходе элемента 102 задержки фО рмируется сигнал ОТВ, поступающий на управляющий вход-вькод блока 2.

Лри номинальном значении напряжения на шине 116 основного питания происходит подзаряд резервного источника 105 питания через диод 113, конденсатор 114 и резистор 115.

При исчезновении напряжения на шине 116 основного питания на вход блока по шине 23 поступает сигнал УСТ, по которому на выходах элементов И 107 и 111 появляются логи78420

ческие нули. При этом работа элементов 108, 109 и 110 блокируется, в результате чего исключается возможность записи информации в элемент 10 памяти и блок переводится в режим хранения информации.

Питание элементов 104, 103, 107- 111 осуществляется от резервного источника 105, чем обеспечивается правильное выполнение операций записи и чтения в моменты отключения и включения основного питания устройства, в том числе и блока 2, когда делитель входных сигналов блока может быть искажен (уменьшен).

Работа таймера 8 происходит следющим образом.

Адресное слово, поступающее на адресный вход таймера, содержит код адреса таймера, распознаваемый селектором 117, и код режима работы, дешифрируемый дешифратором 118.

При совпадении кода адреса с адресом таймера селектор 117 вьщает сигнал, поступающий на входы элементов И 120-123 и на элемент 119. J Дешифратор 118 в зависимости от кода режима работы таймера на одном из своих выходов вьщаеТ сигнал, который поступает с первого выхода на элементы И 120 и 123, со второго на элемент И 121 и с третьего - ца элемент И 122.

При наличии сигнала на первом выходе дешифратора 118 таймер в зависимости от управляницего сигнала выдает или принимает код текущего времени.

По управляющему сигналу ВДС осуществляется режим вьщачи. При этом разрешается прохождение кода теку- ще1го времени с вход-выхода данных таймера через элемент 119, а на выходе элемента И 120 вырабатывается сигнал, по которому происходит занесение этого кода в счетчик 130. Сигнал с выхода элемента И 120 через элемент ИЖ 127 и элемент 124 задержки поступает также на управляющий вход-выход таймера как сигнал ОТВ.

По управляющему сигналу ПРИ осуществляется режим приема. При этом открывается элемент 119 согласования, а на выходе элемента И 123 вырабатывается сигнал, по которому открьшается элемент 131 и код текущего времени со счетчика 130 через элемент 119 и вход-выход данных тай21

мера поступает на шину 16, По этому же сигналу формируется сигнал ОТВ так же, как и в режиме выдачи.

При наличии сигнала на втором выходе дешифратора 118 осуществляет- ся режим приема кода временного интервала, определяющего периодичность формирования запроса прерывания (ЗПР Управляющим сигналом в этом режиме является сигнал ВДЧ. По нему разре- шается прохождение кода временного интервала через элемент 119 согласования данных на вход регистра 125, а на выходе элемента И 121 вырабатывается сигнал, по которому происхо- дит занесение этого кода в регистр 1 и через элемент ИЛИ 128 разрешается занесение его с регистра 125 в счетчик 129. По этому сигналу через элемент ИЛИ 127 и элемент 124 задерж ки формируется сигнал ОТВ.

Счетчик 129 заполняется тактовыми импульсами с генератора 126 до переполнения, после чего на его выходе формируется сигнал, по которому триггер 133 устанавливается в единичное состояние. Сигнал с единичного выхода триггера 133 поступает на управляющий вход-выход блока как сигнал ЗПР, являющийся временной меткой. По сигналу с выхода счетчика 129 через элемент 132 задержки и элемент ИЛИ 128 код временного интервала с регистра 125 переписывается в счетчик.

При наличии сигнала на третьем . выходе дешифратора 118 осуществляется режим сброса сигнала ЗПР. Управляющим сигналом в этом случае также является сигнал ВДЧ. По нему на выходе элемента И 122 формируется сигнал, который производит установку триггера 133 в нулевое состояние, в результате чего происходит сброс сигнала ЗПР, и через элемент ИЛИ 127 и элемент 124 задержки формируется сигнал ОТВ.

При нгшичии питания на шине 116 через диод 135, конденсатор 136 и резистор 137 происходит подзаряд резервного источника 134 питания.

При исчезновении питания на шине 116 функционирование генератора 126 тактовых импульсов и счетчика 130 будет продолжаться за счет получения питания от резервного источника 134, чем обеспечивается продолжение отсчета времени.,

s 5 0

5 о

5

0

5

0

5

78422

Работа шифратора 9 происходит следующим образом.

При поступлении на объединенный вход кода адреса шифратора на выходе селектора 139 формируется логическая единица,поступающая на пер- вьй вход элемента И 141. По управляющему сигналу ПРМ, поступающему на второй вход элемента И 141, на его выходе появляется логическая единица, которая поступает на элемент 140 задержки и на первый вход эл.емента И 142. На второй вход элемента И 142 по шине 19 поступает сигнал с выхода формирователя 10.

При наличии на выходе формирователя 10 логического нуля на выходе элемента И 142 будет логическая единица, которая поступает на выход данных блока и воспринимается блоком 6 как сигнал о санкционированном включении основного питания.

В остальных случаях, например после аварийного самоотключения питания, на выходе формирователя 10 а следовательно, и на выходе данных блока будет логический нуль, который воспринимается блоком 6 как сигнал о несанкционированном включении основного питания.

По истечении времени выдержки, задаваемой элементом 140, на управляющем входе-выходе блока формируется сигнал ОТВ, извещающий блок 6 управления об окончании выполнения предписанной операции.

Работа формирователя 10 происходит следующим образом.

При санкционированном включении основного питания контакт 145 замыкается, резистор 143 шунтируется и на вход формирователя подается потенциал, соответствующий логическому нулю.

При несанкционированном включении основного питания замыкание контакта 145 не происходит и на выход формирователя подается потенциал , соответствующий логической единице.

Работа формирователя 11 происходит следующим образом.

При включении основного питания до тех пор, пока напряжение на шине 116 не достигнет номинального значения, контакт 150 разомкнут, делитель 151 обесточен, триггер 148 , установлен в нулевое состояние и на

23

его инверсном выходе будет логическая единица, которая поступает на выход формирователя и является сигналом установки (УСТ) блоков устройства в исходное состояние.

Когда напряжение на пшне 116 достигнет номинального значения, контакт 150 замкнется, на делитель 151 будет подано напряжение и на его выходе появится потенциал, соответствующий логической единице, который через элемент НЕ 146 и элемент 147 задержки установит триггер 148 в единичное состояние. В результате на , инверсном выходе триггера 148 будет логический нуль, по.которому на выходе формирователя сигнал УСТ будет снят.

Работа формирователя t2 происходи следующим образом.

При пониженном напряжений на шине 116 основного питания компаратор 154 вырабатывает сигнал, соответствующий логическому нулю, который поступает на инверсный вход элемент И 153. На прямом входе элемента И 153 при этом будет логическая единица, так как из-за гистерезиса релейный элемент 149 формировате- ля 11 разомкнет контакт 150 только при значительном понижении напряжения. В результате на выходе элемента будет логическая единица, соответствующая сигналу ЗПР, извещающего по шине 22 блок 6 управления об отключении питания. Через время, необходимое для подготовки устройства к отключению, сигнал с выхода компаратора 154 поступает также через элемент 155 задержки на выход формирователя как сигнал УСТ.

Таким образом, введение в устрой- .ство блока памяти, таймера, блдка обмена данными, элемента ЮШ, шифратора признака запуска, первого, второго и третьего формирователей сигналов расширяет функциональные возможности и повышает коэффициент использования оборудования устройства.

Действительно, введение блока памяти, исключающего запись ложной информации при включении и отключении питания устройства, а также позволяющего хранить записанную инфор11784

24

0

5

0

5

0

5

0

5

мацию при отключенном питания устройства, обеспечивает в устройстве накопление в течение длительного .времени статистической информации без опасения ее разрушения при отключениях питания.

Возможность накопления статистической информации в течение длительного времени в свою очередь исключает необходимость периодической ее передачи в линию связи, что разгружает канал связи для передачи оперативной информации.

Введение блока обмена данными позволяет производить обмен информацией через линию связи, в том числе формирование протокола.сообщения, организацию защиты сообщения и контроль принимаемого сообщения без непосредственного участия в этих - операциях блока управления. Это по- вьшает коэффициент использования оборудования за счет более рацир- нального распределения функций между блоком обмена даннь и и блоком управления. При этом блок управления высвобождается от участия в обмене данными через линию связи для более эффективного использования при сборе и обработке телеинформации .

Наличие таймера позволяет с чы- сокой точностью фиксировать время включения и отключения питания устройства, а также производить отсчет времени при отключенном питании, это очень важно для контроля работы необслуживаемых устройств контролируемых пунктов, что в свою очередь расширяет 4 ункциональные возможности предлагаемого устройства.

Введение в предлагаемом устройстве первого, второго и третьего формирователей, элемента ИЛИ, а также шифратора признака запуска с соответствующими связями также расширяет функциональные возможности устройства за счет реализации функции ввода устройства на рабочий режим функционирования по заданной ветви алгоритма без участия оператора, а также за счет исключения потерь оперативной информации при отключении питания устройства.

Фиг.1

23

Г8

17

h 7ff

25 Н

28 г9

7

S

32 УзГ

LL

37 КTW

39

0

42

-Н «J

5

Фиг,. 2

М

ФигА

77Э

m

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

| Устройство для имитации неисправностей | 1988 |

|

SU1661766A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1989 |

|

SU1734098A1 |

| Устройство для обмена данными | 1989 |

|

SU1700562A1 |

| Устройство микропроцессорной связи | 1978 |

|

SU734657A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

Фиг. 5

J

18

17

пщ

16

IS

f43

10 У44 116

п

т

145

14Ги.

.J

Фиг. 6

ipi/g.7

138

Фил.-6

ЪПР УСТ

Фи8.9

Редактор М.Бандура

Заказ 644/56Тираж 516 Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д. 4/5

Филиал ШШ Патент, г.Ужгород, ул.Проектная, .4

Составитель В.Кузнецов

Техред 3.Палий Корректор М.Демчик

| Устройство контролируемого пункта системы телеизмерения | 1980 |

|

SU858062A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Вопросы промышленной кибернетики, тру;9Ы ЦНИИКА | |||

| М.: Энергия, 1980, Bbini 62, № 9. | |||

Авторы

Даты

1986-02-15—Публикация

1983-11-21—Подача