I t

Изобретение относится к вычислительной технике, в частности к устройствам контроля логических схем, и может быть применено при построении аппаратуры автоматического контроля приборов систем-автоматического управления.

Известно устройство для проверки функционирования логических схем, . содержащее блок входных и- эталонных выходных сигналов, блок контролируемых выходов, реализованный на магазинной памяти переменного объема, коммутатор, блок сравнения, блоки контрольных регистров со схемами сравнения на нуль, обеспечивающие поразрядный контроль работы магазинных памятей по модулю два после подачи последовательности контролируемых выходов, блок индикации неисправности проверяемого устройства, блок ввода, блок управления, обеспечивающий начальную установку устройства, осуществление режимов проверки однотактного, циклического управления вводом данных, анализ состояния схем сравнения, управление работой блока индикации неисправности. Указанное устройство позволяет проверять на работоспособность логические схемы, реализующие различного вида булевые функции lj .

Однако устройство представляет собой достаточно сложное и дорогостоящее оборудование, рпр еделения неисправности в мажоритарных. схемах требуются специальные тестовые наборы, что усложняет процесс контроля.

Известно также устройство для проверки функционирования логических схем, содержащее генератор импульсов, запускающий двоичный счетчик с количеством разрядов, равным максимальному числу входов проверяемой логической схемы, схему контрол уровней, определяющую нахождение выходного напряжения проверяемой схемы в допустимых пределах, компаратор, сравнивающий сигналы проверяемой и эталонной .схем при всех возможных комбинациях входных сигналов, формирователь стробирующих.импульсов, элементы И, ИЛИ,, ИЛИ-НЕ и индикаторные элементы zj .

Однако для работы такого устройства необходимы эталонные схемы,

7б432

применение которых не оправдано,так как их функции могут быть реализованы с помощью тестовых наборов выходных и входных сигналов,кроме то5 го, индикация неисправности происходит на одному импульсу несовпадения, . что приводит к возникновению сбоев, появлению ложных срабатываний, усложняющих отыскание неисправностей.

0 Наиболее близким техническим

рещением к изобретению является устройство для контроля мажоритарных схем, содержащее генератор импульсов такта, вьздающий контрольную посs ледовательность импульсов на один

из входов компаратора, на второй вход которого поступает контролируемая последовательность с объекта контроля, управляющие импульсы на которой

0 поступают через шифратор с реверсивного распределителя, который в свою очередь тактируется импульсами генератора тактовых импульсов. С выхода компаратора и второго выхода

5 генератора импульсов такта импульсы поступают на схему И, которая управляет реверсивным распределителем через вход сложения. При неисправном объекте контроля, т.е. при

0 отсутствии импульса на выходе компаратора на вычитающий вход реверсивного распределителя и счетчик импульсов через сумматор по модулю два поступает сигнал, распределитель делает шаг назад, а счетчик импульсов сосчитывает один импульс. Если это не случайный сбой, картина повторяется трижды иС помощью устройства сброса приводится в исходное

M.

состояние и выключается

Недостатками известного устройства являются невысокая точность установления места неисправности и невозможность определения типа не, исправности, так как в устройстве отсутствуют, регистр памяти и дешифратор, идентифицирующие тип и место неисправности.

Целью изобретения является снижение трудоемкости обнаружения неисправности за счет повышения точности определения места и установления типа неисправности.

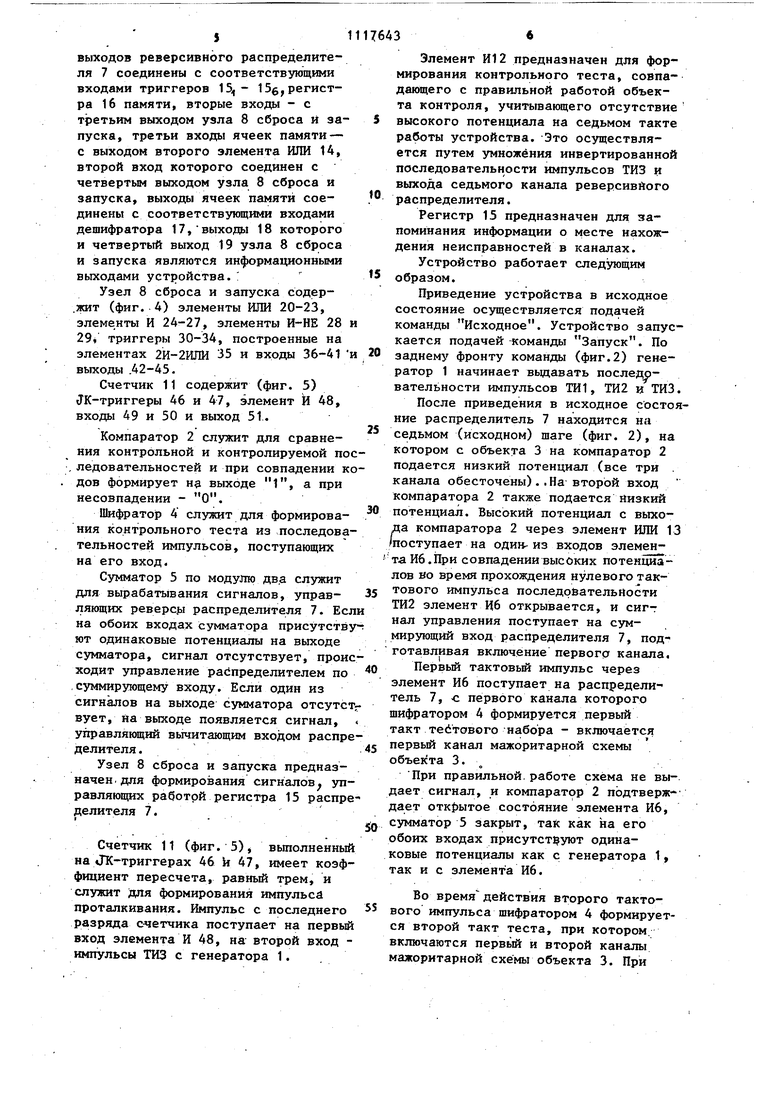

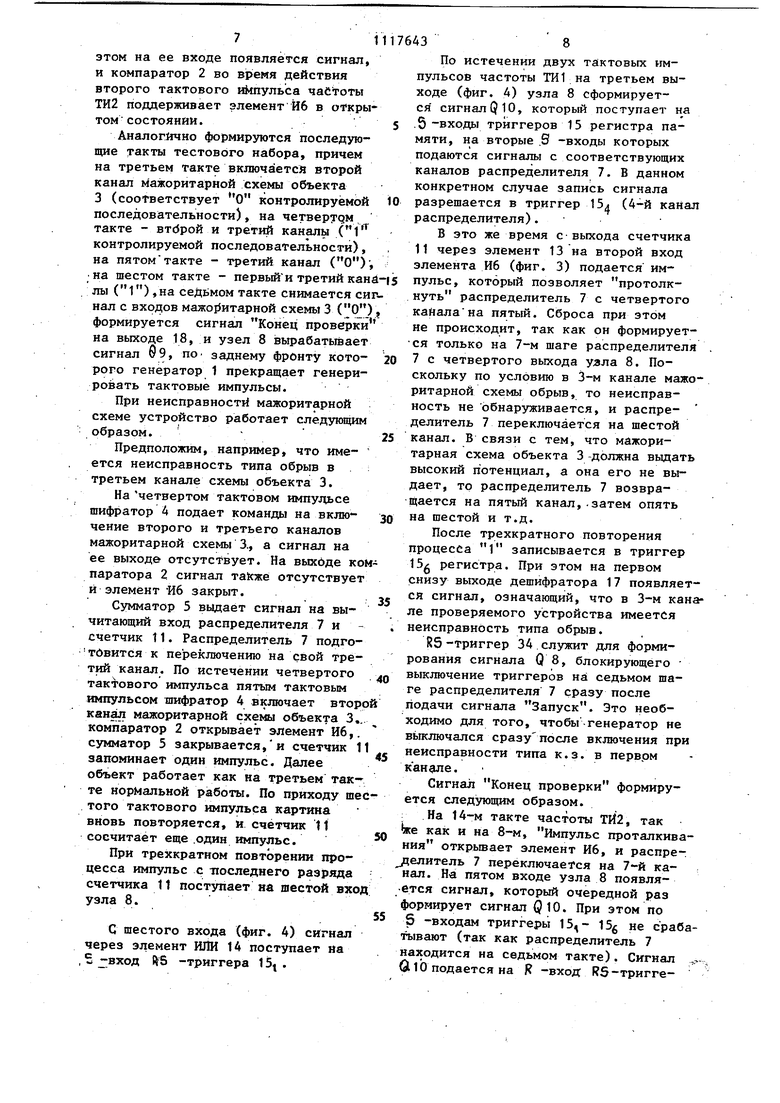

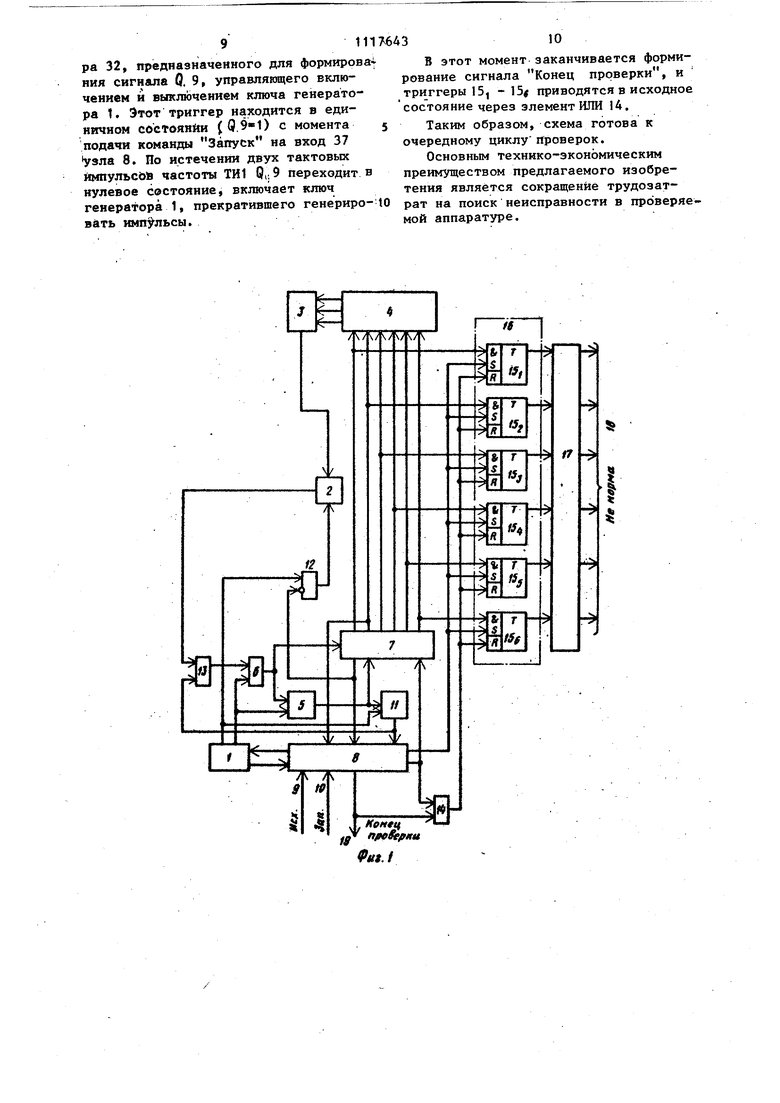

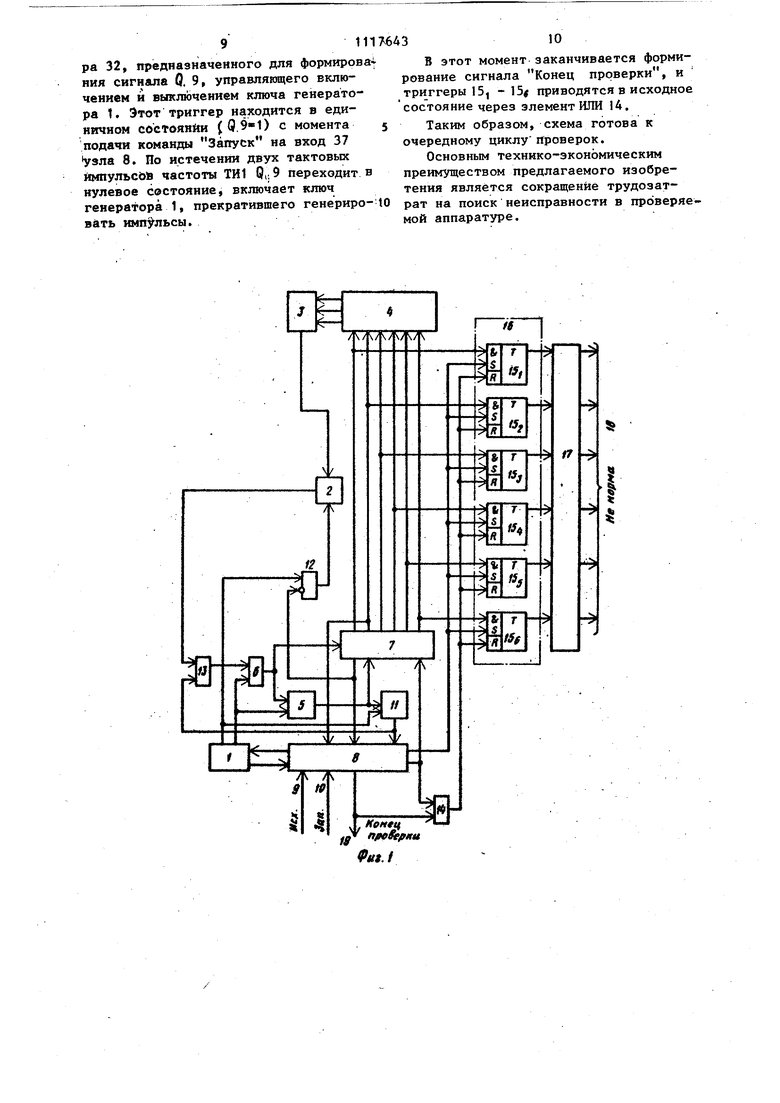

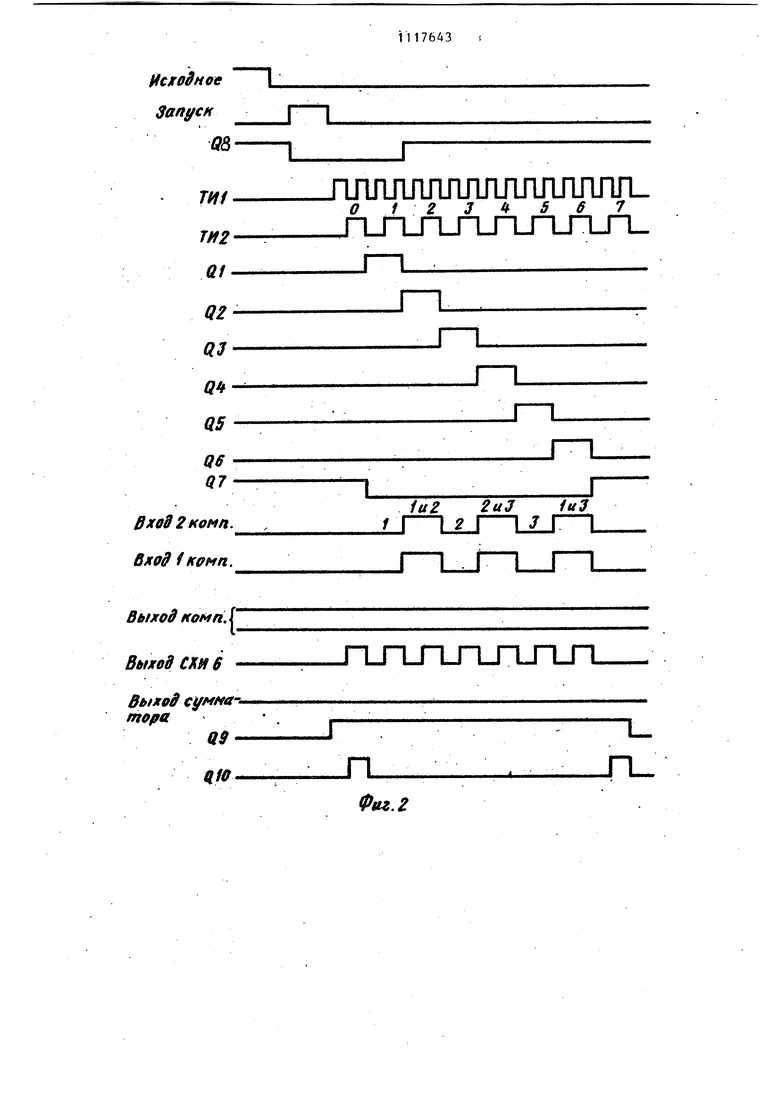

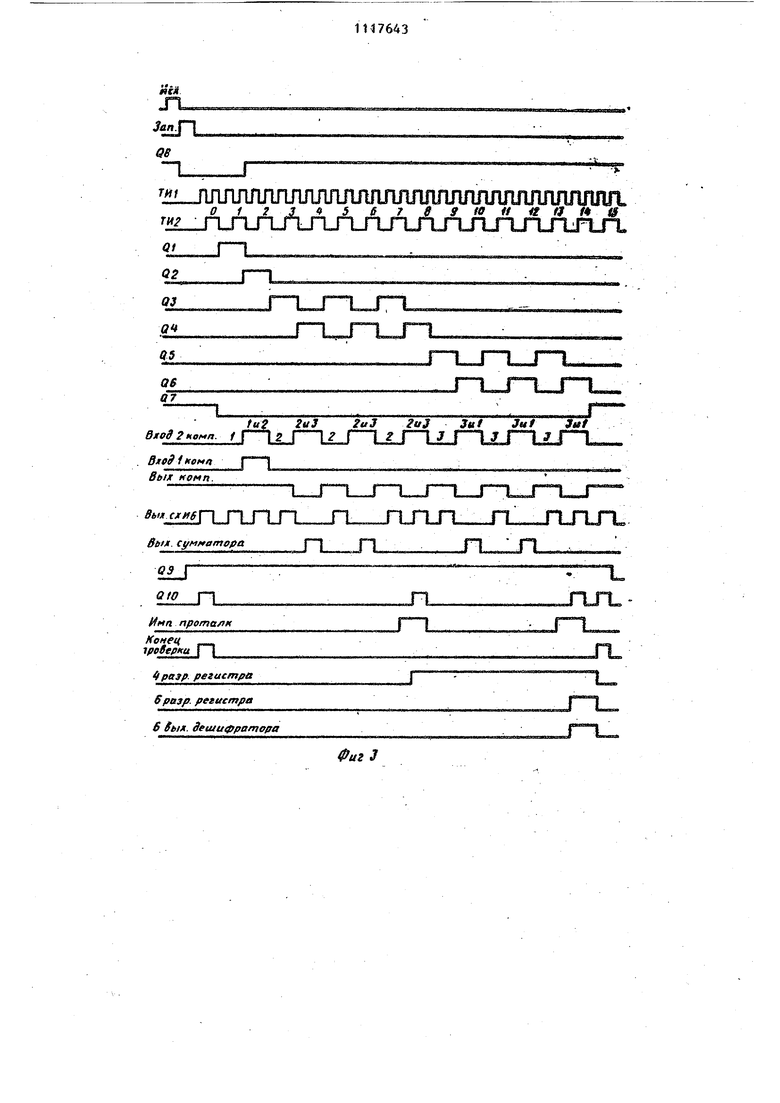

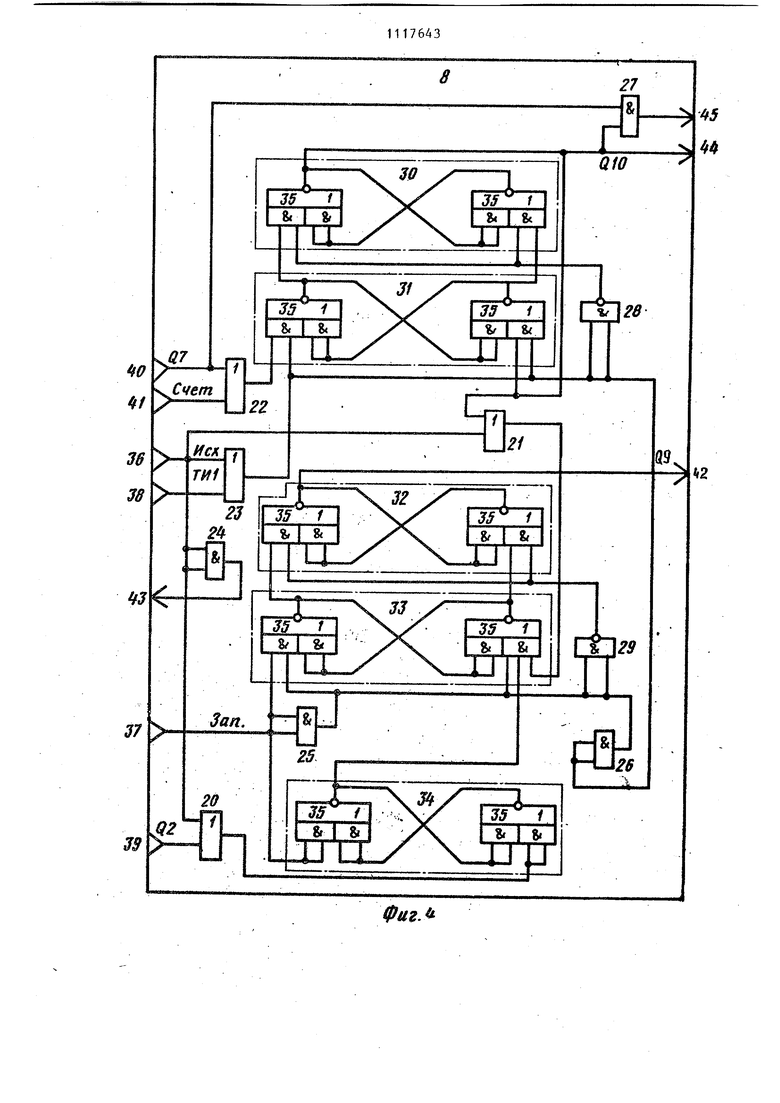

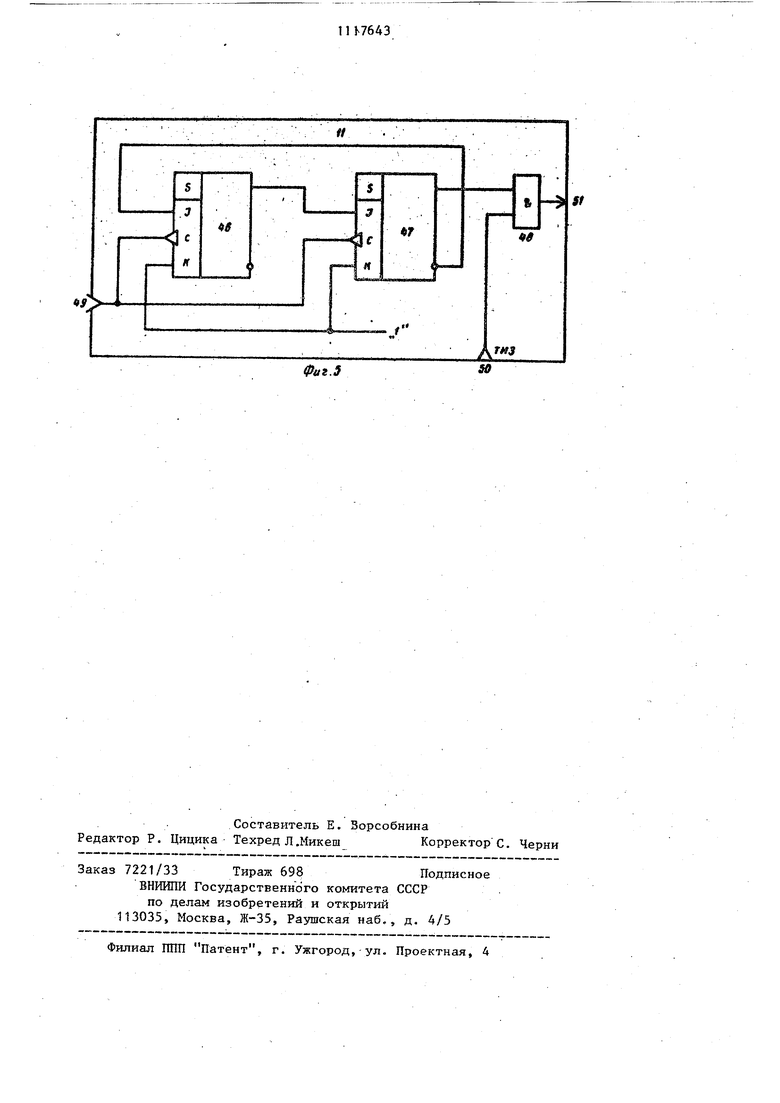

Поставленная цель достигается 5 тем, что в устройство для контроля мажоритарных схем, содержащее компаратор, первый вход которого соединен с выходом объекта контроля, шифратор, три выхода которого соединены с соответствующими-входами объек та контроля, сумматор по модулю.два первый элемент И, генератор тактовых импульсов, первый выход которого со динен с первьми входами первого эле мента И и сумматора по модулю два,. реверсивный распределитель, первые шесть выходов которого подключены к шести входам шифратора, узел сброса и запуска, первые два входа которог являются управляющими, третий вход соединен с вторым выходом генератора тактовых импульсов, а четвертый и пятый входы соединены соответственно с вторым и седьмым выходами распределителя, счетчик импульсов, первый вход которого подключен к выходу сумматора и первому входу ра пределителя, а выход соединен с шее тым входом узла.сброса и запуска, введены два элемента ИЛИ, второй элемент И, регистр памяти и дешифратор, при этом первый вход второго элемента И подключен к третьему выходу генератора тактовых импульсов и второму входу счетчика импуль сов, второй инверсный вход которого соединен с седьмым выходом распреде лителя, а выход - с вторым входом компаратора, выход которого подключен к первому входу первого элемента ИЛИ, второй вход которого соединен с выходом счетчика, а выход с вторым входом первого элемента И, выход которого подключен к вторым входам реверсивного распределителя сумматора по модулю два, первый выход узла сброса и запуска соединен с первым входом генератора тактовых импульсов, второй выход узла сброса и запуска соединен с третьим входом распределителя и первым вхо- дом второго элемента ИЛИ, первые шесть выходов реверсивного распреде лителя соединены с соответствующими первыми входами регистра памяти, вт рые входы которого подключены к третьему выходу узла сброса и запуска, а третьи входы соединены с в ходом второго элемента ИЛИ, второй вход которого подключен к четвертому выходу узла сброса и запуска, выходы регистра памяти соединены с Iсоотвётствуящими входами дешифратора, выходы которого и четвертый вых узла сброса и запуска являются информационными выходами устройства На фиг. 1 представлена блок-схема устройства; на фиг. 2 - диаграмма работы устройства при исправном объекте контроля; на фиг. 3 - диаграмм а работы устройства при неисправном объекте контроля (обрыв в 3-м канале); на фиг. 4 - функциональная.схема узла сброса и запуска; на фиг. 5 функциональная схема счетчика импульсов . Блок-схема устройства (фиг.О «содержит генератор 1 тактовых импульсов, компаратор 2, первый вход которого соединен с выходом объекта 3 контроля, шифратор 4, три выхода которого соединены с соответствующими входами объекта 3 контроля, сумматор 5 по модулю два, первый элемент И 6, при ;этом первьй выход генератора 1 импульсов такта соединен с первыми входами элемента И 6 и сумматора 5 по модулю два, реверсивный распределитель 7, первые шесть выходов которого соединены с шесТью входами шифратора, узел 8 сброса и запука, первые два входа 9 И 10 которого являются управляющими, третий соединен с вторым выходом генератора 1 импульсов такта, а четвертый и пятый соединены соответственно с вторым и седьмым выходами распределителя;, счетчик 11 импульсов, первый вход которого соединен с выходом сумматора 5 по модулю два и первым входом распределителя 7, а выход с шестым входом узла 8 сброса и запуска, элементы И 12, ИЛИ 13 и 14, регистр 16 памяти и дешифратор 17, при этом первый вход второго эле- мента И соединен с третьим выходом генератора 1 импульсов такта и вторым входом счетчика импульсов, второй вход - с седьмым выходом распределителя, выход - с вторым входом компаратора, выход которого соедине t первым входом первого элемента ИЛИ 13, второй вход - с выходом . . fсчетчика 11, а выход - с вторым вхо.г; дом первого элемента И 6, выход которого соединен с вторыми входами реверсивного распределителя 7 и сумматора 5 по модулю два, при этом выход узла 8 сброса и запуска соединен с первым входом генератора импульсов такта, второй выход узла В сброса и запуска - с третьим входом распределителя и первым входом вто- , рого элемента ИЛИ 14, первые шесть выходов реверсивного распределителя 7 соединены с соответствующими входами триггеров 15,- ISg, регистра 16 памяти, вторые входы - с третьим выходом узла 8 сброса и запуска, третьи входы ячеек памяти - с выходом второго элемента ИЛИ 14, второй вход которого соединен с четвертым выходом узла 8 сброса и запуска, выходы ячеек памяти соединены с соответствующими входами дешифратора 17,выходы 18 которого и четвертый выход 19 узла 8 сброса и запуска являются информационными выходами устройства.: Узел 8 сброса и запуска содер.жит (фиг. 4) элементы ИЛИ 20-23, элеме.нты И 24-27, элементы И-НЕ 28 29/ триггеры 30-34, построенные на элементах 2Й-2Ш1И 35 и входы 36-41 выходы .42-45. Счетчик 11 содержит (фиг. 5) JK-триггеры 46 и 47, элемент И 48, входы 49 и 50 и выход 51. Компаратор 2 служит для сравнения контрольной и контролируемой по , ледовательностей и при совпадении к дов формирует на выходе 1, а при несовпадении - О. Шифратор 4 слузкит для формирования контрольного теста из последова тельностей импульсов, поступающих на его вход. Сумматор 5 по модулю два служит для вырабатывания сигналов, управляющих реверс,ы распределителя 7. Ес на обоих входах сумматора присутств ют одинаковые потенциалы на выходе сумматора, сигнал отсутствует, прои ходит управление распределителем по ,суммирзтощему входу. Если один из сигналов на выходе сумматора отсутс вует, на выходе появляется сигнал, угфавляющий вычитающим входом распр делителя. Узел 8 сброса и запуска предназначен .для формирования сигналов уп равляющих работой регистра 15 распр делителя 7. Счетчик 11 (фиг. 5)j вьтолненны на ЛС-триггерах 46 k 47, имеет коэф фициент пересчета, равный трем, и служит для формирования импульса проталкивания. 1 мпульс с последнего разряда счетчика поступает на первь вход элемента И 48, на второй вход импульсы ТИЗ с генератора 1. 3 Элемент И12 предназначен для формирования контрольного теста, совпадающего с правильной работой объекта контроля, учитывающего отсутствие высокого потенциала на седьмом такте работы устройства. Это осуществляется путем умножения инвертированной последовательности импульсов ТИЗ и выхода седьмого канала реверсивного распределителя. Регистр 15 предназначен для запоминания информации о месте нахождения неисправностей в каналах. Устройство работает следующим образом. Приведение устройства в исходное состояние осуществляется подачей команды Исходное. Устройство запускается подачей команды Запуск. По заднему фронту команды (фиг.2) генератор 1 начинает вьщавать последовательности импульсов ТИ1, ТИ2 и ТИЗ. После приведения в исходное состояние распределитель 7 находится на седьмом (исходном) шаге (фиг. 2), на котором с объекта 3 на компаратор 2 подается низкий потенциал (все три . канала обесточены)..На второй вход компаратора 2 также подается Низкий потенциал. Высокий потенциал с выхода компаратора 2 через элемент ИЛИ 13 /поступает на один- из входов элемента Иб.При совпадении высоких потенциалов во время прохождения нулевого тактового импульса последовательности ТИ2 элемент И6 открывается, и сигт нал управления поступает на суммирующий вход распределителя 7, подготавливая включение первого канала. Первый тактовьй импульс через элемент Иб поступает на распределитель 7, -с первого канала которого шифратором 4 формируется первый такт тестового набора - включается первый канал мажоритарной схемы объекта 3. При правильной.работе схема не выдает сигнал, и компаратор 2 подтверждает открытое состояние элемента И6, сумматор 5 закрыт, так как на его обоих входах присутствуют одинаковые потенциалы как с генератора 1, так и с элемента И6. Во время действия второго тактового импульса шифратором 4 формируется второй такт теста, при котором, включаются первьй и второй каналы мажоритарной схемы объекта 3. При этом на ее входе появляется сигнал, и компаратор 2 во действия второго тактового ийпульса частоты ТИ2 поддерживает элемент Й6 в откры том состоянии. Аналогично формирзгются последующие такты тестового набора, причем на третьем такте включается второй канал мажоритарной схемы объекта 3 (соответствует 0 контролируемой последовательности), на четвертом такте - втброй и третий каналы (1 контролируемой последовательности), на пятомтакте - третий канал (О) на шестом такте - первыйи третий кан лы (1) ,на седьмом такте снимается си нал с входов мажо15итарной схемы 3 () формируется сигнал Конец проверки на выходе 18, и узел 8 вырабатывает сигнал 09, ПО заднему фронту которого генератор 1 прекращает генерировать тактовые импульсы. При неисправности мажоритарной схеме устройство работает следующим образом. Предположим, например, что имеется неисправность типа обрыв в третьем канале схемы объекта 3. На четвертом тактовом импудьсе шифратор 4 подает команды на включение второго и третьего каналов мажоритарной схемы 3., а сигнал на ее выходе отсутствует. На выхбде ко паратора 2 сигнал отсутствует и элемент И6 закрыт. Сумматор 5 выдает сигнал на вычитающий вход распределителя 7 и счетчик 11. Распределитель 7 подготйвится к переключению на свой третий канал. По истечении четвертого тактового импульса пятым тактовым импульсом шифратор 4 включает втор канал мажоритарной схеьвл объекта 3.. компаратор 2 открывает элемент Иб,. сумматор 5 закрывается,и счетчик t запоминает один импульс. Далее объект работает как на третьем такте нормальной работы. По приходу ше того тактового импульса картина вновь повторяется, и счётчик 11 сосчитает еще .один импульс. При трехкратном повторении процесса импульс с -последнего разряда счетчика 11 поступает на шестой вхо узла 8. С шестого входа (фиг. 4) сигнал через элемент ИЛИ 14 поступает на , 6 вход iiS -триггера 15 . По истечении двух тактовых импульсов частоты ТИ1 на третьем выходе (фиг. 4) узла 8 сформируется сигналQ 10, который поступает на .5 -входы триггеров 15 регистра памяти, на вторые ,Э -входы которых подаются сигналы с соответствующих каналов распределителя 7. В данном конкретном случае запись сигнала разрешается в триггер 15 (4-й канал распределителя). В это же время с выхода счетчика 11 через элемент 13 на второй вход элемента И6 (фиг, 3) подается импульс, который позволяет протолкнуть распределитель 7 с четвертого каналана пятый. Сброса при этом не происходит, так как он формируется только на 7-м шаге распределителя . 7 с четвертого выхода узла 8. Поскольку по условию в 3-м канале мажоритарной схемы обрыв, то неисправность не обнаруживается, и распределитель 7 переключается на шестой канал. В связи с тем, что мажоритарная схема объекта 3 -должна выдать высокий потенциал, а она его не выдает, то распределитель 7 возвращается на пятый канал,-затем опять на шестой и т.д. После трехкратного повторения процесса 1 записывается в триггер 15g регистра. При этом на первом снизу выходе дешифратора 17 появляется сигнал, означающий, что в 3-м канале проверяемого устройства имеется неисправность типа обрыв. R5 -триггер 34 служит для формирования сигнала Q 8, блокирующего выключение триггеров на седьмом шаге распределителя 7 сразу после подачи сигнала Запуск. Это необходимо для того, чтобы генератор не вьпслючался сразупосле включения при неисправности типа к.з. в первом канале. Сигнал Конец проверки формируется следующим образом. На 14-м такте частоты ТИ2, так Ьке как и на 8-м, Iiмпyльc проталкивания открьгоает элемент И6, и распреелитель 7 переключается на 7-й канал. На пятом входе узла 8 появляется сигнал, который очередной раз формирует сигнал QlO. При этом по S -входам триггеры 15,- 15 не срабатывают (так как распределитель 7 находится на седьмом такте). Сигнал W 10 подается на К -вход К5-тригге9111

pa 32, предяазначенного для формировав ния сигнала 0. 9, управляющего включением и выключением ключа генератора t. Этот триггер находится в единичном состоянии (Q.9-1) с момента подачи команды Запуск на вход 37 узла 8. Но истечении двух тактовых ИмпульсЬ частоты ТИ1 переходит в нулевое состояние, включает ключ генератора 1, прекратившего генерировать . ,

7643 0

В этот момент заканчивается формирование сигнала Конец проверки, и триггеры 15, - 15« приводятся в исходное состояние через элемент ИЛИ 14, 5 Таким образом, схема готова к очередному циклу проверок.

Основным технико-экономическим преимуществом предлагаемого изобретения является сокращение трудозатtO рат на поиск неисправности в проверяемой аппаратуре.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля мажоритарных схем | 1977 |

|

SU705451A1 |

| Устройство для контроля мажоритарных блоков | 1981 |

|

SU1015389A1 |

| СИСТЕМА СВЯЗИ | 2003 |

|

RU2249914C2 |

| Устройство для обнаружения кратных дефектов в группе типовых элементов замены | 1983 |

|

SU1126966A1 |

| Устройство для контроля многовыходных цифровых узлов | 1984 |

|

SU1176333A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для поиска кратных дефектов в группе объектов | 1983 |

|

SU1233157A1 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

| Устройство аналого-цифрового преобразования | 1982 |

|

SU1045378A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1343551A1 |

Itcjre Hoe Запуск ТИ1 Т ft2 0 ход 2 ком n. Вход 1 комп. Выжод KoMri, ВшодСКМб

n

rL

Фиг. г лпшшшишлллллпги JTJTJTJnjnJTJTJnriirrLTLrLTLJlо 12 J 4 5 6 7

: LJirinnmirijm/Lfu «L-jViAAAAAAAAAAAn

J-L

tf/

Q3

Of

Q5

QB

07 I Ч Вых ком п. Выя (XMS «МвшЮ1 я л..л fftiff. сумг аторй

йг / п л

Фи.

Фаг.З

SO

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для ПРОВЕРКИ ФУНКЦИОНИРОВАНИЯ ЛОГИЧЕСКИХ СХЕМ | 0 |

|

SU354415A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-10-07—Публикация

1983-06-15—Подача