(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПОЗИЦИОННЫХ ПРИЗНАКОВ НЕПОЗИЦИОННОГО КОДА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования позиционных признаков непозиционного кода | 1980 |

|

SU898418A1 |

| Устройство для формирования позиционных характеристик непозиционного кода | 1981 |

|

SU968802A1 |

| Устройство для сложения по модулю | 1982 |

|

SU1064278A1 |

| Устройство для определения позиционных признаков непозиционного кода | 1983 |

|

SU1142827A1 |

| Устройство для преобразования непозиционного кода в позиционный код | 1987 |

|

SU1510097A1 |

| Преобразователь непозиционного кода в позиционный код | 1984 |

|

SU1481895A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Устройство для формирования позиционных признаков непозиционного кода | 1981 |

|

SU1007098A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ S-ИЧНЫХ ЦИФР В ПОЗИЦИОННО-ОСТАТОЧНОЙ СИСТЕМЕ СЧИСЛЕНИЯ | 1991 |

|

RU2006919C1 |

| Преобразователь двоичного кода в код системы остаточных классов | 1980 |

|

SU959062A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в выЧислительных устройствах, работающих с двухступенчатыми непозиционными кодами.

Известен преобразователь кодов, содержащий счетчики, генератор, вентильные схемы I.

Наиболее близким по технической сущности к предлагаемому является устройство для формирования позиционных признаков непозиционного кода, содержащее регистры, подключенные ко входам блока хранения констант, выходной сумматор, соединенный с выходными регистрами и со схемой анализа содержимого старщих разрядов, сумматор ранга числа, последовательно соединенные двоичные сумматоры, дополнительный двоичный сумматор, схему выработки признака знака 2.3

Недостатками известных устройств являются низкое быстродействие и структурная сложность.

Цель изобретения- повышение быстродействия и упрощение устройства.

Эта цель достигается тем, что устройство для формирования позиционных признаков

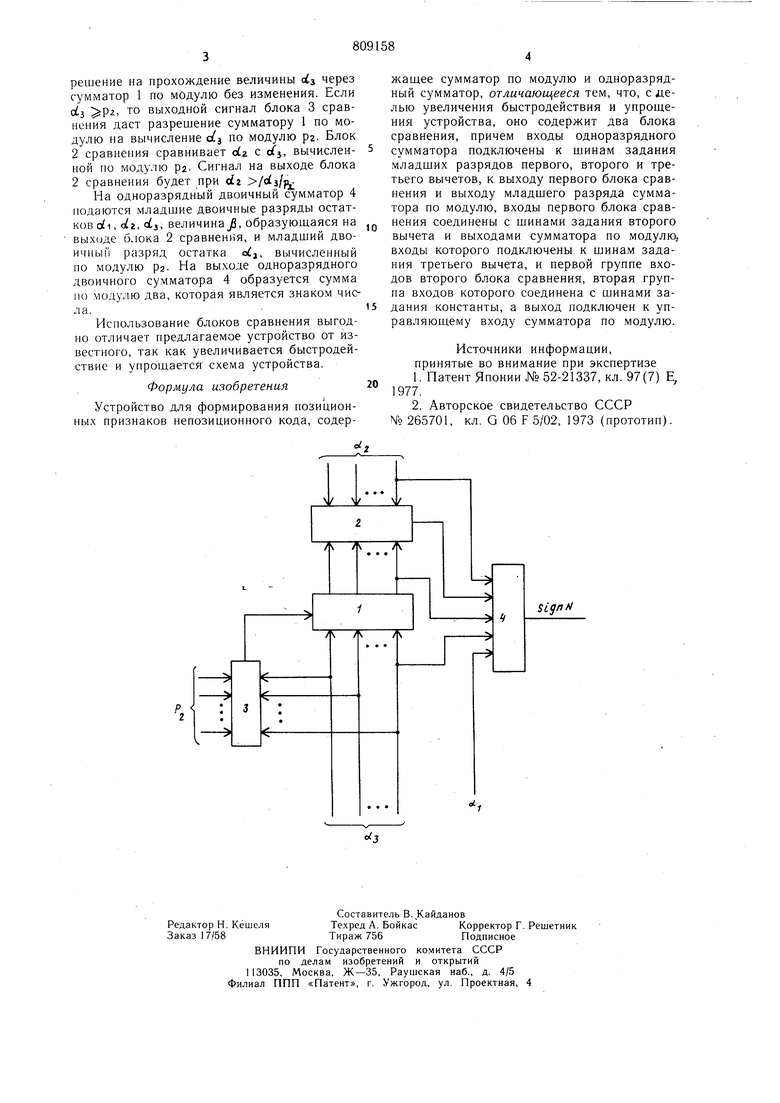

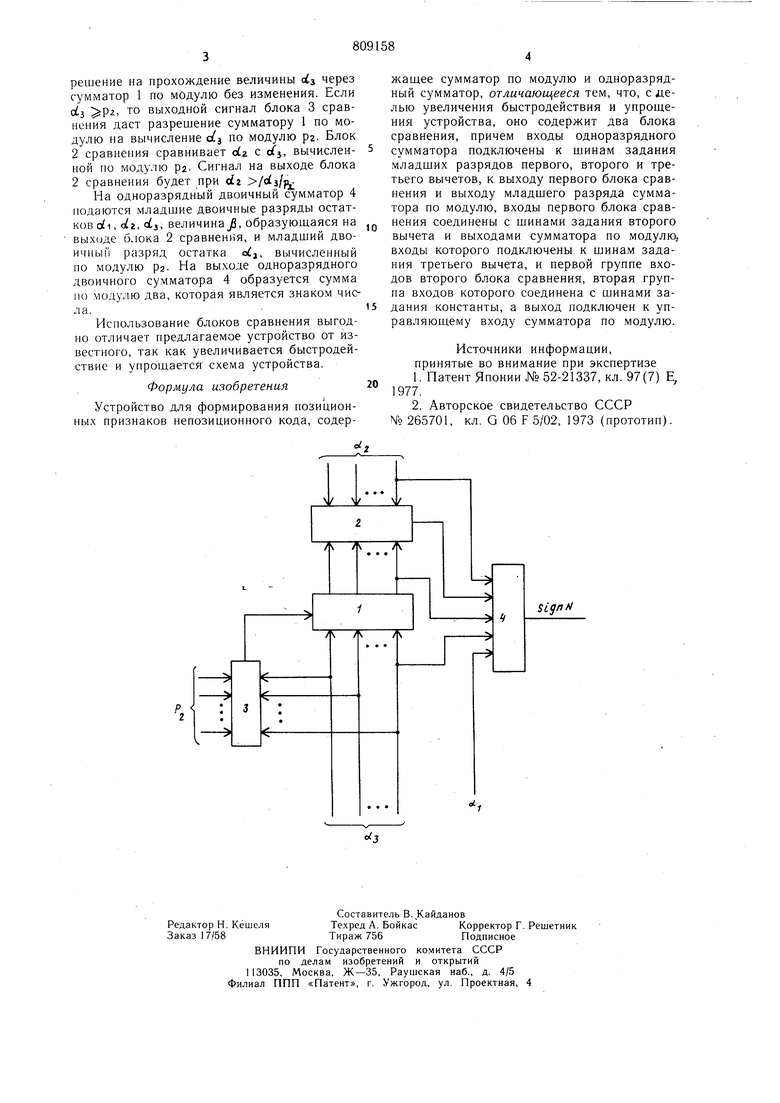

непозиционного кода, содержащее сумматор по модулю и одноразрядный сумматор, содержит два блока сравнения, причем входы одноразрядного сумматора подключены к щинам задания младщих разрядов первого, второго и третьего вычетов, к выходу первого блока сравнения и выходу младщего разряда сумматора по модулю, входы первого блока сравнения соединены с шинами задания второго вычета и выходами сумматора по модулю, входы которого подключены к финам задания третьего вычета, и первой группе входов второго блока сравнения, вторая группа входов которого соединена с шинами задания константы, а выход подключен к управляющему входу сумматора по модулю.

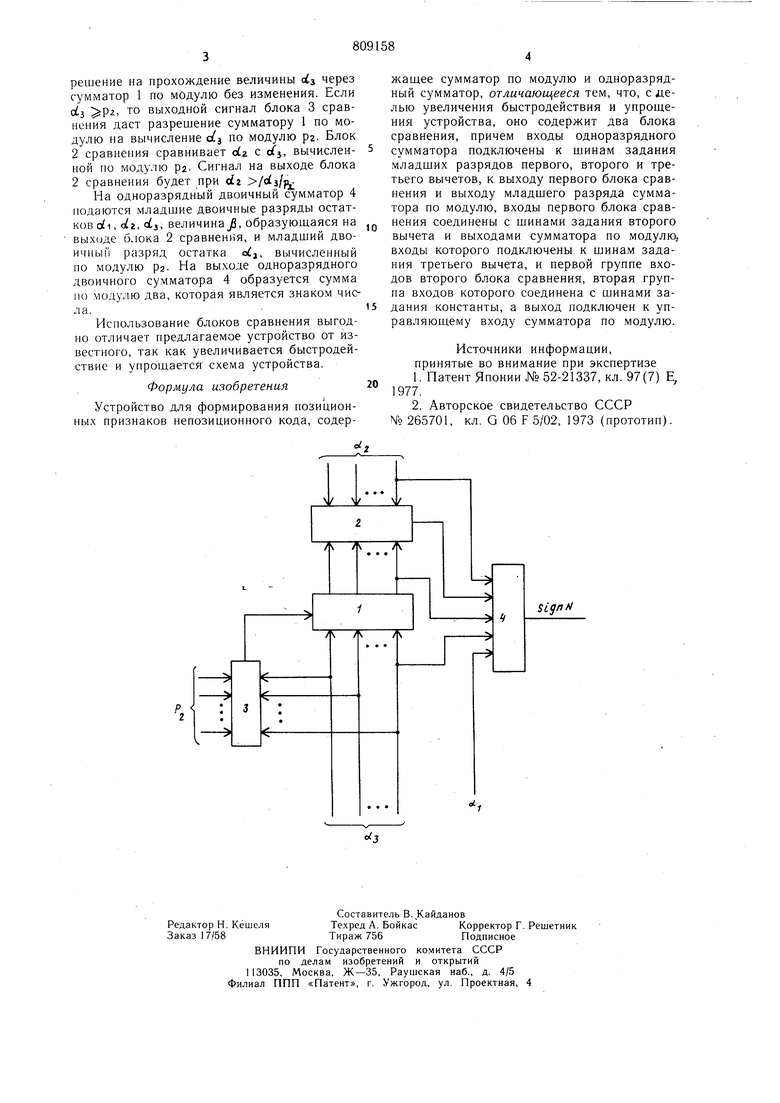

На чертеже приведена блок-схема устройства.

Устройство содержит сумматор 1 по модулю, блоки 2 и 3 сравнения, одйоразрядный двоичный сумматор 4.

Устройство работает следующим образом.

Остаток сравнивается с константой рг на блоке 3 сравнения. Если d рг, то выходной сигнал.блока 3 сравнения даст разрешение на прохождение величины через сумматор 1 по модулю без изменения. Если выходной сигнал блока 3 сравнения даст разрешение сумматору 1 по модулю на вычисление по модулю рг. Блок 2 сравнения сравнивает dz с оГз вычисленной но модулю р2. Сигнал на выходе блока 2 сравнения будет при dz ilf На одноразрядный двоичный сумматор 4 нодаются младшие двоичные разряды остатков d, , оСз, величина j8, образующаяся на выx(Jдe блока 2 сравнения, и младший двоичный разряд остатка oij, вычисленный по модулю Ра. На выходе одноразрядного двоичного сумматора 4 образуется сумма по модулю два, которая является знаком чисИспользование блоков сравнения выгодно отличает предлагаемое устройство от известного, так как увеличивается быстродействие и упрощается схема устройства. Формула изобретения Устройство для формирования позиционных признаков непозиционного кода, содер1 ) 1

/IN 1 1 жащее сумматор по модулю и одноразрядный сумматор, отличающееся тем, что, с делью увеличения быстродействия и упрощения устройства, оно содержит два блока сравнения, причем входы одноразрядного сумматора подключены к шинам задания младших разрядов первого, второго и третьего вычетов, к выходу первого блока сравнения и выходу младшего разряда сумматора по модулю, входы первого блока сравнения соединены с щинами задания второго вычета и выходами сумматора по модулю, входы которого подключены к шинам задания третьего вычета, и первой группе входов второго блока сравнения, вторая группа входов которого соединена с шинами задания константы, а выход подключен к управляющему входу сумматора по модулю. Источники информации, принятые во внимание при экспертизе 1.Патент Японии №52-21337, кл.97(7) Е 1977. 2.Авторское свидетельство СССР Nfo 265701, кл. G 06 F 5/02, 1973 (прототип).

Авторы

Даты

1981-02-28—Публикация

1979-06-14—Подача