Изобретение откосится к вычислительной технике и может быть хлсполь зовано при построении быстродействующих вычислительных устройств.

Целью изобретения является повы- шение быстродействия.

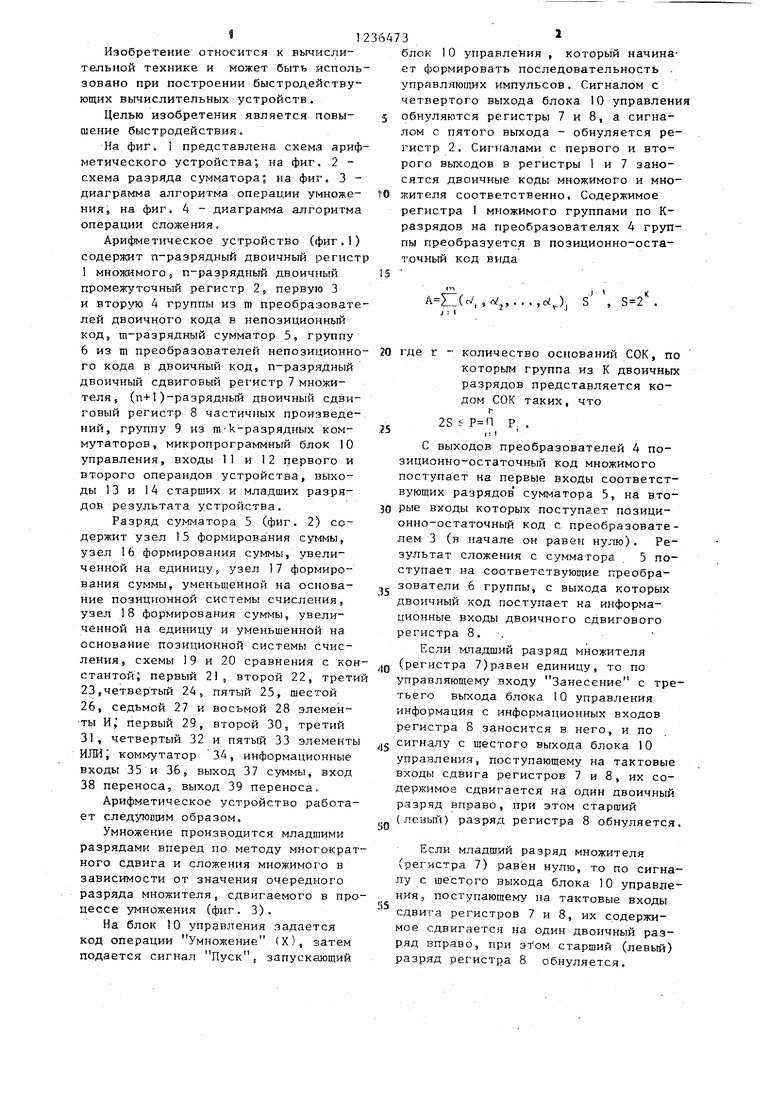

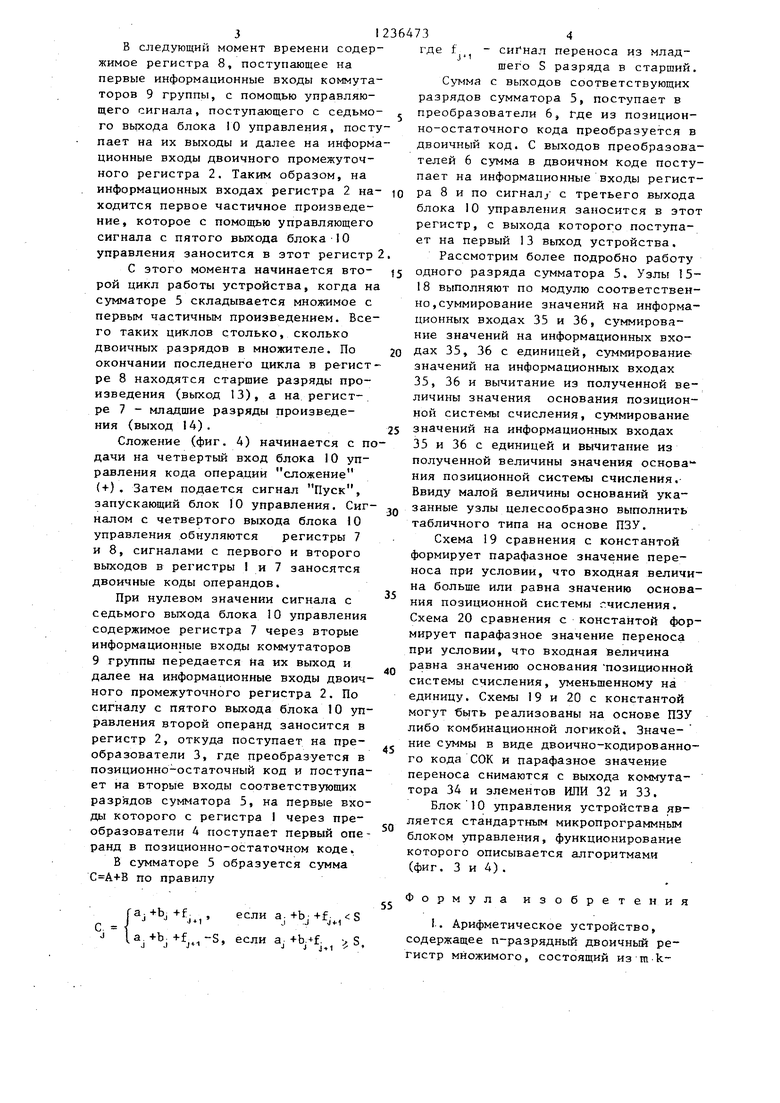

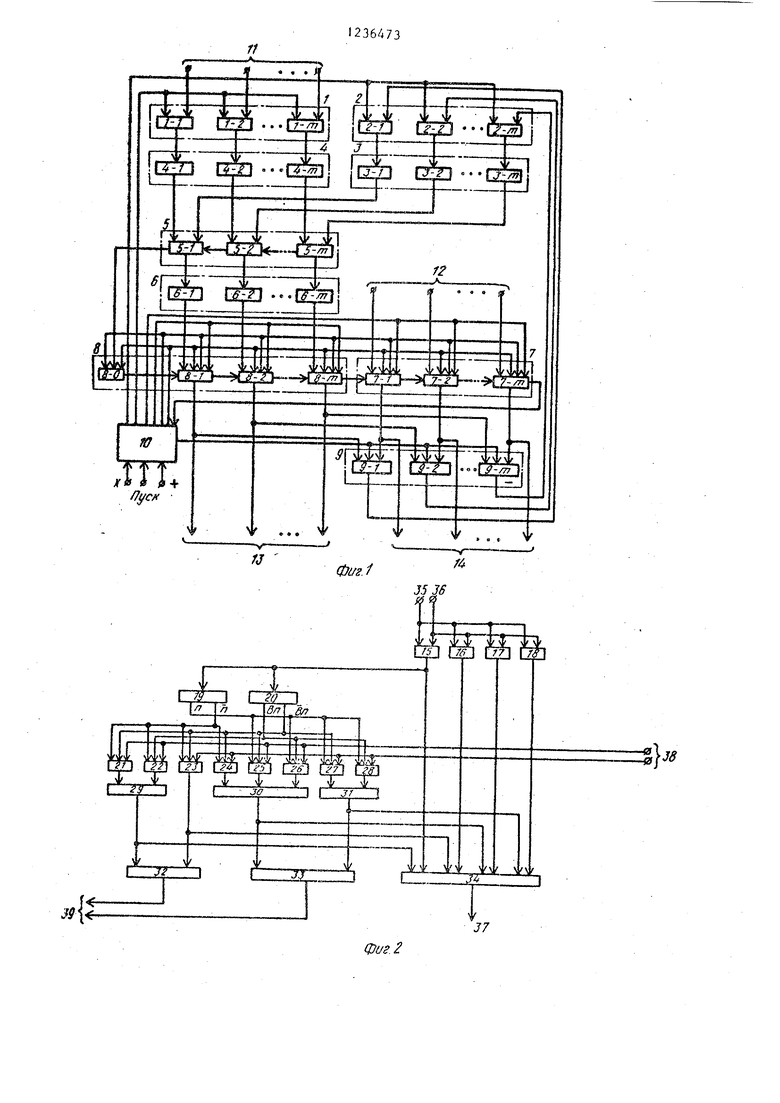

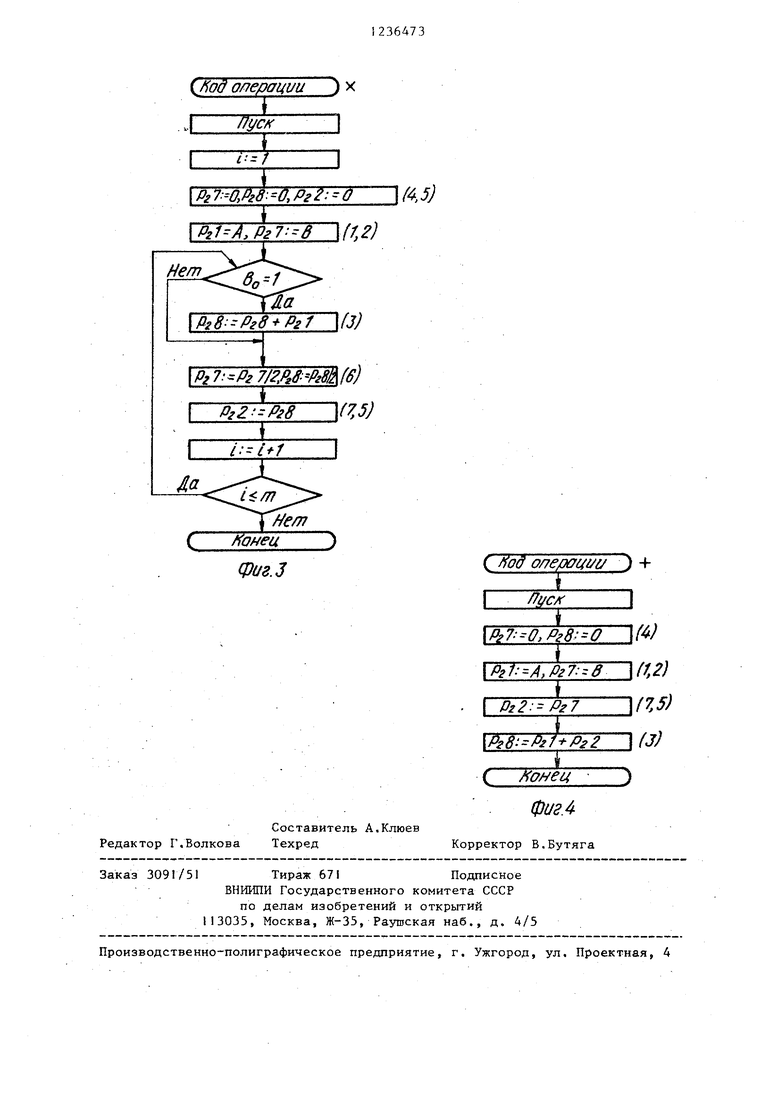

На фиг. 1 представлена схема арифметического устройства; на. фиг. 2 - схема разряда сумматора; на фиг. 3 - диаграмма алгоритма операции умноже- ния, на фиг, 4 - диаграмма алгоритма операции сложения.

Арифметическое устройство (фиг.1) содержит п-разрядный двоичный регист 1 множимого, п-разрядный двоичный промежуточный регистр 2f первую 3 и BTopiTo 4 группы из m преобразователей двоичного кода в непозициоиньй код, т-разрядный сумматор 5, группу 6 из m преобразователей непозиционного кода в двоичный код, п- разряДный двоичный сдвиговый регистр 7 множителя , (п+1)-разрядный двоичный сдвиговый регистр 8 частичных произведений, группу 9 из т-k-разрядных коммутаторов, микропрограммный блок 0 управления, входы 11 и 2 первого и второго операндов устройства, выходы 13 и 14 старших и младших разрядов результата устройства.

Разряд сумматора 5 (фиг. 2) содержит узел 15 формирования су1-{мы узел 16 формирования суммы, увеличенной на единицу 5 узел 17 формирования суммы, уменьшенной на основание позиционной системы счисления, узел 18 формирования суммы, увеличенной на единицу и уменьшенной на основание позиционной системы счисления, схемы 19 и 20 сравнения с константой; первый 2, второй 22, трети 23,четвертый 24, пятый 25, шестой 26, седьмой 27 и восьмой 28 элемен- ты И, первый 29, второй 30, третий 31, четвертый 32 и пятый 33 элементы ИШ коммутатор ЗА, информационные входы 35 и 36, выход 37 суммы, вход 38 переноса, выход 39 переноса.

Арифметическое устройство работает следуювоим образом.

Умножение производится младшими разрядами вперед по методу многократного сдвига и сложения множимого в зависимости от значения очередного разряда множителя 5 сдвигаемого в процессе умножения (фиг. 3).

На блок 0 управления задается код операции Умножение (Х), затем подается сигнал Пуск запускающий

блок 10 управления , который начинает формировать последовательность . управляющих импульсов. Сигналом с четвертого выхода блока 10 управления обнуляются регистры 7 и 8, а сигналом с пятого выхода - обнуляется регистр 2. Сигналами с первого и второго выходов в регистры 1 и 7 заносятся двоичные коды множимого и мно- жит€ .ля соответственно. Содержимое регистра i множимого группами по К- разрядов на преобразователях 4 группы преобразуется в позиционно-оста- точный код вида

(сУ, ,У,...,Ы), S

20 где г - количество оснований СОК, по которым группа из К двоичных разрядов представляется кодом СОК таких, что

h

, 2S J Р. .

| 1

С выходов преобразователей 4 по- зиционно-остаточный код множимого поступает на первые входы соответствующих разрядов сумматора 5, на вто30 Рые входы которых поступает позици- онно-остаточный код с преобразователем 3 (в начале он равен нулю). Результат сложения с сумматора 5 поступает на соответствующие преобразователи 6 группы, с выхода которых двоичный код поступает на информационные входы двоичного сдвигового регистра 8. .

Если младший разряд множителя (регистра 7)равен единицу, то по управляющему входу Занесение с третьего выхода блока 10 управления информация с информационных входов регистра 8 заносится в него, и по

J5 сигналу с шестого выхода блока 10 управления, поступающему на тактовые входы сдвига регистров 7 и 8, их содержимое сдвигается на один двоичный разряд вправо, при этом старший (леньш) разряд регистра 8 обнуляется

35

40

ЙО

S5

Если младший разряд множителя (регистра 7) равен нулю, то по сигналу с шестого выхода блока 10 управления, поступающему на тактовые входы сдвига регистров 7 и 8, их содержимое сдвигается на один двоичный разряд вправо, при 3toM старший (левый) разряд регистра 8 обнуляется.

В следующий момент времени содержимое регистра 8, поступающее на первые информационные входы коммутаторов 9 группы, с помощью управляющего сигнала, поступающего с седьмого вькода блока ГО управления, постпает на их выходы и далее на информционные входы двоичного промежуточного регистра 2. Таким образом, на информационных входах регистра 2 находится первое частичное произведение, которое с помощью управляющего сигнала с пятого выхода блока 10 управления заносится в этот регистр

С этого момента начинается второй цикл работы устройства, когда н сумматоре 5 складывается множимое с первым частичным произведением. Всего таких циклов столько, сколько двоичных разрядов в множителе. По окончании последнего цикла в ре-гист ре 8 находятся старшие разряды произведения (выход 13), а на регист-. ре 7 - младшие разряды произведения (выход 14).

Сложение (фиг. 4) начинается с пдачи на четвертый вход блока 10 управления кода операции сложение (+). Затем подается сигнал Пуск, запускающий блок 10 управления. Сигналом с четвертого выхода блока 10 управления обнуляются регистры 7 и 8, сигналами с первого и второго выходов в регистры I и 7 заносятся двоичные коды операндов.

При нулевом значении сигнала с седьмого выхода блока 10 управления содержимое регистра 7 через вторые информационные входы коммутаторов 9 группы передается На их выход и далее на информационные входы двоичного промежуточного регистра 2. По сигналу с пятого выхода блока 10 управления второй операнд заносится в регистр 2, откуда поступает на преобразователи 3, где преобразуется в позиционно-остаточный код и поступает на вторые входы соответствующих разрядов сумматора 5, на первые входы которого с регистра I через преобразователи 4 поступает первый операнд в позиционно-остаточном коде.

В сумматоре 5 образуется сумма по правилу

С.

.M и 3j bj- f..

л .- b/f,,, .

0

s

0

5

0

5

5

0

где f - сигнал переноса из младшего S разряда в старший.

Сумма с выходов соответствующих разрядов сумматора 5, поступает в преобразователи 6, Где из позицион- но-остаточного кода преобразуется в двоичный код. С выходов преобразователей 6 сумма в двоичном коде поступает на информационные входы регистра 8 и по сигнал с третьего выхода блока 10 управления заносится в этот регистр, с выхода которого поступает на первый 13 выход устройства.

Рассмотрим более подробно работу одного разряда сумматора 5. Узлы 15- 18 выполняют по модулю соответственно , суммирование значений на информационных входах 35 и 36, суммирование значений на информационных входах 35, 36 с единицей, суммирование значений на информационных входах 35, 36 и вычитание из полученной величины значения основания позиционной системы счисления, суммирование значений на информационных входах 35 и 36 с единицей и вычитание из полученной величины значения основания позиционной системы счисления.- Ввиду малой величины оснований указанные узлы целесообразно выполнить табличного типа на основе ПЗУ.

Схема 19 сравнения с константой формирует парафазное значение переноса при условии, что входная величина больше или равна значению основания позиционной системы с-числения. Схема 20 сравнения с константой формирует парафазное значение переноса при условии, что входная величина равна значению основания позиционной системы счисления, уменьшенному на единицу. Схемы 19 и 20 с константой могут быть реализованы на основе ПЗУ либо комбинационной логикой. Значение суммы в виде двоично-кодированного кода СОК и парафазное значение переноса снимаются с выхода коммутатора 34 и элементов ИЛИ 32 и 33.

Блок 10 управления устройства является стандартным микропрограммным блоком управления, функционирование которого описывается алгоритмами (фиг. 3 и 4).

Формула изобретения

. Арифметическое устройство, содержащее п-разрядный двоичный регистр множимого, состоящий из m-kразрядных групп (), n-разрядный двоичный сдвиговый регистр множителя, состоящий из m k-разрядных групп п-разрядный двоичный промежуточный регистр, состоящий из m-k-разрядных групп, (п+1)-разрядный двоичный сдвиговый регистр частичных произведений, состоящий из m k-разрядньгх групп, щ-разрядный сумматор и микропрограммный блок управления, причем выходы п младших разрядов и выход младшего разряда (п+1)-разрядного двоичного сдвигового регистра частичных произведений соответственно являются выходом старших разрядов результата устройства и подключены к сдвиговому входу старшего разряда п-разрядного двоичного сдвигового регистра множителя, входы первого и второго операндов устройства соединены соответственно с информационными входами п-разрядных двоичных регистров множимого и сдвигового регистра множителя, выходы которого являются выходом младших разрядов результата устройства, выход младшего разряда п-разрядного двоичного регистра множителя подключен к первому входу микропрограммного блока управления, второй вход которого является входом Пуск устройства, третий вход блока управления является входом Умножение устройства, входы записи п-разрядньгх двоичных регистра множимого и сдвигового регистра множителя, а также п младших разрядов (n+l )-разрядно-го двоичного сдвигового регистра частичных произведений подключены соответственно к выходам первого, второго и третьего управляющих полей микропрограммного блока управления, входы обнуления п-разрядного двоичного регистра множителя и ( )-разрядного двоичного сдвигового регистра частичных произведений объединены и подключены к вьгходу четвертого управляющего поля микропрограммного блока управления, вход занесения п-разрядного двоичного промежуточного регистра подключен к выходу пятого уп равляющего поля микропрограммного блока управления, тактовые входы п- разрядного двоичного сдвигового регистра множителя и (п+1)-разрядного двоичного сдвигового регистра частиных произведений объединены и подключены к выходу шестого управляю0

5

0

5

0

5

0

5

5

щего поля блока микропрограммного управления, выход переноса р-го разряда сумматора соединен с входом переноса (p-l)-ro () разряда сумматора, выход переноса старшего разряда сумматора подключен к информационному входу старшего разряда (п+1)-разрядного двоичного сдвигового регистра частичных произведений, отличающееся тем, что, с целью повышения быстродействия, оно содержит первую и вторую группы из га преобразователей двоичного кода в непозиционный код, группу из m преобразователей непозиционного кода в двоичный код, группу из mk-раз- рядных коммутаторов, группа выходов которых подключена соответственно к группе информационных входов п-разрядного двоичного промежуточного регистра, группа выходов которого подключена соответственно к группе входов преобразователей двоичного кода в непозиционный код первой группы, группа выходов п-разрядного двоичного регистра множимого подключена к группе входов преобразователей двоичного кода в непозиционный код второй группы, выходы которых подключены к первым информационным входам соответствующих разрядов га-разрядного сумматора, вторые информационные входы которых подключены к выходам соответствующих преобразователей двоичного кода в непозиционный код первой группы, выходы разрядов п- разрядного сумматора подключены ,к входам соответствуюших преобразователей непозиционного кода в двоичный код группы, выходы которых подключены к информационньи входам соответствующих групп (п+1)-разрядного двоичного сдвигового регистра частичных произведений, кроме нулевого разряда, группа выходов которого подключена соответственно к первой группе информационных входов коммутаторов группы, вторая группа информационных входов которых подключена соответст-, венно к группе выходов п-разрядного двоичного сдвигового регистра множителя, управляющие входы .коммутаторов группы соединеньгс выходом седьмого уп-- равляющего полямикропрограмного блока управления,четвертый входкоторого является входом Сложение устройства.

2. Устройство по п. 1, отличающееся тем, что разряд т7

разрядного сумматора содержит узлы формирования суммы, суммы,увеличенной на единицу, суммы, уменьшенной на основание позиционной системы счисления, суммы, увеличенной на единицу и уменьшенной на основание позиционной системы счисления, две схемы сравнения с константой, восемь элементов И, пять элементов ИЛИ и коммутатор, причем выход коммутатора является выходом разряда га-раз- рядного сумматора, информационные входы которого подключены к соответствующим входам узлов формирования суммы, суммы, увеличенной на единицу, суммы, уменьшенной на основа - ние позиционной системы счисления, суммы, увеличенной на единицу и умен шеной на основание позиционной системы счисления, выходы которых соединены соответственно с первым, вторым третьим и четвертым информационными входами коммутатора, выход узла формирования суммы соединен с входами первой и второй схем сравнения с константой, инверсный выход первой схемы сравнения с константой соединен с первыми входами элементов И с первого по четвертый, прямой выход первой схемы сравнения с константой соединен с первыми входами элементов И с пятого по восьмой, вторые входы первого, третьего, четвертого, пятого и седьмого элементов И соединены с инверсным выходом второй ске 364738

мы сравнения с константой, прямой выход которой соединен с вторьгми входами второго, шестого и восьмого элементов И, третьи входы первого, , второго, пятого и шестого элементов И соединены с инверсным входом переноса разряда т-разрядного сумматора, прямой вход переноса которого соединен с третьими входами третьего,

0 четвертого, седьмого и восьмого элементов И, выходы первого и второго элементов И соединены через первый элемент ИЛИ с первым управляющим входом коммутатора, второй, третий

5 и четвертый управляющие входы которого соединены соответственно с выходами третьего элемента И, второго и третьего элементов ИЛИ, выходы четвертого, пятого и шестого элемен0 тов И соединены соответственно с

входами второго элемента ИЛИ, выходы седьмого и восьмого элементов И соединены соответственно с входами третьего элемента 1ШИ, выходы первого

5 элемента ИЛИ и третьего элемента И соединены соответственно с входами четвертого элемента ИЛИ, выход которого является инверсным выходом переноса разряда тп-разрядного сумматоQ ра, прямой выход переноса которого соединен с выходом пятого элемента ИЛИ,первый и второй входы которого соединены соответственно с выходами второго и третьего элемен- тов ИЛИ.

зд

37

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения чисел с плавающей запятой | 1985 |

|

SU1280624A1 |

| Устройство для умножения | 1989 |

|

SU1672441A1 |

| Вычислительное устройство | 1988 |

|

SU1532917A1 |

| Устройство для вычисления сумм произведений | 1982 |

|

SU1020818A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Устройство для умножения | 1990 |

|

SU1753471A1 |

| Устройство для умножения | 1989 |

|

SU1667061A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство для умножения | 1984 |

|

SU1226447A1 |

| Устройство для умножения | 1985 |

|

SU1305667A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих вычислительных устройств. Целью изобретения является повьше- ние быстродействия. Устройство содержит регистр множимого, промежуточный регистр, группы преобразователей двоичного кода в непозиционный код, сумматор, группу преобразователей непозиционного кода в двоичный код, сдвиговый регистр множителя, сдвиговый регистр частичных произведений, группу коммутаторов, блок управления и соответствующие связи. 1 з.п. ф-лы, 4 ил. ISD со Од со

| Арифметическое устройство по модулю | 1983 |

|

SU1120325A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Каган Б.М | |||

| Электронные вычнсли- тельные машины и системы | |||

| М.: Энергия, 1979, с | |||

| Мяльно-трепальный станок для обработки тресты лубовых растений | 1922 |

|

SU200A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-07—Публикация

1984-11-30—Подача