Изобретение относится к вычислительной технике и может быть использовано в запоминающих устройствах (ЗУ) на ферритовых сердечниках.

Известно устройство для выбора информации из блоков памяти с использованием трансформаторных ключей выборки, первичные обмотки которых для каждого адреса соединены в разрядах последовательно и подключены к общему ключу кода. Трансформаторныеключи позволяют снизить мощность, потребляемую запоминающим устройством, унифицирвать схемы ключей втекающего и вытекающего тока С 1.

Наиболее близким к изобретению техническим решением является устройство, в котором начала первичны обмоток трансформаторов ключей выборки в кшкдом из разрядов объединены и подключены к источнику питания, а концы подключены к ключам кода 2J.

Недостатком известных устройств является малое быстродействие, так как закрывание ключей выборки происходит медленно, только за счет тока намагничивания входного трансформатора.

Целью изобретения является повышение быстродействия устройства.

Поставленная цель достигаеРгся тем, что в устройство для выбора информации из блоков памяти, содержащее адресные ключи, токоэадающие элементы и группы управляющих ключей, каждый из которых содержит транзистор, база и эмиттер которого подключены к выводам вторичной обмотки соответствующего трансформатора, причтем одни из выводов первичных обмоток трансформаторов каждой группы соединены с выходом соответствующего адресного ключа, один из входов которого соединен о шиной нулевого потенциала, а другой является адресным входом устройства, другие выводы первичнь(х обмоток одноименных трансформаторов групп через соответствующие токозадающие элементы подключены к основной шине питания, введены управляющий ключ, элементы связи и группы нелинейных элементо причем одни из выводов нелинейных элементов кшкдой группы соединены с выводами первичных обмоток трансформаторов той же группы, а другие выводы - с шиной нулевого потенци.ала, выход управляющего ключа соединен с дополнительной шиной питания, один из входов является управляющим, а другой вход соедине с одними из выводов связи, другие выводы которых подк/шчя . ны к другим выводам первичных обмо

ток одноименных трансформаторов соответствующих групп.

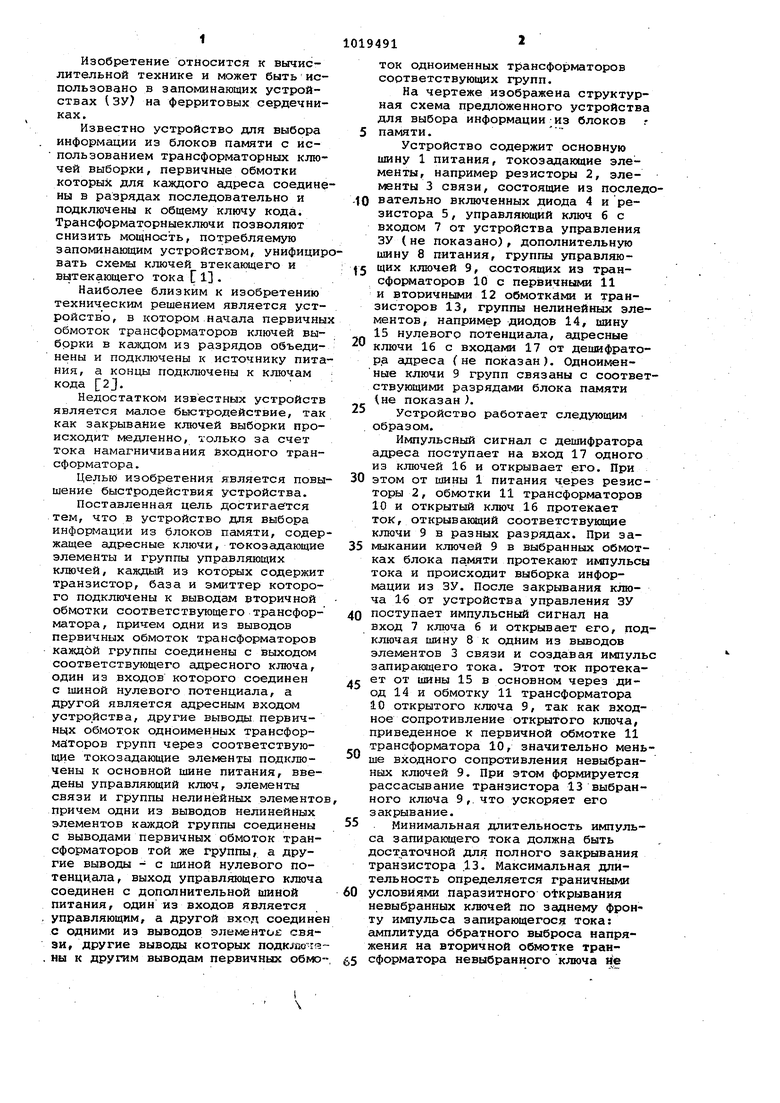

На чертеже изображена структурная схема предложенного устройства для выбора информации-из блоков памяти.

Устройство содержит основную шину 1 питания, токозадакхцие элементы, например резисторы 2, элементы 3 связи, состоящие из последвательно включенных диода 4 и резистора 5, управляющий ключ 6 с входом 7 от устройства управления ЗУ (не показано), дополнительную шину 8 питания, группы управляющих ключей 9, состоящих из трансфоЕФ«аторов 10 с первичными 11 и вторичными 12 обмотками и транзисторов 13, группы нелинейных элементов, например диодов 14, шину 15 нулевого потенциала, адресные ключи 16 с входами 17 от дешифратора адреса (не показан). Одноименные ключи 9 групп связаны с соответствующими разрядами блока памяти не показан ).

Устройство работает следующим образом.

Импульсный сигнал с дешифратора адреса поступает на вход 17 одного из ключей 16 и открывает его. При этом от шины 1 питания через реэисторы 2, обмотки 11 трансформаторов 10 и открытый ключ 16 протекает ток, открывающий соответствующие ключи 9 в разных разрядах. При замыкании ключей 9 в выбранных обмотках блока па.мяти протекают импульсы тока и происходит выборка информации из ЗУ. После закрывания ключа 1 от устройства управления ЗУ поступает импульсный сигнал на вход 7 ключа 6 и открывает его, подключая шину 8 к одним из выводов элементов 3 связи и создавая импуль запирающего тока. Этот ток протекает от шины 15 в основном через диод 14 и обмотку 11 трансформатора 10 открытого ключа 9, так как входное сопротивление открытого ключа, приведенное к первичной обмотке 11 трансформатора 10, значительно меньше входного сопротивления невыбранных ключей 9. При этом формируется рассасывание транзистора 13 выбранного ключа 9,. что ускоряет его закрывание.

Минимальная длительность импульса запирающего тока должна быть достаточной для полного закрывания транзистора .13. Максимальная длительность определяется граничными условиями паразитного о- крызаняя невыбранных кдночей по заднему фронту импульса запирающегося тока: амплитуда обратного выброса напряжения на вторичной обмотке трансформатора невыбранного ключа rig

должна превЕшать напряжения отпирания транзистора этрхчэ ключа.

В качестве управлйицего ключа б может быть использован, например, трансформаторнь клк)ч,подобный ключу 9.Ключи 16 представляют собой токовые iключи и могут быть шполнены,Например, fia микросхемах серии 169.

Наличие предлагаемой цепи активного рассасывания ключей 9 позволяет сократить время закрывания этих ключей и уменышть цКкл обращения в ЗУ. Ншример, время закрывания 5 трансформаторного ключа на трайзисторе КТ625АМ-2 сокращается в 5 раз (от 200 НС до 40 НС.

| название | год | авторы | номер документа |

|---|---|---|---|

| Трансформаторное постоянное запоминающее устройство | 1985 |

|

SU1352534A1 |

| Запоминающее устройство | 1979 |

|

SU809367A1 |

| Устройство для моделирования @ -фазного вентильного электродвигателя | 1990 |

|

SU1797133A1 |

| Адресный блок запоминающего устройства с линейной выборкой | 1984 |

|

SU1336098A1 |

| Формирователь тока выборки | 1977 |

|

SU710074A1 |

| МНОГОПОЗИЦИОННАЯ МАТРИЦА УПРАВЛЕНИЯ | 1972 |

|

SU337818A1 |

| Формирователь адресных токов | 1979 |

|

SU924752A1 |

| ИНВЕРТОР | 1994 |

|

RU2066513C1 |

| Импульсный стабилизатор переменного напряжения | 1983 |

|

SU1111139A1 |

| Трансформаторное постоянное запоминающее устройство | 1985 |

|

SU1310901A2 |

УСТРОЙСТВО ДЛЯ ВЫБОРА ИНФОРМАЦИИ ИЗ БЛОКОВ ПАМЯТИ, содержащее адресные КЛЮЧИ, токозадающие элемен1ы и группы управлякмцих ключей, каждый из которых содержит транзистор, база и эмиттер которого подключены к выводам вторичной обмотки соответствующего трансформатора/ причем один из выводов первичных обмоток трансформаторов каждой группы соединены с выходом соответствующего адресного ключа, один из входов которого соединен с шиной нулевого потенциала, а другой является адресным входом устройства, другие выводы первичных обмоток одноименных трансформаторов групп через соответствуквдие токозадающие элементы подклняены к основной шине питания, отличающееся тем, что, с целью повьвоения быстродействия устройства, в него введены управляющий ключ, элементы связи и группы нелинейных элементов, причём одни из выводов нелинейных элементов каждой группы соединены с выводами первичных обмоток тргшсформаторов той же группы, а другие выводы - с ШИНОЙ нулевого потенциала, выход управляклчего ключа сое. 9 динен с дополнительной шиной питания, один из входов является управляющим, а другой вход соединен с одними из выводов элементов связи, другке выводы которых подключены к другим выводам первичных обмоток § одноименных трансформаторов соответствующих групп. ф .

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающие устройства ЭЦВМ | |||

| Сб | |||

| под ред | |||

| А.А | |||

| Крупекого, Мир, 1968, с | |||

| Способ подготовки рафинадного сахара к высушиванию | 0 |

|

SU73A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для выборки информации из блоков памяти | 1975 |

|

SU532131A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1983-05-23—Публикация

1982-02-17—Подача