1

Изобретение относится к импульсной технике, в частности, к системам автоматического контроля и управления, в которых информация о контролируемом параметре представлена в частотной форме.

Известно устройство для контроля скорости изменения частоты, основанное на измерении и контроле разности двух интервалов времени, каждый из которых состоит из одного или нескольких периодов следования входных сигналов 1, содержащее формирователь входных импульсов, блок управления, состоящий из блока переключений, триггера, распределителя импульсов, шести элементов И и ИЛИ, источник эталонной частоты, счетчик, блок разности периодов, состоящий из блока элементов И и счетчика, элемент И и формирователь команды контроля.

Существенные недостатки этого устройства - значительная погрещность контроля скорости изменения частоты при работе его в щироком диапазоне частоты входных сигналов, и относительно низкое быстродействие, так как результат контроля формируется один раз за два периода входного сигнала.

Наиболее близким по технической сущности к данному изобретению является устройство 2, содержащее блок разности

периодов, представляющий собой реверсивный счетчик, дешифратор, блоки отключения и начальной установки, формирователь входных импульсов с фильтром низких частот, генератор эталонной частоты, блоки выходных реле и индикации, два блока управления, блоки подготовки повторного запуска, знака скорости и запрета, два элемента И и три элемента ИЛИ.

Существенные недостатки этого устройства - низкая точность контроля скорости изменения частоты при работе устройства в широком диапазоне входных сигналов и низкое быстродействие, что обусловлено большим циклом контроля скорости изменения частоты.

Целью данного изобретения является повышение быстродействия и точности контроля скорости изменения частоты при работе устройства в широком диапазоне частот входных сигналов.

Поставленная цель достигается тем, что в устройство, содержащее формирователь входных сигналов, выход которого соединей со входом блока управления, блок разности периодов, блок знака скорости, элемент И и источник эталонной частоты, введены счетчик импульсов, блок умножения, блок сравнения и шифратор, причем первый выход блока управления соединен с

первыми входами счетчика импульсов и блока разности периодов, второй выход блока управления соединен с первым входом элемента И, третий выход подключен к первому входу блока умножения и второму входу блока разности периодов, а четвертый выход подключен ко второму входу счетчика импульсов и через блок знака скорости - ко второму входу элемента И, третий вход блока разности периодов соединен с выходом счетчика импульсов и вторым входом блока умножения, четвертый вход блока разности периодов подключен к третьим входам счетчика импульсов и блока умножения и выходу источника эталонной частоты, первый выход блока разности периодов соединен со вторым входом блока знака скорости, второй выход соединен через блок сравнения с третьим входом элемента И, а выход шифратора подключен к четвертому входу блока умножения, выход которого соединен со вторым входом блока сравнения.

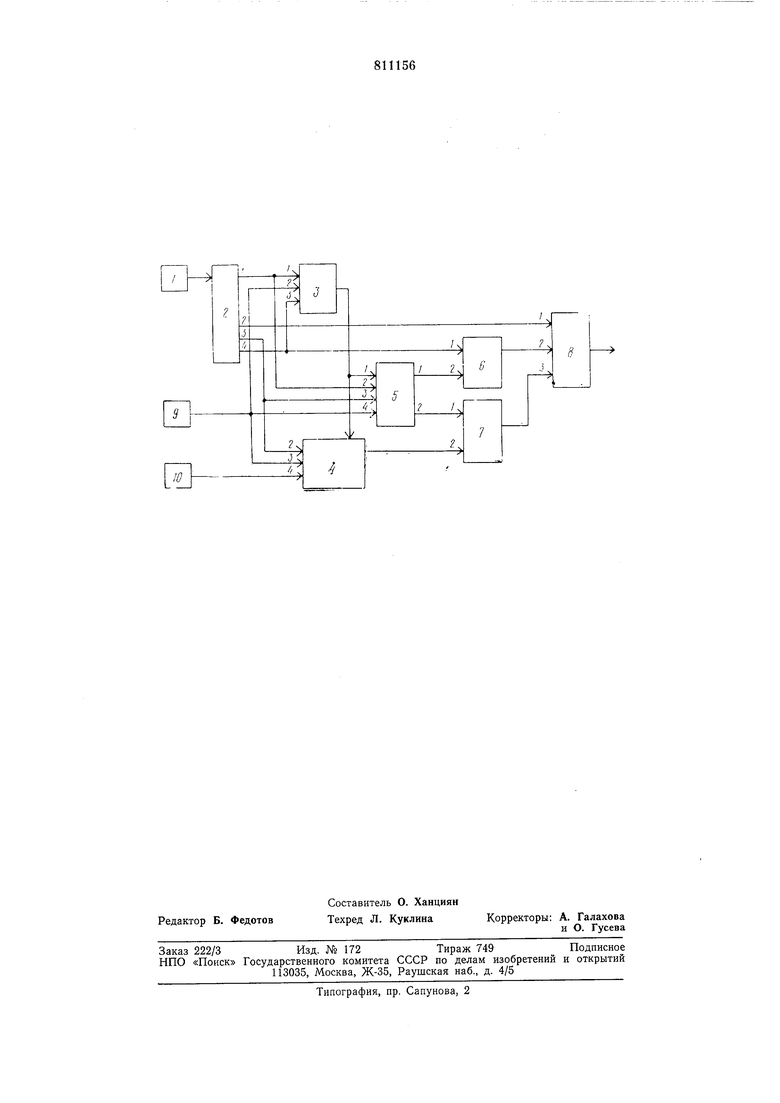

На чертеже представлена блок-схема устройства для контроля скорости изменения частоты.

Устройство содержит формирователь 1 входных сигналов, блок 2 управления, счетчик 3 импульсов, блок 4 умножения, блок 5 разности периодов, блок 6 знака скорости, блок 7 сравнения, элемент И 8, источник 9 эталонной частоты и шифратор 10.

В данном устройстве контроль скорости изменения частоты осуществляется посредством контроля изменения длительности каждого периода следования входных сигналов. При этом устройство вырабатывает сигнал, если выполняется условие:

7-1-У2

5„ Т

где TI и TZ - длительность соответственно первого и второго из двух соседних периодов;

(5„ - параметр, характеризующий скорость изменения частоты и определяющий порог срабатывания устройства.

При этом в зависимости от значения п параметр бп может иметь различный физический смысл.

В данном устройстве счетчик 3 предназначен для формирования числа Ni, пропорционального длительности первого из двух соседних периодов, т. е. .

В блоке 4 умножения формируется число А соответствующее максимально допустимому изменению периода Д Гдоп -б„-Г1.

При этом реализуются операции умножения по одному из известных алгоритмов умножения чисел.

В блоке 5 разности периодов формируется разность чисел импульсов эталонной частоты, заполняющих два соседних периода Ti и Гг.

д/V - yV yV. Г Т,.

Кроме того, при Ni NZ (Ti TZ) на первом выходе блока 5 разности периодов вырабатывается сигнал, свидетельствующий о понижении частоты.

Блок 7 предназначен для сравнения числа AN с числом АЛ/доп и выдачи открывающего сигнала на вход элемента И 8 при условии A/V АЛ допУстройство работает следующим образом. В течение периода TI в счетчик 3 и блок 5 поступают сигналы источника 9. К окончанию периода TI в счетчике 3 формируется число NI TI.

В момент окончания периода Т и начала периода TZ формирователь 1 вырабатывает сигнал, который запускает блок 2 управления. При этом на первом выходе блока 2 появляется запрещающий импульс, который блокирует поступление сигналов источника 9 в счетчик 3 и блок 5. Одновременно с этим появляется импульс управления на втором выходе блока 2. После окончания импульса на втором выходе появляется импульс управления на третьем выходе блока 2 и т. д.

Длительность импульсов управления и интервал времени между ними определяются временем переключения функциональных элементов схемы предлагаемого устройства.

Импульс управления с третьего выхода блока 2 разрешает прием числа из счетчика 3 и числа б из шифратора 10 в блок 4 и числа NI из счетчика 3 в блок 5. При этом в блоке 4 начинается процесс умножения числа б на NI, далее полученный результат (б-JVi) умножается на NI и т. д. до получения результата А Ндоп. б Т .

Импульс управления с четвертого выхода блока 2 устанавливает счетчик 3 в исходное состояние, а блок 5 - во включенное состояние, при котором с его выхода на второй вход элемента И 8 подается открывающий сигнал.

Одновременно с окончанием импульса управления на четвертом выходе блока 2 пропадает закрывающий импульс на его первом выходе и начинается новое заполнение счетчика 3 и блока 5 сигналами источника 9.

К окончанию периода TZ в счетчике 3 будет сформировано число Nz TZ, в блоке 5 - число А NI NI - NZ TI - TZ, в блоке 4 закончится вычисление числа и, если AAi ., с выхода блока 7 на третий вход элемента И 8 будет подан открывающий сигнал.

При TZ TI, что соответствует понижению частоты, блок 5 выработает сигнал, который постунит на второй вход блока 6 и переведет его в выключенное состояние. При этом с выхода блока 6 на второй вход элемента И 8 будет подан закрывающий сигнал.

Если же TZ Гь что соответствует повышению частоты, на первом выходе блока 5 сигнал не появится, и блок 6 останется во включенном состоянии. В момент окончания периода TZ и начала периода Гз произойдет очередной запуск блока 2. При этом импульс с первого выхода блока 2 запретит подачу сигналов источника 9 в счетчик 3 и блок 5. Импульс управления со второго выхода блока 2 поступит па первый вход элемента И 8 и, если при этом на второй и третий входы элемента И 8 будут поданы также открывающие сигналы, на выходе элемента И 8 появится сигнал, который будет свидетельствовать о достижении скоростью повышения частоты предельно допустимого значения бпС окончанием импульсов управления блока 2 начнется новый цикл контроля скорости изменения частоты.

Данное устройство может быть использовано и для коптроля скорости понижения частоты. Для этого второй вход элемента И 8 должен быть соединен с инверсным выходом блока 6 знака скорости. При необходимости контроля скорости изменения частоты по модулю (одновременный контроль скорости повышения и понижения частоты) второй вход элемента И 8 должен быть подключен к логической «1.

Таким образом, в данном устройстве реализуется быстродействующий и точный контроль скорости изменения частоты. Оно может найти широкое применение в системах контроля и аварийной защиты турбореактивных двигателей, паровых турбин, мощных генераторов и гидротурбин.

Формула изобретения

Устройство для контроля скорости изменения частоты, содержащее формирователь входных сигналов, выход которого соединен со входом блока управления, блок разности периодов, блок знака скорости, элемент И и источник эталонной частоты, о тличающееся тем, что, с целью повыщения быстродействия и точности работы устройства, в него введены счетчик импульсов, блок умножения, блок сравнения и шифратор, причем первый выход блока управления соединен с первыми входами счетчика импульсов и блока разности периодов, второй выход блока управления соединен с первым входом элемента И, третий выход блока управления подключен к первому входу блока умножения и второму входу блока разности периодов, а четвертый выход подключен ко второму входу счетчика импульсов и через блок знака скорости - ко второму входу элемента И, третий вход блока разности периодов соединен с выходом счетчика импульсов и вторым входом блока умножения, четвертый вход блока разности периодов подключен к третьему входу счетчика импульсов, третьему входу блока умножения и выходу источника эталонной частоты, первый выход блока разности периодов соединен со вторым входом блока знака скорости, второй выход блока разности периодов соединен через блок сравнения с третьим входом элемента И, а выход шифратора подключен к четвертому входу блока умножения, выход которого соединен со вторым входом блока сравнения.

Источники информации,

принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 591769, кл. G 01R 3/46, 12.04.76.

2.Авторское свидетельство СССР Afo 565258, кл. G 01R 23/00, 04.06.76 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля скорости изменения частоты | 1979 |

|

SU885884A2 |

| Устройство для контроля параметров вращения | 1980 |

|

SU871071A1 |

| Способ преобразования периодического электрического сигнала в код и устройство для его осуществления | 1989 |

|

SU1683175A1 |

| Сигнализатор предельных значений частоты вращения | 1989 |

|

SU1677639A1 |

| Устройство для контроля скорости вращения | 1977 |

|

SU659952A1 |

| СПОСОБ ИЗМЕРЕНИЯ ЧАСТОТЫ (ВАРИАНТЫ) И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ (ВАРИАНТЫ) | 2008 |

|

RU2380716C1 |

| ИЗМЕРИТЕЛЬ ВРЕМЕННЫХ ИНТЕРВАЛОВ | 1972 |

|

SU428353A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU942034A1 |

| Измеритель скорости изменения частоты | 1985 |

|

SU1288620A1 |

| Устройство для контроля скорости вращения | 1976 |

|

SU591769A1 |

Авторы

Даты

1981-03-07—Публикация

1979-03-28—Подача