(54) ЛОГИЧЕСКИЙ МОДУЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический модуль | 1979 |

|

SU890387A2 |

| Устройство для контроля ошибок канала магнитной записи-воспроизведения | 1983 |

|

SU1101887A1 |

| Коммутирующее устройство | 1986 |

|

SU1510075A1 |

| Устройство для приема дискретной информации | 1974 |

|

SU506896A1 |

| Устройство для контроля неисправностей в цифровой системе связи | 1983 |

|

SU1104574A1 |

| Устройство для контроля пневматических приборов | 1980 |

|

SU934226A1 |

| Автоматический контрольно-пропускной пункт | 1976 |

|

SU596987A1 |

| Устройство для автоматического управления поливом | 1988 |

|

SU1519594A1 |

| Устройство для приема телеметрической информации | 1978 |

|

SU734785A1 |

| Устройство контроля за электромагнитным приводом постоянного тока тормоза | 1982 |

|

SU1075031A1 |

Изобретение относится к управлению технологическими процесса.ми и .может быть использовано, например, для управления процессом нанесения покрытий с по.мощью пневмораспылителей. Известен логический модуль, содержащий элементы И, ИЛИ, НЕ I. Недостатком его является невозможность обработки аналоговых сигналов. Наиболее близким по технической сущности и достигаемому результату к предлагаемо.му является логический модуль, содержащий два канала, каждый из которых содержит первый элемент ЗАПРЕТ, блок памяти и реле времени, причем информационнЕяй вход первого элемента ЗАПРЕТ первого соединен с запрещающим входом первого элемента НЕ второго канала и является первым входом модуля, имеющего сенсорные датчики г. Недостатком его является невозможность отрабатывать аналоговые сигналы. Цель изобретения - расщирение области применения за счет возможности обработки как аналоговых так и дискретных сигналов. Поставленная цель достигается тем, что логический модуль содержит элемент ИЛИ и кроме того в каждом канале второй и третий элементы ЗАПРЕТ и элемент НЕ, причем в каждом канале выход первого элемента ЗАПРЕТ соединен с запрещающим входом второго элемента ЗАПРЕТ, выход которого соединен с первым входом блока памяти, выход которого подключен через реле времени к запрещающему входу третьего элемента ЗАПРЕТ, выход третьего элемента ЗАПРЕТ второго канала соединен со вторым входом блока памяти первого канала и со вторым запрещающим входом третьего элемента ЗАПРЕТ первого канала, выход которого подключен к первому входу элемента ИЛИ, второй вход которого является вторым входом модуля, а выход является первым выходом устройства, выход блока памяти первого канала соединен с информационным входом первого элемента ЗАПРЕТ второго канала и через элемент НЕ первого канала - со вторым входом блока памяти второго канала, причем запрещающий вход первого элемента ЗАПРЕТ первого канала и выход второго эле.мента ЗАПРЕТ первого

канала являются соответственно третьим входом и третьим выходом модуля, а второй заирещающий вход второго элемента ЗАПРЕТ первого канала является четвертым входом модуля.

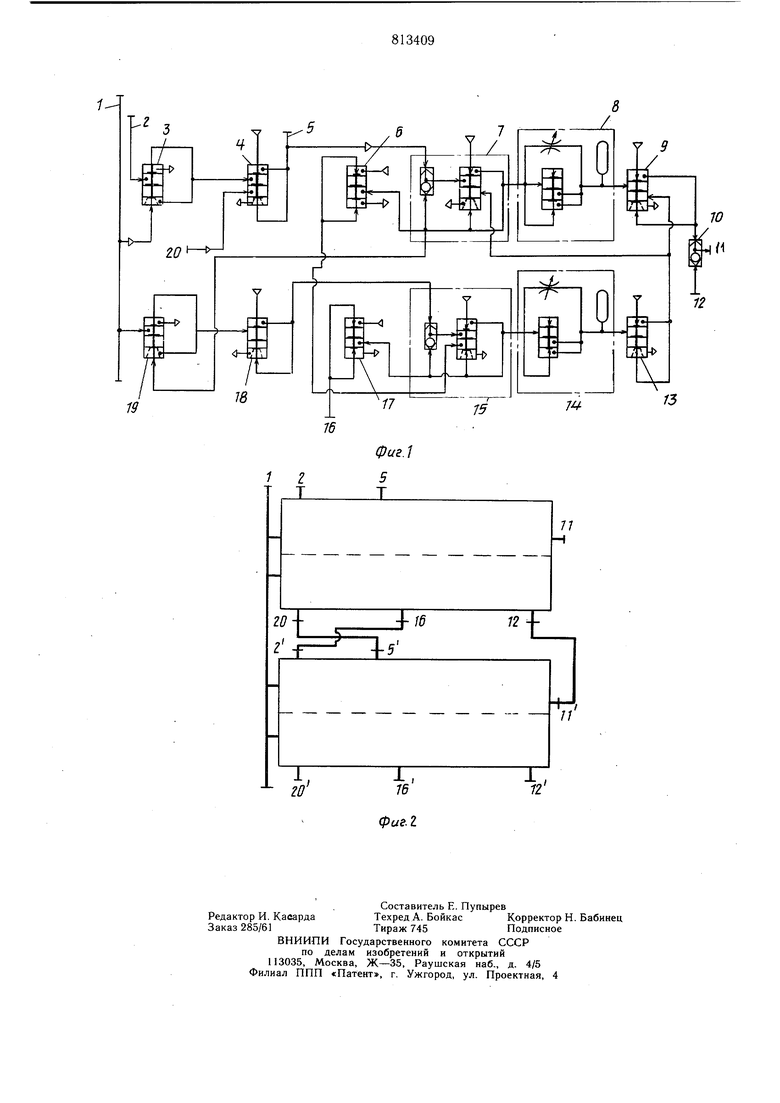

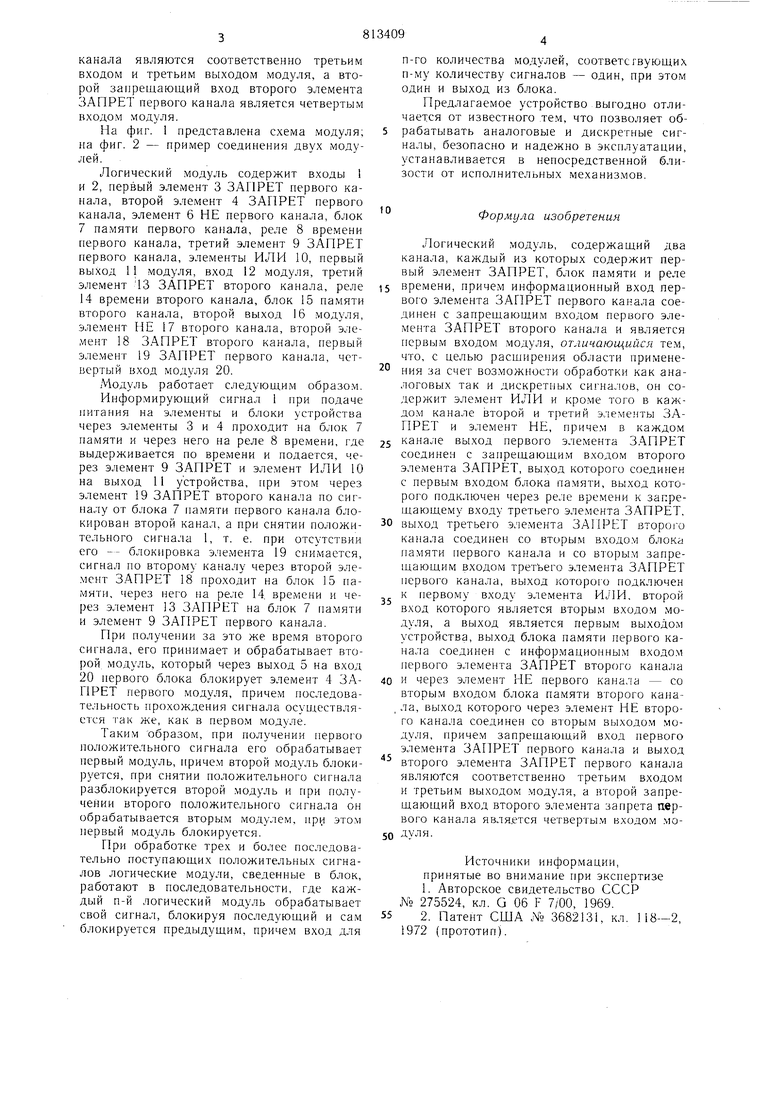

На фиг. 1 представлена схема модуля; на фиг. 2 - пример соединения двух .модулей.

Логический модуль содержит входы 1 и 2, первый элемент 3 ЗАПРЕТ первого канала, второй элемент 4 ЗАПРЕТ первого канала, элемент 6 НЕ первого канала, блок 7 памяти первого капала, реле 8 времени первого канала, третий эле.мент 9 ЗАПРЕТ первого капала, элементы ИЛИ 10, первый выход 11 модуля, вход 12 модуля, третий элемент ТЗ ЗАПРЕТ второго канала, реле 14 времени второго канала, блок 15 памяти второго канала, второй выход 16 модуля, элемент НЕ 17 второго канала, второй элемент 18 ЗАПРЕТ второго канала, первый элемент 19 ЗАПРЕТ первого канала, четвертый вход модуля 20.

Модуль работает следующим образо.м. Информируюш.ий сигнал 1 при подаче питания на элементы и блоки устройства через элементы 3 и 4 проходит на блок 7 памяти и через него на реле 8 времени, где выдерживается по времени и подается, через элемент 9 ЗАПРЕТ и элемент ИЛИ 10 на выход 11 устройства, при этом через элемент 19 ЗАПРЕТ второго канала по сигналу от блока 7 памяти первого канала блокирован второй канал, а при снятии положительпого сигнала 1, т. е. при отсутствии его -- блокировка элемента 19 снимается, сигнал по второму каналу через второй эле.мент ЗАПРЕТ 18 проходит на блок 15 памяти, через пего па реле 14, вре.мени и через элемент 13 ЗАПРЕТ на блок 7 памяти и элемент 9 ЗАПРЕТ первого канала.

При получении за это же время второго сигнала, его принимает и обрабатывает второй модуль, который через выход 5 на вход 20 нервого блока блокирует элемент 4 ЗАПРЕТ первого модуля, причем последовательность прохождения сигнала осуплествляется так же, как в первом модуле.

Таки.м образом, при получении первого положительного сигнала его обрабатывает первый модуль, причем второй модуль блокируется, при снятии положительного сигнала разблокируется второй модуль и при получении второго положительного сигнала он обрабатывается вторым модулем, при этом первый модуль блокируется.

При обработке трех и более последовательно поступаюплих положительных сигналов логические модули, сведенпые в блок, работают в последовательности, где каждый п-й логический модуль обрабатывает свой сигнал, блокируя последующий и сам блокируется предыдущим, причем вход для

п-го количества модулей, соответсгвующих п-му количеству сигналов - один, при это.м один и выход из блока.

Предлагаемое устройство выгодно отличается от известного .тем, что позволяет обрабатывать аналоговые и дискретные сигналы, безопасно и надежно в эксплуатации, устанавливается в непосредственной близости от исполнительных механиз.мов.

Формула изобретения

Логический модуль, содержащий два канала, каждый из которых содержит первый эле.мент ЗАПРЕТ, блок памяти и реле

времени, причем информационный вход первого элемента ЗАПРЕТ первого канала соединен с запрещающи.м входом первого элемента ЗАПРЕТ второго канала и является первы.м входом модуля, отличающийся те.м, что, с целью расщирепия области применения за счет воз.можности обработки как аналоговых так и дискретных сигналов, он содержит элемент ИЛИ и кроме того в каждом канале второй и третий э.лементы ЗАПРЕТ и элемент НЕ, причем в каждом

5 канале выход первого элемента ЗАПРЕТ соединен с запрещающи.м входом второго элемента ЗАПРЕТ, выход которого соединен с первым входом блока памяти, выход которого подключен через реле времени к запрещающему входу третьего эле.мента ЗАПРЕТ,

0 выход третьего элемента ЗАПРЕТ BTOpoio капала соединен со вторы.м входо.м блока памяти первого канала и со вторым запрещающим входом третьего элемента ЗАПРЕТ первого канала, выход которого подключен к первому входу элемента ИЛИ, второй вход которого является вторым входом модуля, а выход является первым выходом устройства, выход блока памяти первого канала соединен с информационным входо.м первого элемента ЗАПРЕТ второго канала

0 и через элемент НЕ первого канала - со вторым входом блока памяти второго канала, выход которого через элемент НЕ второго канала соединен со вторым выходом модуля, причем запрещающий вход первого элемента З.АПРЕТ первого канала и выход

второго элемента ЗАПРЕТ первого канала являются соответственно третьим входом и третьим выходом модуля, а второй запреихающий вход второго эле.мента запрета первого канала явля.ется четверты.м входом .модуля.

Источники информации, принятые во вни.мание при экспертизе 1. Авторское свидетельство СССР № 275524, кл. G 06 F 7/00, 1969. 5 2. Патент США № 3682131, кл. 1 18--2, 1972 (прототип).

1 г

ь

20 -+ }6

-г- 4-5 20

фиг.

5 Л

12 -

Г7

W фаг. 2

Авторы

Даты

1981-03-15—Публикация

1978-04-24—Подача