1

Изобретение относится к радиотехнике и может быть использовано в устройствах импульсной и вычислительной техники.

Известен формирователь задержки импульсов, содержащий триггер с установочными входами и двумя выходами, к одному из которых подключен через конденсатор один из входов триггера и анод диода, один из установочных входов триггера подключен к выходу ждуш,его мультивибратора, вход которого соединен с выходом промежуточного клапана, а второй установочный вход и выход триггера подключены к двум другим входам про.межуточного клапана 1.

Недостатками такого формирователя являются сложность, низкая стабильность временных параметров выходного сигнала при изменении питающего напряжения и ограниченная возможность использования логических элементов транзисторно-транзисторной логики с встроенными шунтирующими диодами на входах многоэмиттерного транзистора из-за-больщих входных токов, протекающих по шунтирующим диодам при перезаряде вре.мязадающих конденсаторов.

Цель изобретения - упрощение устройства 11 повышения стабильности временных параметров выходных импульсов.

Для достижения указанной цели в формирователе задержки импульсов, содержащем триггер с двумя входами, два последовательно включенны.х инвертора и конденсатор, один из выводов которого соединен с первым выходом триггера, при этом один вход триггера соединен с источником запускающих импульсов, а другой соединен

0 с выходом второго инвертора и выходом устройства, другой вывод конденсатора подключен к входу первого инвертора и через резистор к второму выходу триггера, а вход первого инвертора соединен с анодом диода, катод которого соединен с источнико.м

напряжения.

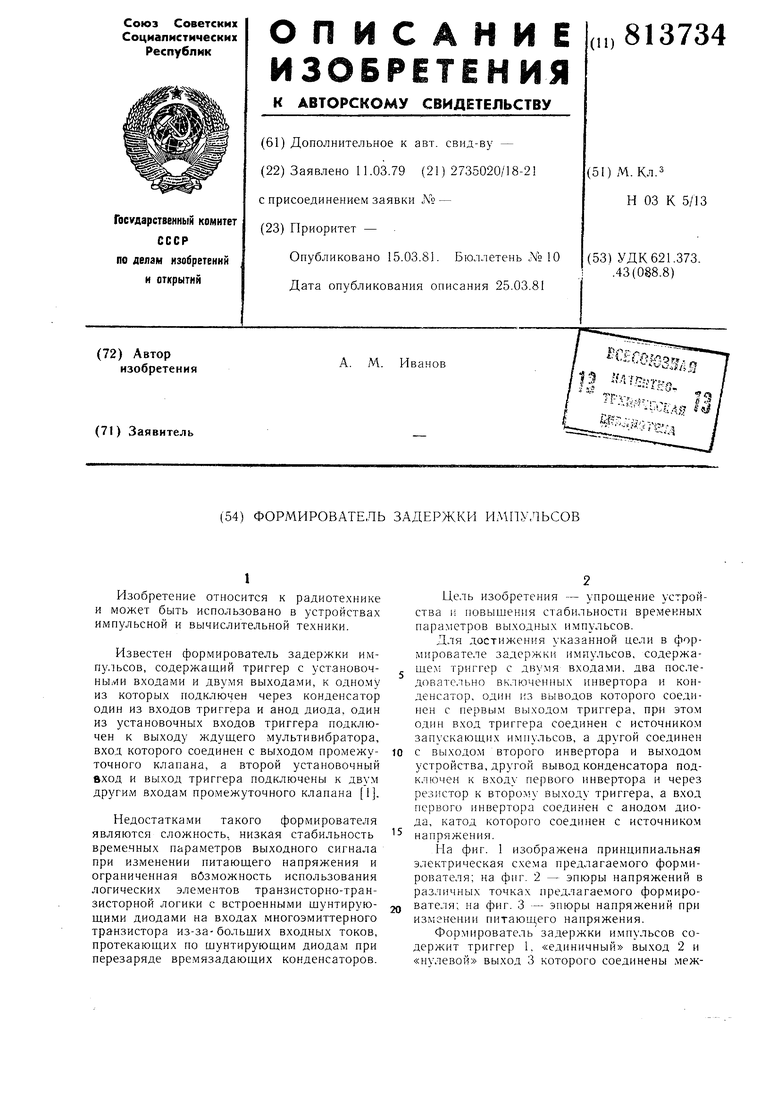

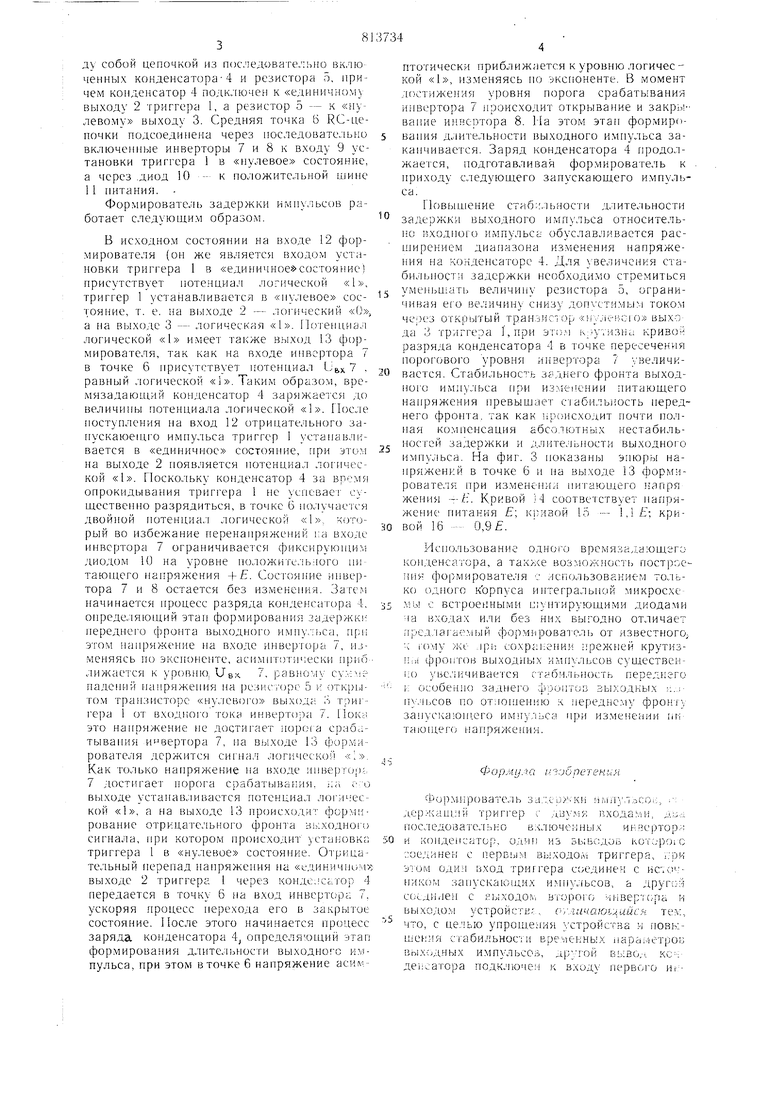

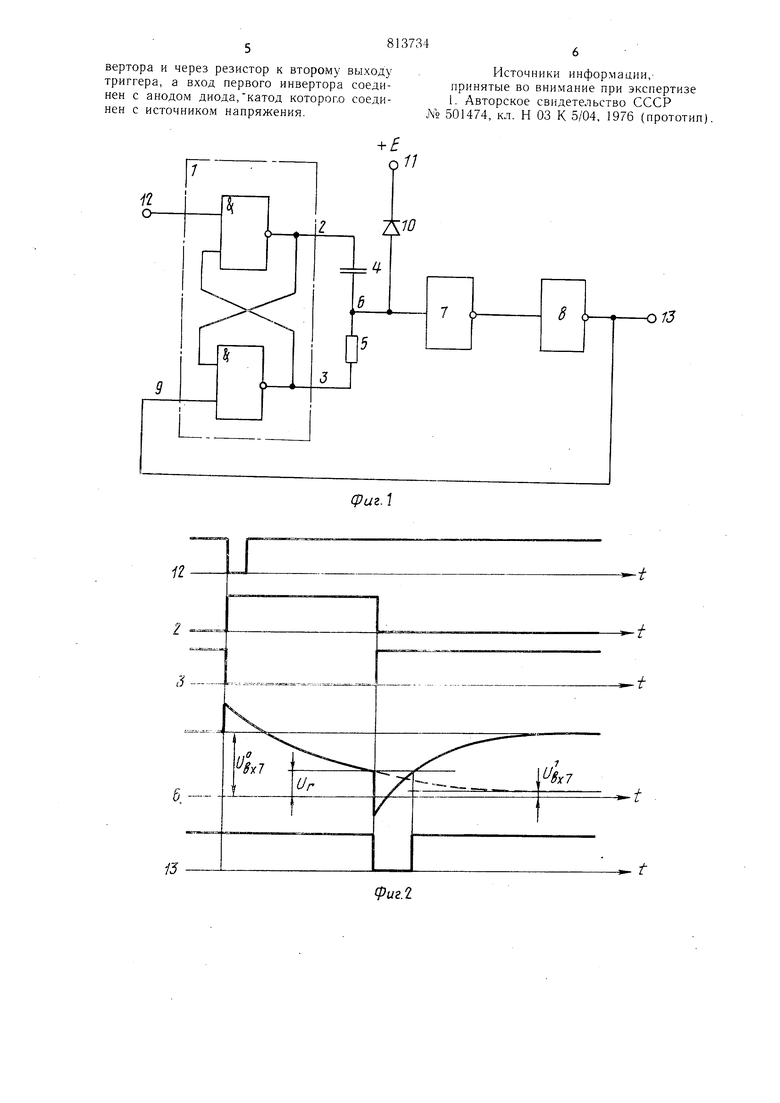

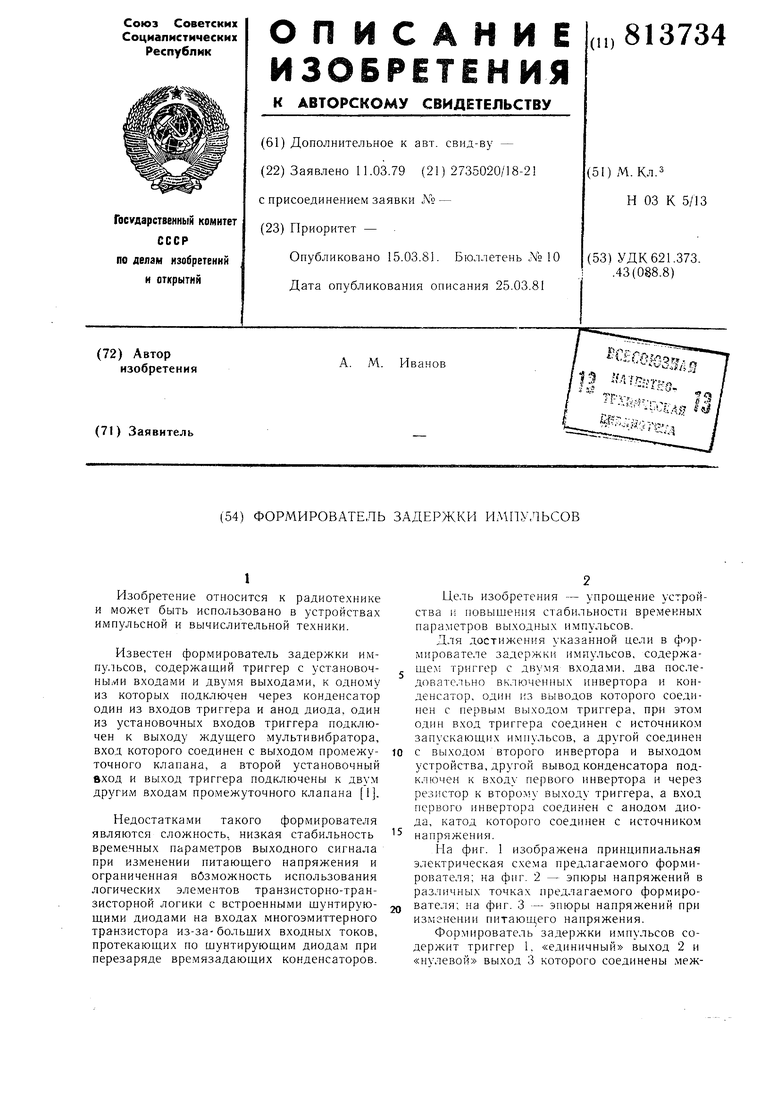

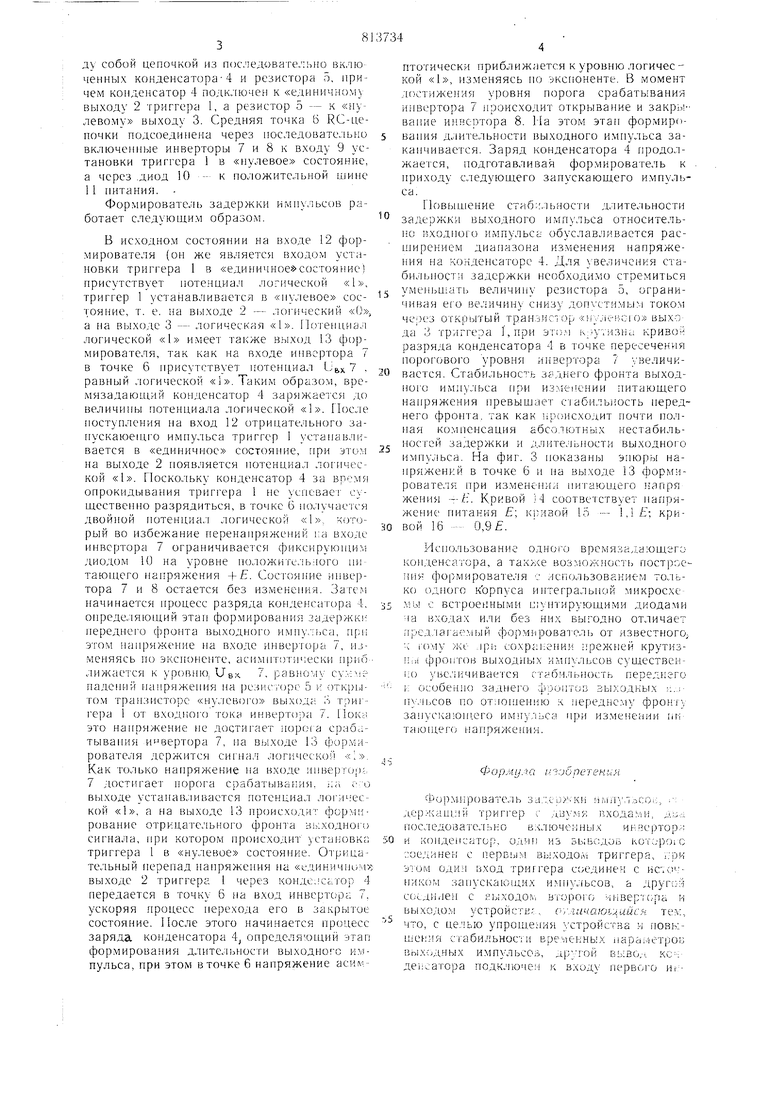

На фиг. 1 изображена принципиальная электрическая схема предлагаемого формирователя; на фиг. 2 - эпюры напряжений в различных точках предлагаемого формирователя; на фиг. 3 - эпюры напряжений при изменении питающего напряжения.

Формирователь задержки импульсов содержит триггер 1, «единичный выход 2 и «нулевой выход 3 которого соединены .между собой цепочкой нз последовательно включенных конденсатора-4 и резистора о, нричем конденсатор 4 подключен к «единичному выходу 2 триггера 1, а резистор 5 - к «нулевому выходу 3. Средняя точка 6 RC-цепочки подсоединена через последовательно включенные инверторы 7 и 8 к входу 9 установки триггера 1 в «нулевое состояние, а через .диод 10 - к положительной шине 11 питания. .

Формирователь задержки имнульсов работает еледуюпгим образом.

В исходном состоянии на входе 12 формирователя (он же является вхо.аом установки триггера 1 в «единичное состояние; присутствует потенциал логической «Ь, триггер 1 устанавливается в «нулевое состояние, т. е. на В1 1ходе 2 - ло|-ический «О, а на выходе 3 - логическая «1. Потенциа.л логической «1 имеет также 13 формирователя, так как на входе инвертора 7 в точке 6 присутствует потенциал UE.X 7 . равный .логической «i. Таким образо.м, вре.мязадающий конденсатор 4 заряжается до величины потенциала логической «1. После поступления на вход 12 отрицательного зануекаюещго имцульса триггер 1 устанавливается в «единичное состояние, при это.м на выходе 2 появляется потенциал логпческой «1. Поскольку конденсатор 4 за вр;мя опрокидывания триггера 1 не успевает существенно разрядиться, в точке 6 нолучается двойной потенциал логической «1, который во избежание перенанряжений i:a входе инвертора 7 ограничивается фиксируюн1им диодом 10 на уровне положите. питающего напряжения +.. Состояние инвертора 7 и 8 оетаетси без изменения. Затем начинается процесс разряда конденсатора 4. опреде.ляюнхий этан формирования задержки: нереднсго фронта выходного HMny/riica, этом нан|)яженне на входе инвертор 7, пзменяясь по экспоненте, аси.мпт:)тически 1риб лижается к уровню, Us;-. 7, равному ev:-.: падений напряжения на резис,-оре 5 к: открчлтом транзисторе «ну.левого выхода Л три|-гера 1 от входного тока инверто;1а 7. Пок;; это нанряжение не достигает порога срабатывания и вертора 7, па выходе 13 ф эрмирователя держится сигна, ;10Г1;ческой -х. Как только напряжение на входе ипве)Т(,)-: 7 достигает порога срабатывания, iia ; о выходе устанавливается потенциал ло|-ической «1, а на выходе 13 происхо.аи ; формирование отрицательного фронта ь;1 :ходного си1Д1ала, нри котором нроисходит установка триггера 1 в «нулевое состояние. Отрицательный нерепад напряжения на « динич11о:ч ; выходе 2 триггера 1 через конде;:с;-тор 4 передается в точку 6 на вхо.д инвертора 7. ускоряя процесс иерехода его в закрытое еоетояние. После этого начинается процесс заряда ко1-1денсатора 4 опре.деля-ощий этап формирования длительности выходного импульса, при этом в точке 6 напряжение асимптотически приближается к уровню логичес кой «1, из.меняясь но экспоненте. В момент достижения уровня порога срабатывания инвертора 7 происходит открывание и закрывание иннеотора 8. Па этом этап формировапня длительности выходного и.мпульеа закапчивается. Заряд конденсатора 4 продолжается, подготавливая формирователь к приходу следующего запускающего и.мпульеа.

I loBtjimeHHe етаб::льности длите шности

задержки выходного и у1пульса относительно входного нмнульсс обуславливается раецп1рениегу1 диапазона изменения напряжения на конденсаторе 4. Для мзеличения етабильноети задержки необходимо стремиться

умен1Щ1ат1) величину резистора 5, ограничивая его величину снизу допхттимым током че;)(3 откр1з1тый траизнст ор «иулег:с1 о выхо да 3 триггера 1,при этп.ч к:Л7изн кривой разряда конденсатора 4 в Т1:чке пересечения порогового уровня инвертора 7 увеличкваетея. Стабильнос-уь заднего фронта выходного имну.льса при из.меиении питающего нанряжения цревьипает с1абиль);ость переднего фронта, так как происходит почти полпая компенсация абсолютных нестабильностей задержки и д.лителыюсти выходного импульса. На фиг. 3 показаны эпюры напряжений в точке 6 и на выходе 13 формирователя при из.менепил питающего напря жепин --с. Кривой 4 соответствует напряжение питания ; К|;иаой 15 -- ,; кривой 16 0,9.

Использование одного времязал.ающего конденса1ора, а возмок {оеть построения формирователя с лепользованием только одпого корпуса интегральной микросхе

.МЫ с встроенными щунтирующими диодами ча входах или без них выгодно отличает лрсд.лагаемый формирователь от извеетногО; ; .ому же ipi: сохра :ении прежней крутиз i::i фронтов вьгходнь х кмпульсов суняеетвенi:o увеличивается стабильность переднего

i: особенно заднего фронтов выходных :.:ПУЛЬСОВ по от:юп1ению к переднс;.1у фронту запускаюпюго имнульса при из.мепепии пи таю1цег(; напряжется.

Формирователь за;:с:и д н мм/1улзсо.;, .лер:-; ан1. т)иггер У .ч,13}мя пходами, последовательно включеппых инвертору

и конденсатор, одип нз ЗЫВСДОБ кот:;рО С соединен с первым выходом триггера, ,;рк этом одни вход триггера с(;еди1-1ен е ис.оспиком запускаю1цих и П1ульсов, а другой соединен с выходом второго чнвертс/ра и выходом устройств;. оуличо-ющийся тем,

что, е целью упрощения устройства и повьушения стабильности временных iiapa:.ieTpOo

ИМНуЛЬСОй, другой ВЬ;БО,ч. КС У

деисатора подключен к входу первого ntвертора и через резистор к второму выходу триггера, а вход первого инвертора соединен с анодом диода, катод которого соединен с источником напряжения.

Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 501474, кл. Н 03 К 5/04, 1976 (прототип).

07J

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь задержки импульсов | 1982 |

|

SU1083354A1 |

| Формирователь дискретных сигналов | 1982 |

|

SU1115210A1 |

| Формирователь импульсов | 1977 |

|

SU930616A1 |

| Формирователь дискретных сигналов | 1979 |

|

SU809523A1 |

| Устройство для задержки сигналов | 1982 |

|

SU1251308A1 |

| Преобразователь постоянного напряжения | 1981 |

|

SU1056390A1 |

| Формирователь импульсов | 1982 |

|

SU1043820A1 |

| Устройство для допускового контроля напряжения | 1983 |

|

SU1170422A1 |

| Формирователь импульсов | 1981 |

|

SU993453A1 |

| Устройство для сравнения двоичных чисел | 1985 |

|

SU1663608A1 |

Авторы

Даты

1981-03-15—Публикация

1979-03-11—Подача