ё

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В БИПОЛЯРНЫЙ КОД | 2002 |

|

RU2218660C2 |

| Регистр сдвига | 1982 |

|

SU1111207A1 |

| Формирователь дискретных сигналов | 1982 |

|

SU1115210A1 |

| Устройство для сопряжения цифровой вычислительной машины | 1987 |

|

SU1444793A1 |

| Селектор импульсов по длительности | 1984 |

|

SU1226631A1 |

| ПРЕОБРАЗОВАТЕЛЬ ИНЕРЦИАЛЬНОЙ ИНФОРМАЦИИ | 2006 |

|

RU2325620C2 |

| Электронное реле времени | 1983 |

|

SU1115231A1 |

| Формирователь задержки импульсов | 1979 |

|

SU813734A1 |

| Устройство для формирования импульсов | 1987 |

|

SU1582342A1 |

| Формирователь задержки импульсов | 1982 |

|

SU1083354A1 |

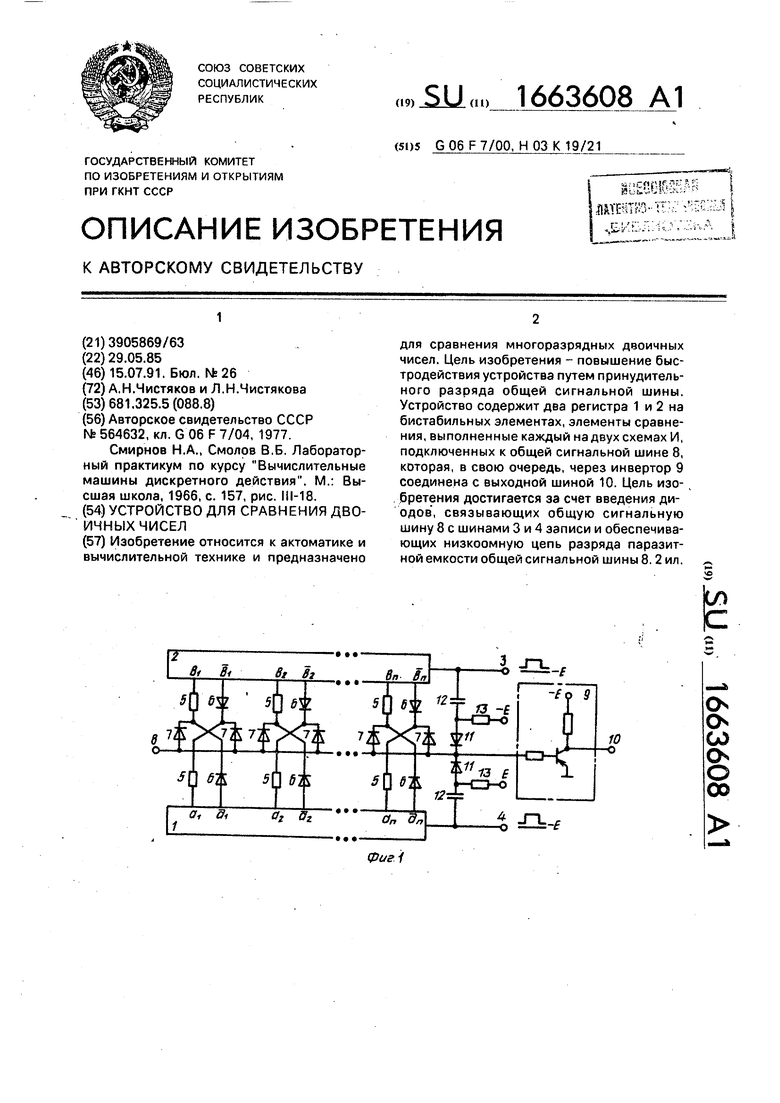

Изобретение относится к автоматике и вычислительной технике и предназначено для сравнения многоразрядных двоичных чисел. Цель изобретения - повышение быстродействия устройства путем принудительного разряда общей сигнальной шины. Устройство содержит два регистра 1 и 2 на бистабильных элементах, элементы сравнения, выполненные каждый на двух схемах И, подключенных к общей сигнальной шине 8, которая, в свою очередь, через инвертор 9 соединена с выходной шиной 10. Цель изобретения достигается за счет введения диодов, связывающих общую сигнальную шину 8 с шинами 3 и 4 записи и обеспечивающих низкоомную цепь разряда паразитной емкости общей сигнальной шины 8. 2 ил.

Os О СА СЬ О 00

Изобретение относится к автоматике и вычислительной технике и может быть использовано для сравнения многоразрядных двоичных чисел.

Цель изобретения - повышение быстродействия устройства путем принудительного разряда общей сигнальной шины.

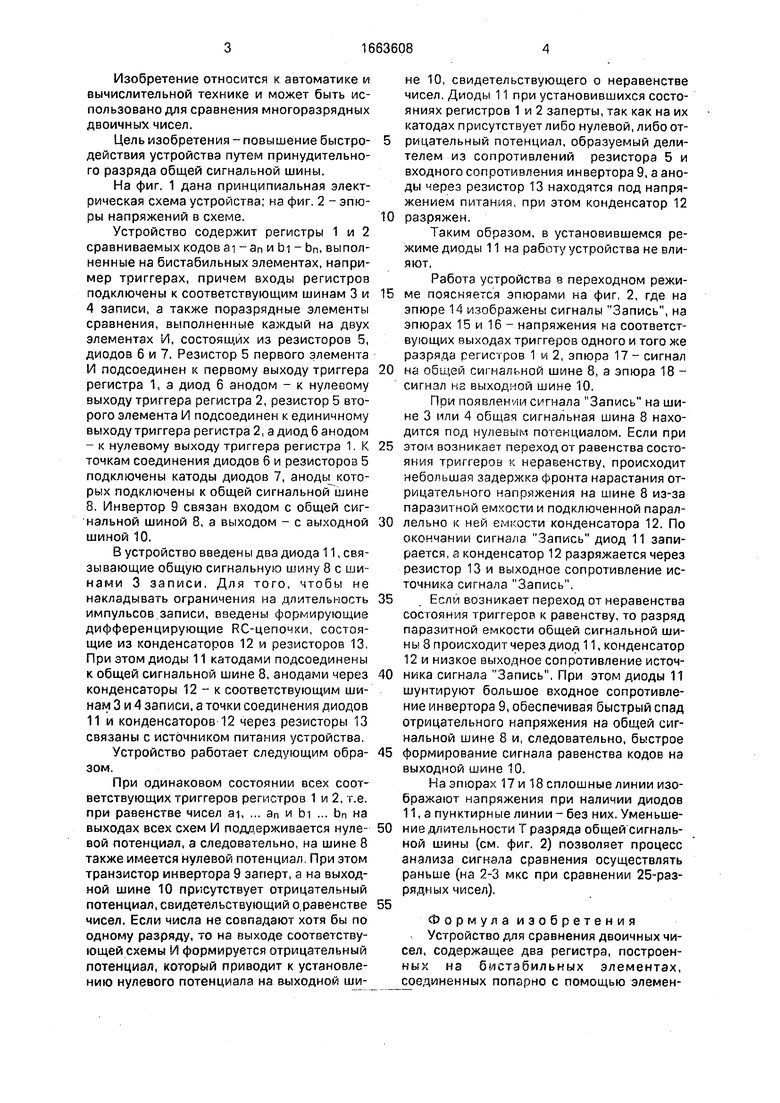

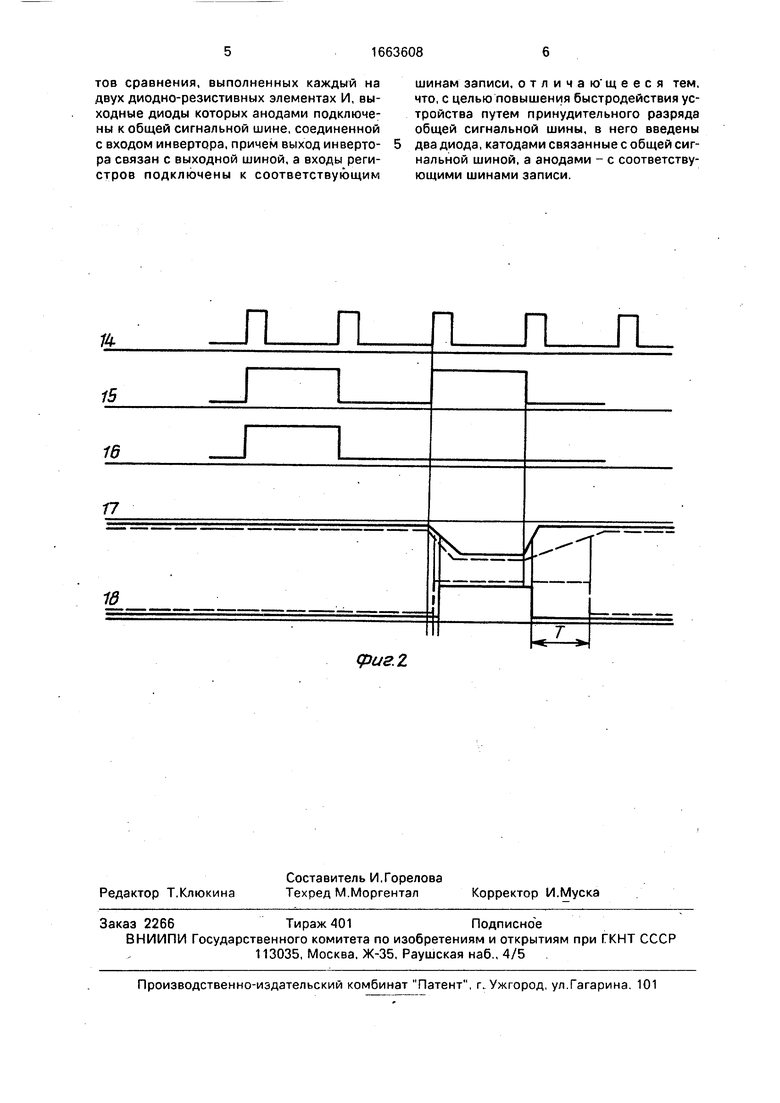

На фиг. 1 дана принципиальная электрическая схема устройства; на фиг. 2 - эпюры напряжений в схеме.

Устройство содержит регистры 1 и 2 сравниваемых кодов ai - an и bi - bn, выполненные на бистабильных элементах, например триггерах, причем входы регистров подключены к соответствующим шинам 3 и 4 записи, а также поразрядные элементы сравнения, выполненные каждый на двух элементах И, состоящих из резисторов 5, диодов 6 и 7. Резистор 5 первого элемента И подсоединен к первому выходу триггера регистра 1, а диод 6 анодом - к нулевому выходу триггера регистра 2, резистор 5 второго элемента И подсоединен к единичному выходу триггера регистра 2, а диод 6 анодом - к нулевому выходу триггера регистра 1. К точкам соединения диодов 6 и резисторов 5 подключены катоды диодов 7, аноды которых подключены к общей сигнальной шине 8. Инвертор 9 связан входом с общей сигнальной шиной 8, а выходом - с выходной шиной 10.

В устройство введены два диода 11, связывающие общую сигнальную шину 8 с шинами 3 записи. Для того, чтобы не накладывать ограничения на длительность импульсов записи, введены формирующие дифференцирующие RC-цепочки, состоящие из конденсаторов 12 и резисторов 13, При этом диоды 11 катодами подсоединены к общей сигнальной шине 8, анодами через конденсаторы 12 - к соответствующим шинам 3 и 4 записи, а точки соединения диодов 11 и конденсаторов 12 через резисторы 13 связаны с источником питания устройства.

Устройство работает следующим образом.

При одинаковом состоянии всех соответствующих триггеров регистров 1 и 2, т.е. при равенстве чисел ai, ... an и bi ... bn на выходах всех схем И поддерживается нулевой потенциал, а следовательно, на шине 8 также имеется нулевой потенциал, При этом транзистор инвертора 9 заперт, а на выходной шине 10 присутствует отрицательный потенциал, свидетельствующий о.равенстве чисел. Если числа не совпадают хотя бы по одному разряду, то на выходе соответствующей схемы И формируется отрицательный потенциал, который приводит к установлению нулевого потенциала на выходной шине 10, свидетельствующего о неравенстве чисел. Диоды 11 при установившихся состояниях регистров 1 и 2 заперты, так как на их катодах присутствует либо нулевой, либо отрицательный потенциал, образуемый делителем из сопротивлений резистора 5 и входного сопротивления инвертора 9, а аноды через резистор 13 находятся под напряжением питания, при этом конденсатор 12

разряжен.

Таким образом, в установившемся режиме диоды 11 на работу устройства не влияют,

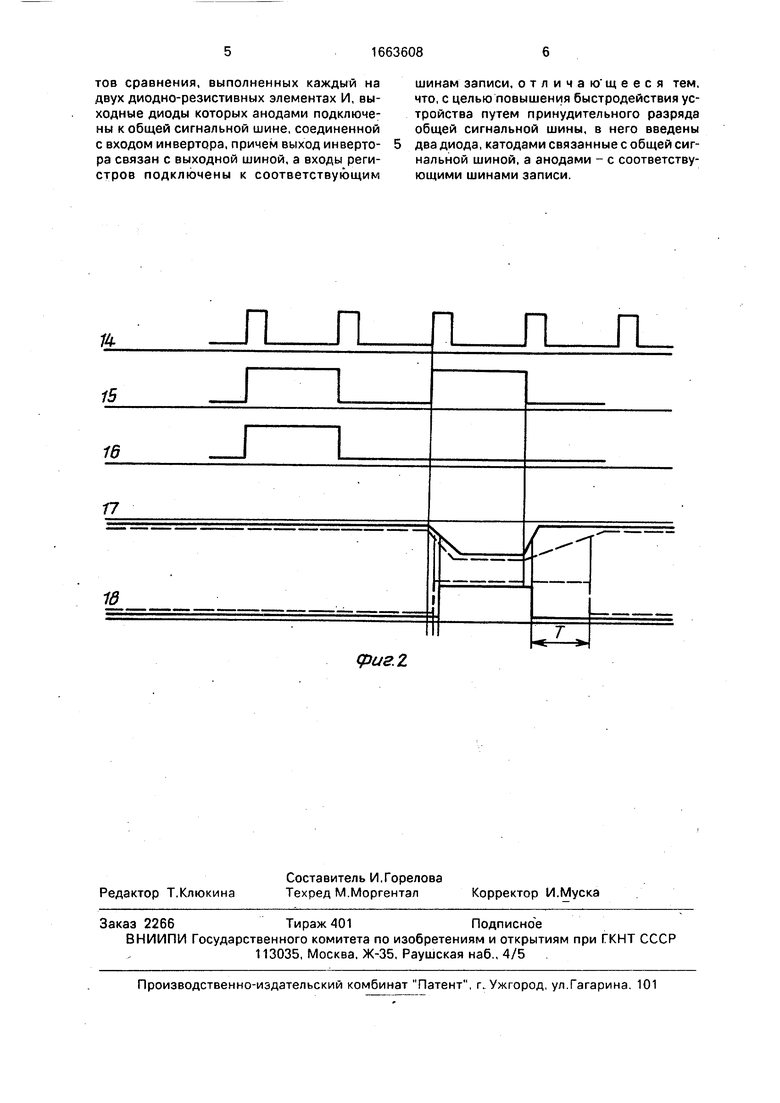

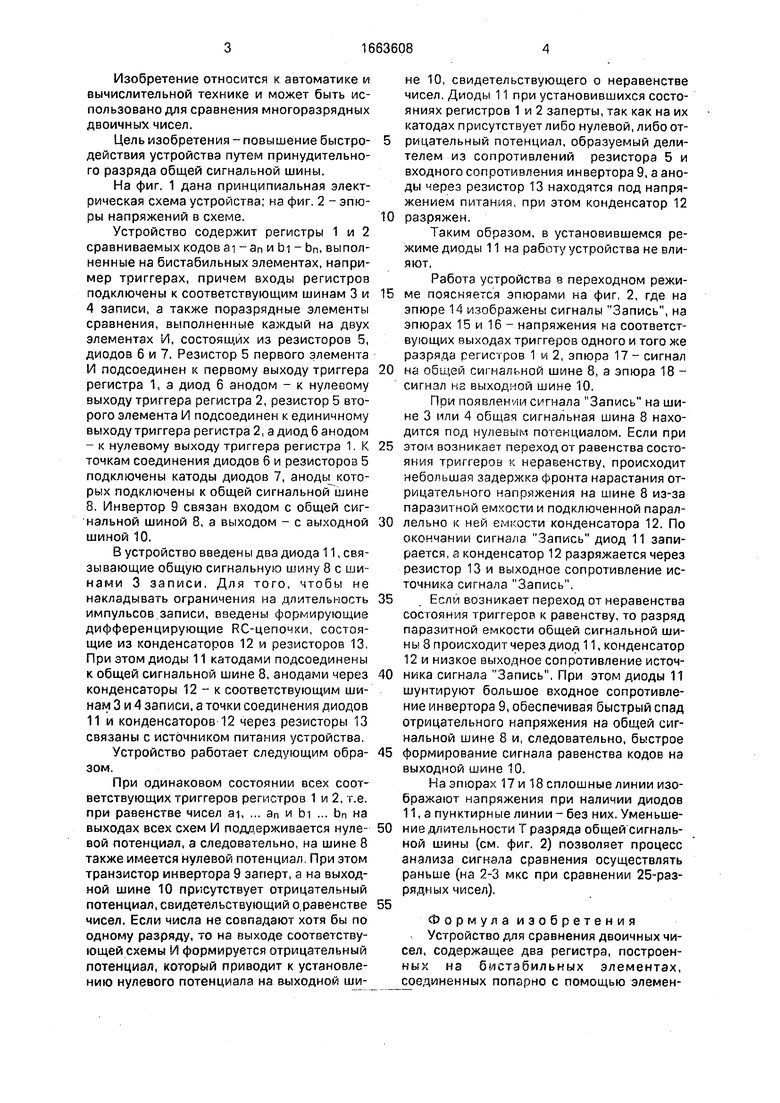

Работа устройства в переходном режиме поясняется эпюрами на фиг, 2, где на эпюре 14 изображены сигналы Запись, на эпюрах 15 и 16 - напряжения на соответствующих выходах триггеров одного и того же разряда регистров 1 и 2, эпюра 17- сигнал

на общей сигнальной шине 8, а эпюра 18 - сигнал на выходной шине 10.

Пои появлении сигнала Запись на шине 3 или 4 общая сигнальная шина 8 находится под нулевым потенциалом. Если при

этом возникает переход от равенства состояния триггеров к неравенству, происходит небольшая задержка фронта нарастания отрицательного напряжения на шине 8 из-за паразитной емкости и подключенной параллельно к ней емкости конденсатора 12. По окончании сигнала Запись диод 11 запирается, а конденсатор 12 разряжается через резистор 13 и выходное сопротивление источника сигнала Запись.

Еслм возникает переход от неравенства

состояния триггеров к равенству, то разряд паразитной емкости общей сигнальной шины 8 происходит через диод 11, конденсатор 12 и низкое выходное сопротивление источника сигнала Запись. При этом диоды 11 шунтируют большое входное сопротивление инвертора 9, обеспечивая быстрый спад отрицательного напряжения на общей сигнальной шине 8 и, следовательно, быстрое

формирование сигнала равенства кодов на выходной шине 10.

На эпюрах 17 и 18 сплошные линии изображают напряжения при наличии диодов 11, а пунктирные линии- без них. Уменьшение длительности Т разряда общей сигнальной шины (см. фиг, 2) позволяет процесс анализа сигнала сравнения осуществлять раньше (на 2-3 мкс при сравнении 25-разрядных чисел).

Формула изобретения Устройство для сравнения двоичных чисел, содержащее два регистра, построенных на бистабильных элементах, соединенных попарно с помощью элементов сравнения, выполненных каждый на двух диодно-резистивных элементах И, выходные диоды которых анодами подключены к общей сигнальной шине, соединенной с входом инвертора, причем выход инвертора связан с выходной шиной, а входы регистров подключены к соответствующим

шинам записи, отличаю щееся тем, что, с целью повышения быстродействия устройства путем принудительного разряда общей сигнальной шины, в него введены два диода, катодами связанные с общей сигнальной шиной, а анодами - с соответствующими шинами записи.

Фиг. 2

| Устройство для сравнения двоичных чисел | 1975 |

|

SU564632A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Смирнов НА, Смолов В.Б | |||

| Лабораторный практикум по курсу Вычислительные машины дискретного действия | |||

| М.: Высшая школа, 1966, с | |||

| Соломорезка | 1918 |

|

SU157A1 |

| Говорящий кинематограф | 1920 |

|

SU111A1 |

Авторы

Даты

1991-07-15—Публикация

1985-05-29—Подача