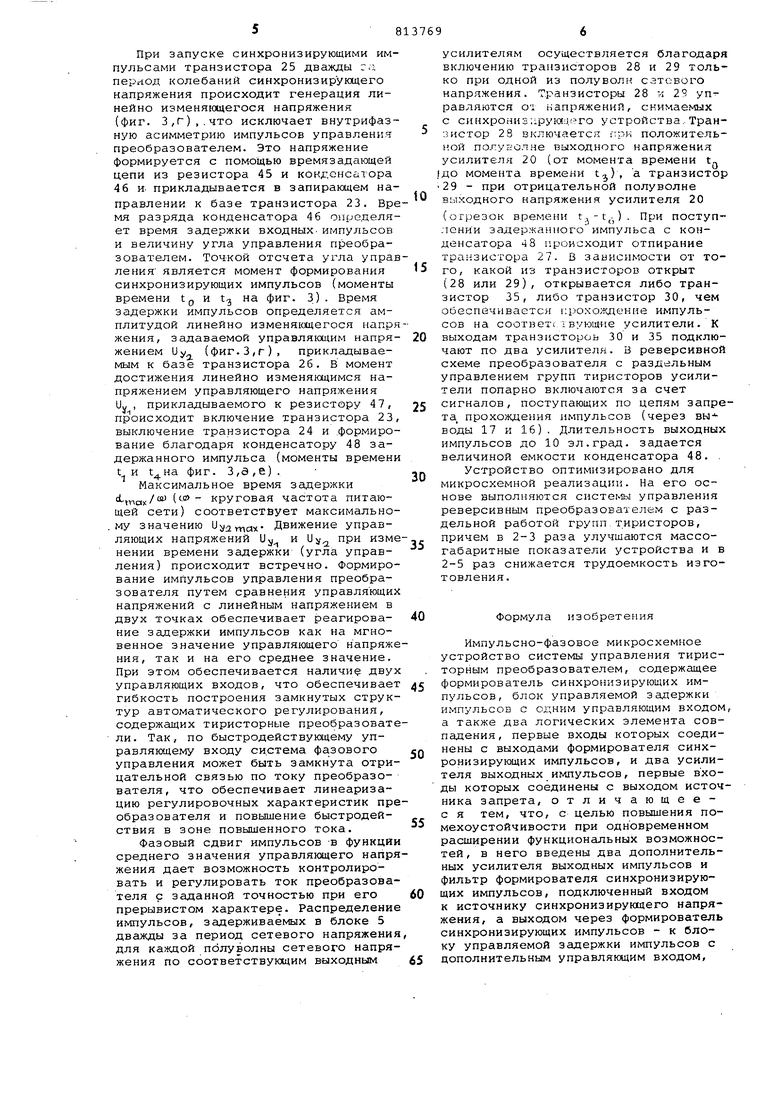

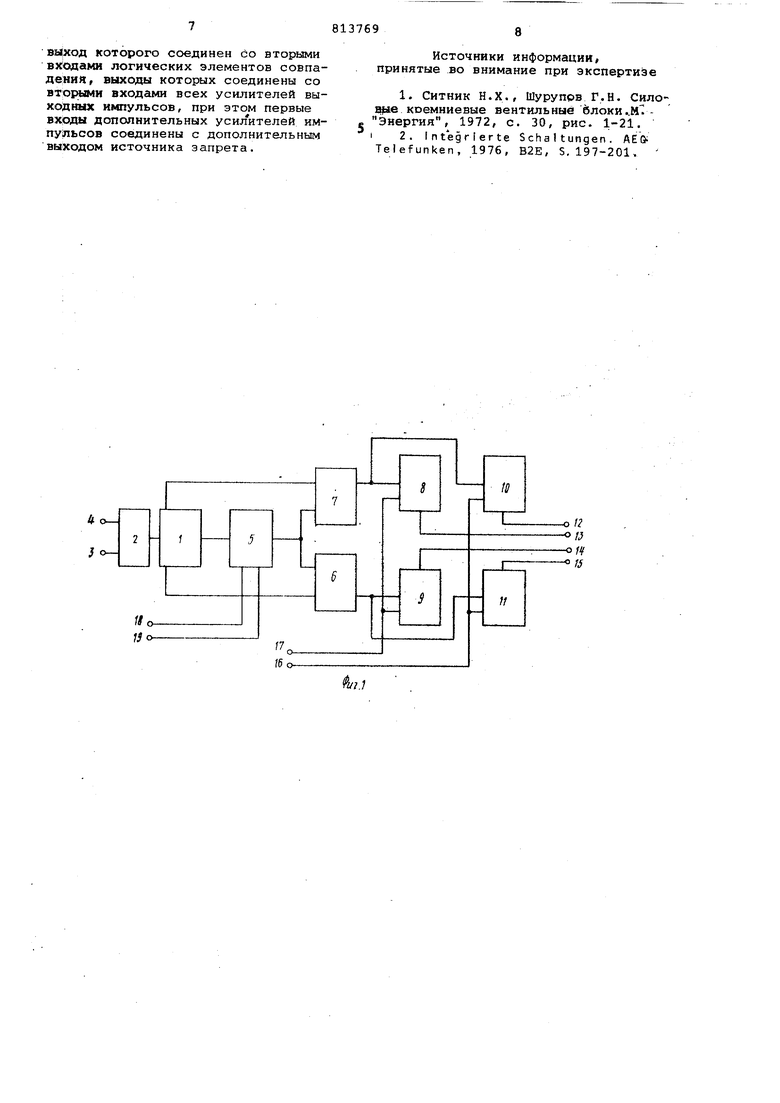

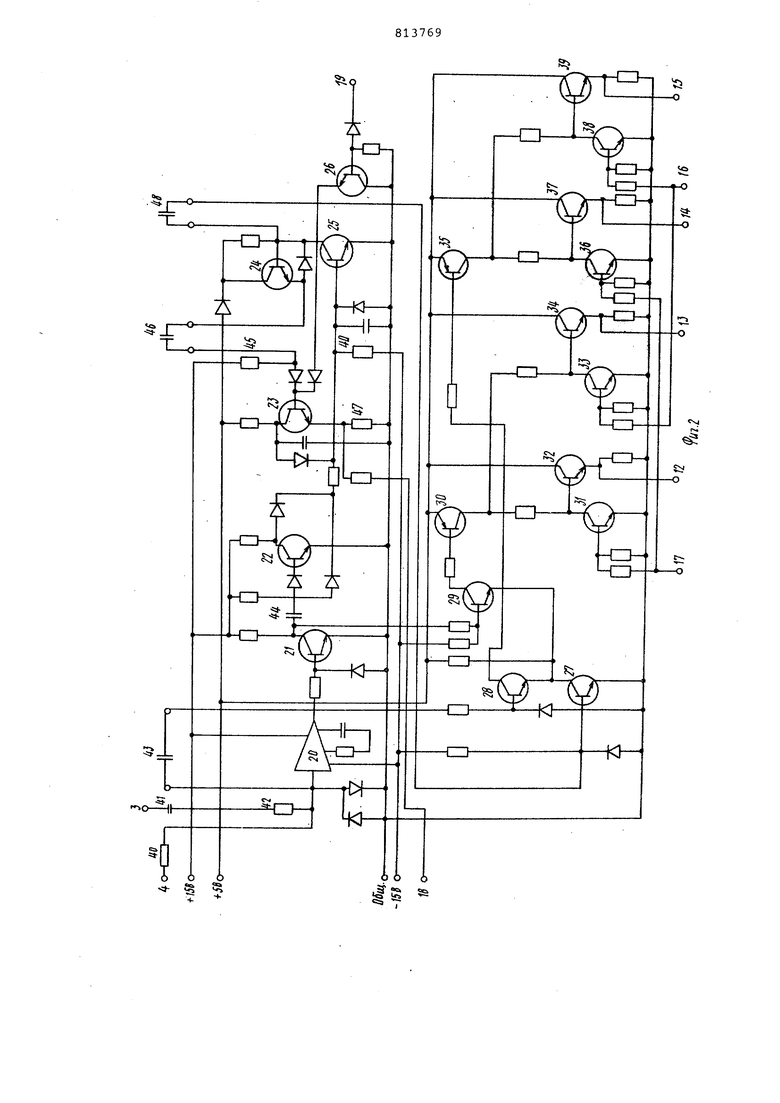

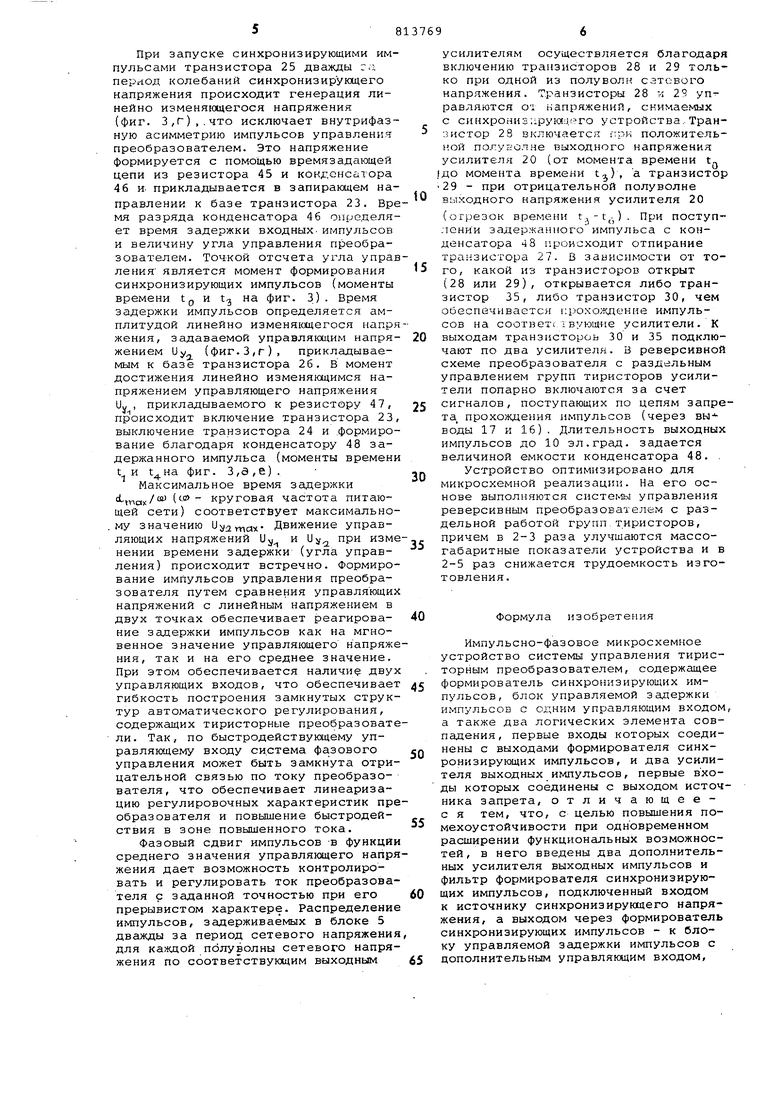

применения данного устройства преобрЬэователямн для нереверсивного привода. Кроме того,сигнал, управляющий формирователем синхронизирующих импульсов/ имеет мощность,что приводит к сложности и неэкономичнос ти генератор а управляющего сигна;та, а управление преобразователем от данной схемы не обеспечивает линейность статической регулировочной характеристики преобразователя,что ограничивает глубину регулирования электропривода в связи с невозможностью получения идентичного качест ва процесса регулирования во всем диапазоне изменения угла управления при этом не обеспечивается симметри управляющих импульсов при управлени многофазным выпрямителем. Таким образом, указанные недостатки приводят к .ограничению области применения и fc усложнению систем, в которы устройство применяется. Цель изобретения - повышение помехоустойчивости при одновременном расширении Функциональных возможнос тей . Поставленная цель достигается те что в импульсно-фазовое микросхемное устройство системы управления тиристорным преобразователем, содер жащее формирователь синхронизирующих импульсов, блок.управляемой задержки импульсов с одним управляющим входом, а также два логических элемента совпадения, первые входы которых соединены с выходами формирователя синхронизирующих импульсов и два усилителя выходных импульсов, первые входы которых соединены с выходом источника запрета,- введены два дополнительных усилителя выходных импульсов и фильтр формирования синхронизирующих импульсов, подключенный входом к источнику синхронизирующего напряжения, а выходом через формирователь синхронизирующих импульсов - к блоку управляемой задержки импульсов с дополнительным управляющим входом, выход которого соединен со вторыми входами логичес ких элементов совпадения, выходы ко торых- соединены со вторыми входа;ми всех усилителей выходных импульсов, при этом первые входы дополнительны усилителей импульсов соединены с до полнительным выходом источника запрета . На фиг. 1 представлена функциональная схема микросхемного устройства; на фиг. 2 - принципиальная сх ма микросхемного устройства на фиг. 3 - временные диаграммы работы устройства. Устройство содержит формировател 1синхронизирующих импульсов,фильтр 2формирователя, подключенный выводами 3 и 4 к источнику напряжения синхронизации, а выходом через форм рователь 1 - к блоку 5 управляемой задержки импульсов, реализувощему фазовый сдвиг. Блок 5 управляемой задержки импульсов через элементы И 6 и 7 совпадения связан с выходны1 1и усилителями 8, 9, 10 и 11, соединенными попарно параллельно. Выходы усилителей подключены к зажимам 12, 13, .14 и 15, а выводы 16 и 17 - к источн ику запсета прохождения выходных импульсов. Блок 5 управляемой задержки импульсов снабжен управляющими входами 18 и 19. Формирователь 1 си - хрон11знрующих импульсов реализуется (фиг. 2) на операционном усилителе 20 и транзисторах 21 и 22, реализующий фазовый сдвиг блок 5 управляемой задержки импульсов - на транзисторах 23, 24, 25 и 26, а элементы И 6 и 7 содержат общий транзистор 27 и транзисторы 28 и 29. Усилители 8 и 10 выполняют на транзисторах 30, 31, 32 и 30, 33, 34, соответственно усилители 9 и 11 на транзисторах 35, 36, 37 и 35, 38, 39. Устройство работает следующим образом. Операционный усилитель 20 с резисторами 40 и 42 и конденсаторами 41и 43 образует фильтр 2 формирователя синхронизирующих импульсов.Напряжения синхронизации одной фазы сети, инверсные по знаку, подаются на выводы 3 и 4 и через входные ветви операционного усилителя 20 поступают на,его вход, где происходит их алгебраическое суммирование. Прямое напряжение подается через резистор 40, а инверсное напряжение - через последовательно включенные резистор 42и конденсатор 41, предназначенные для выделения высокочастотных составляющих, благодаря наложению которых на прямое напряжение происходит компенсация искажений в полезном синхронизирующем напряжении. Усилитель 20 охвачен емкостной обратной связью и в целом совместно со входными ветвями образует фильтрующее звено второго порядка. Выходное напряжение усилителя 20 И1у1еет трапецеидальную форму (фиг. 3,о(), благодаря чему исключается влияние искажений, действующих выше порога срабатывания усилителя 20.-Отрицательная полуволна выходного напряжения усилителя 20 преобразуется транзистором 21 в напряжение прямоугольной , которое дифференцируется конденсатором 44. Полученные в моменты времени tg и tgj, соответствующие переходу через напряжения на выходе усилителя 20, узкие импульсы поступают на вход выполненного на основе задержанного г.1ультивибратора блока 5 управляемой задержки импульсов, осуществляющего Лазовый сдвиг (фиг. 3, б,в). При запуске синхронизирующими им пульсами транзистора 25 дважды га период колебаний синхронизирующего напряжения происходит генерация линейно изменяющегося напряжения (фиг. 3,г),.что исключает внутрифаз ную асимметрию импульсов управления преобразователем. Это напряжение формируется с помощью времязадающей цепи из резистора 45 и кокдонсагора 46 и прикладывается в запирающем на правлении к базе транзистора 23. Вр мя разряда конденсатора 46 определя ет время задержки входных-импульсов и величину угла управления преобразователем. Точкой отсчета угла упра ления является момент формирования синхронизирующих импульсов (моменты времени t и t на фиг. 3). Время задержки импульсов определяется амплитудой линейно изменяющегося напр жения, задаваемой управляющим напря жением (фиг.3,г), прикладываемым к базе транзистора 26. В момент достижения линейно изменяющимся напряжением управляющего напряжения Uy , прикладываемого к резистору 47, происходит включение транзистора 23 выключение транзистора 24 и .формиро вание благодаря конденсатору 48 задержанного импульса (моменты времени t и t, фиг. 3,а,е). Максимальное время задержки ( круговая частота питающей сети) соответствует максимально, му значению . Движение управляющих напряжений U, и при изме нении времени задержки (угла управления) происходит встречно. Формирование импульсов управления преобразователя путем сравнения управляющих напряжений с линейным напряжением в двух точках обеспечивает реагирование задержки импульсов как на мгновенное значение управляющего напряже ния, так и на его среднее значение. При этом обеспечивается наличие двух управляющих входов, что обеспечивает гибкость построения замкнутых структур автоматического регулирования, содержащих тиристорные преобразовате ли. Так, по быстродействуюцему управляющему входу система фазового управления может быть замкнута отрицательной связью по току преобразователя, что обеспечивает линеаризацию регулировочных характеристик пре образователя и повьпление быстродействия в зоне повыщенного тока. Фазовый сдвиг импульсов -в функции среднего значения управляющего напря жения дает возможность контролировать и регулировать ток преобразователя с заданной точностью при его прерывистом характере. Распределение импульсов, задерживаемых в блоке 5 дважды за период сетевого напряжения для каждой полуволны сетевого напряжения по соответствующим выходным усилителям осуществляется благодаря включению транзисторов 28 и 29 только при одной из полуволн сатсвого напряжения. Транзисторы 28 к 29 управляются О1 напряжений, снимаемых с синхрониз;1ру ац го устройства,. Транзистор 28 включается ггри положительной no.ryiio.nae выходного напряжения усилителя 20 (от момента времени tg ДО момента времени t), а транзистор 29 - при отрицательной полуволне выходного напряжения усилителя 20 (отрезок времени t.-t.J. При поступлении задержанного импульса с конденсатора ч8 происходит отпирание транзистора 27. В зависимости от того, какой из транзисторов открыт (28 или 29), открывается либо транзистор 35, либо транзистор 30, чем обеспечивается проходдение импульсов на соответ1 1 вующ-ие усилители. К выходам транзисторов 30 и 35 подключают по два усилителя. В реверсивной схеме преобразователя с раздельным управлением групп тиристоров усилители попарно включаются за счет сигналов, поступающих по цепям запрета, прохождения импульсов (через выводы 17 и 16). Длительность выходных импульсов до 10 эл.град. задается величиной емкости конденсатора 48. . Устройство оптимизировано для микросхемной реализации. На его основе выполняются системы управления реверсивным преобразователем с раздельной работой групп.тиристоров, причем в 2-3 раза улучшаются массогабаритные показатели устройства и в 2-5 раз снижается трудоемкость изготовления. Формула изобретения Импульсно-фазовое микросхемное устройство системы управления тиристорным преобразователем, содержащее формирователь синхронизирующих импульсов, блок управляемой задержки импульсов с одним управляющим входом, а также два логических элемента совпадения, первые входы которых соединены с выходами формирователя синхронизирующих импульсов, и два усилителя выходных импульсов, первые входы которых соединены с выходом источника запрета, отличающеес я тем, что, с целью повьпления помехоустойчивости при одновременном расширении функциональных возможностей, в него введены два дополнительных усилителя выходных импульсов и фильтр формирователя синхронизирующих импульсов, подключенный входом к источнику синхронизирукщего напряжения, а выходом через формирователь синхронизирующих импульсов - к блоку управляемой задержки импульсов с дополнительным управляющим входом.

В14ХОД которого соединен со вторыми вх эдами логических элементов совпадения, выходы которых соединены со вторыми входами всех усилителей выхоД(ШХ импульсов, при этом первые входы дополнительных усилителей иМпульсов соединены с дополнительным выходом источника запрета.

Источники информации, принятые во внимание при эксперти:зе

1. Ситник Н.Х., Шурупрв Г.Н. СилоEpie коемниевые вентильные блоки..М7 Энергия, 1972, с. 30, рис, 1-21. I 2. Integrierte Schaltungen. АЕ Telefunken, 1976, В2Е, S. 197-201.

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ управления трехфазным тиристорным преобразователем | 1990 |

|

SU1815769A1 |

| Реверсивный вентильный двигатель | 1979 |

|

SU826513A1 |

| Формирователь импульсов для управления тиристорами | 1990 |

|

SU1760610A1 |

| Устройство для управления мощныммногофазным тиристорным преобразова-телем | 1973 |

|

SU508891A1 |

| Одноканальное устройство для управления вентильным преобразователем | 1984 |

|

SU1297192A1 |

| Устройство для управления компенсированным выпрямительно-инверторным преобразователем электроподвижного состава | 1987 |

|

SU1468791A1 |

| УСТРОЙСТВО ИМПУЛЬСНО-ФАЗОВОГО УПРАВЛЕНИЯ | 1999 |

|

RU2160957C2 |

| Устройство для управления грузоподъемным электромагнитом | 1990 |

|

SU1817144A1 |

| Устройство для управления многофазным тиристорным преобразователем | 1976 |

|

SU650200A1 |

| Устройство для фазового управления сварочным током контактных машин | 1978 |

|

SU766789A1 |

4 }

Авторы

Даты

1981-03-15—Публикация

1978-12-08—Подача