(54) УСТРОЙСТВО ФОРМИРОВАНИЯ МНОГОСТУПЕНЧАТОГО КВАЗИСИНУСОИДАЛЬНОГО ТРЕХФАЗНОГО НАПРЯЖЕНИЯ

жение-частота, счетчик импульсов, дешифратор и формирователи по числу фаз, дополнительный счетчик, дополнительный дешифратор, триггеры по количеству фаз формируемого напряжения и дополнительные ключи, количество которых определяется фазностью формируемого напряжения, причем выход каждого формирователя подключен к суммируюш,ей точке каждой фазы через соответствующие дополнительные ключи, цепи управления которых связаны с дополнительным дешифратором, управляюш,ие также через соответствующие триггеры дополнительными выходными ключами, а вход дополнительного дешифратора связан со счетчиком через дополнительный счетчик 4

Недостаток устройства - преувеличенный диапазон формирователей напряжения. Так, в нем имеются три диапазона формирователей напряжения отдельных участков синусоиды от 0,00им до 0,86UAA, от 0,86UM до 0,ООиллИ от 0,86U до 1,OOU,.

Другим недостатком устройства является асимметрия его выходного напряжения, вызванная применением инвертора для формирования одной полярности выходного напряжения, что приводит к изменению фазы и амплитуды напряжения относительно входного напряжения, а также другой полярности выходного напряжения, где формирователь подключается прямо к выходу.

Цель изобретения - улучшение качества выходного напряжения и упрощение устройства.

Поставленная цель достигается тем, что устройство формирования многоступенчатого квазисинусоидального трехфазного напряжения, содержащее регулируемый генератор тактовой частоты, выход которого подключен ко входу распределителя импульсов, а выход распределителя импульсов связан со входом Т-триггера, с распределителями потенциалов по числу выходных фаз и со входами цифроаналоговых преобразователей числом, равных числу формируемых участков синусоиды причем последние связаны ключами двусторонней проводимости с задатчиком уровня постоянного напряжения и с инвертирующим усилителем с единичным усилением, дополнительно снабжено реверсивными двоичными счетчиками двоичного кода и RS-триггером, причем выходы реверсивных двоичных счетчиков подключены ко входам цифроанало говых преобразователей, а их входы - к выходам распределителя импульсов и RSтриггера, вход которого подключен к выходу распределителя импульсов.

Улучшение качества выходного напряжения достигается тем, что формирование выходного напряжения обеих полярностей осуществляется в одинаковых условиях, т. е. уже на входе цифроаналогового преобразователя подключается необходимая полярность постоянного напряжения и, следовательно, не имеется причин для возникновения асимметрии, присущей известному устройству.

В предлагаемом устройстве сокращены диапазоны участков формируемой синусоиды, т. е. каждый, цифроаналоговый преобразователь формирует определенные уровни, которые не формируют другие цифроаналоговые преобразователи.

Применение цифроаналоговых преобразователей двоичного кода позволяет сократить число ключей двусторонней проводимости и число резисторов, т. е. для формирования каждой ступени аналоговой величины включается один или несколько ключей двусторонней проводимости.

Следует отметить, что трехфазные системы симметричного синусоидального напряжения характеризуются наличием в каждый момент времени только одного значения напряжений каждой фазы в диапазонах от 0,0им до 0,5UM, от 0,5UM до 0,86UM, от 0,8бимдо 1,00им,

где максимальное (амплитудное) значение выходного напряжения устройства. Переключение второго диапазона меняется через л/6, а первого и третьего через периода выходного напряжения.

Формируется только одно значение ступенчато-аппроксимированного синусоидального напряжения. Достигается это разбиванием полного диапазона значений выходного напряжения на три поддиапазона, согласно которым устройство состоит из трех

разных функциональных формирователей, работающих с частотой, в три раза больщей выходной генерируемой частоты, а именно, первый полупериод формирует от 0,0им до 0,5 Цд, от 0,5 UM до 0,0 UM и второй от 0,86 УЛА до 0,5 UM и от 0,5 Uw до 0,86 UM,

третий от 0,86 Uw до - 1,0 UM и от - 1,OUM до - 0,86 UM, а выходы функциональных формирователей через ключи двусторонней проводимости подключаются к выходу устройства в следующем порядке: первый и

третий формирователь с обратной последовательностью чередования переключения фаз и частотой в 6 раз больше выходной частоты устройства, а второй с прямой последовательностью чередования переключения фаз и частотой в 12 раз больше выходной частоты устройства.

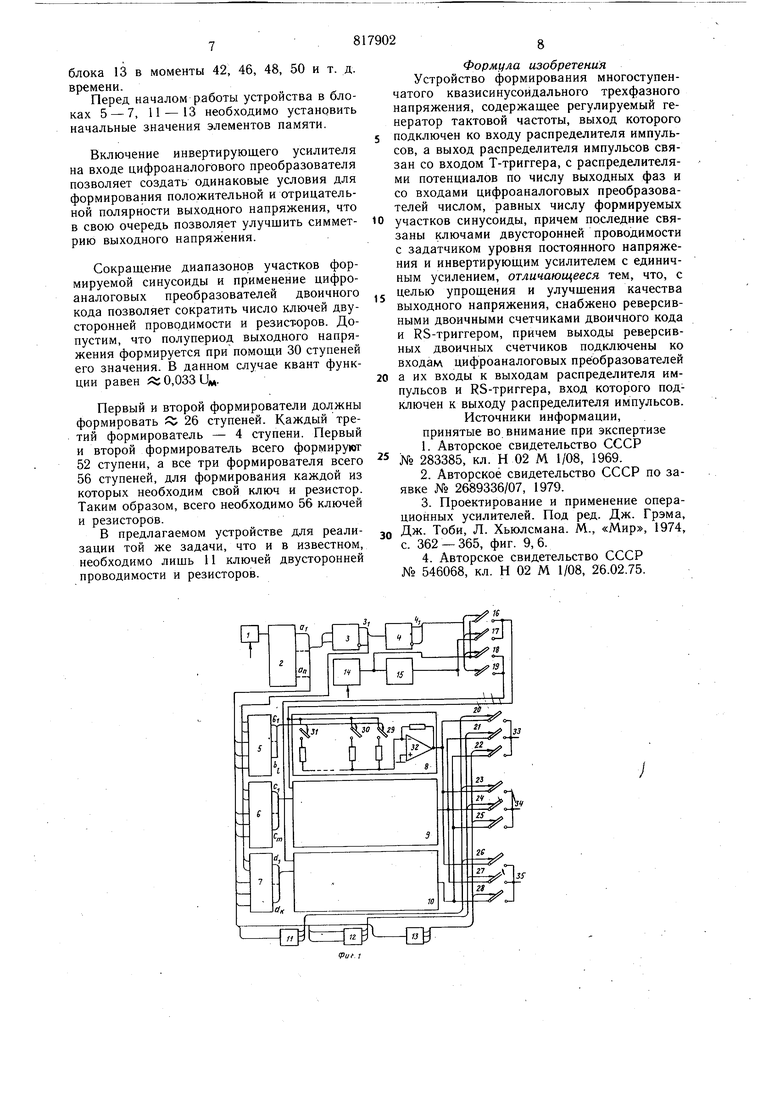

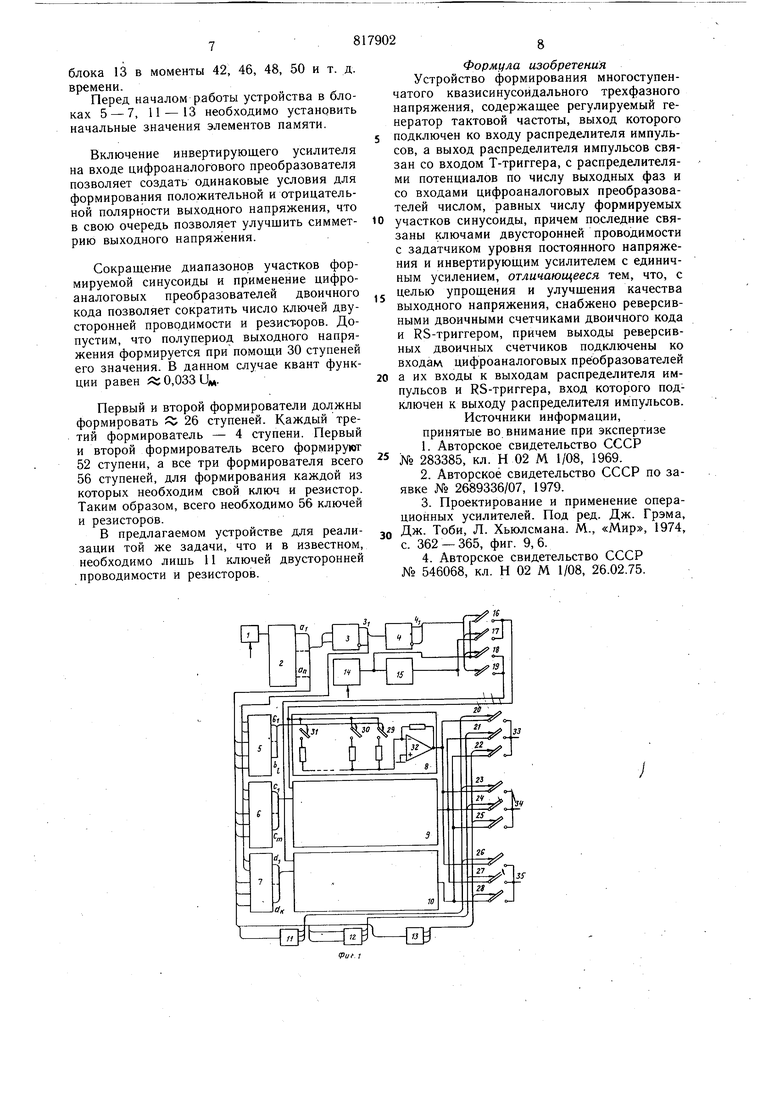

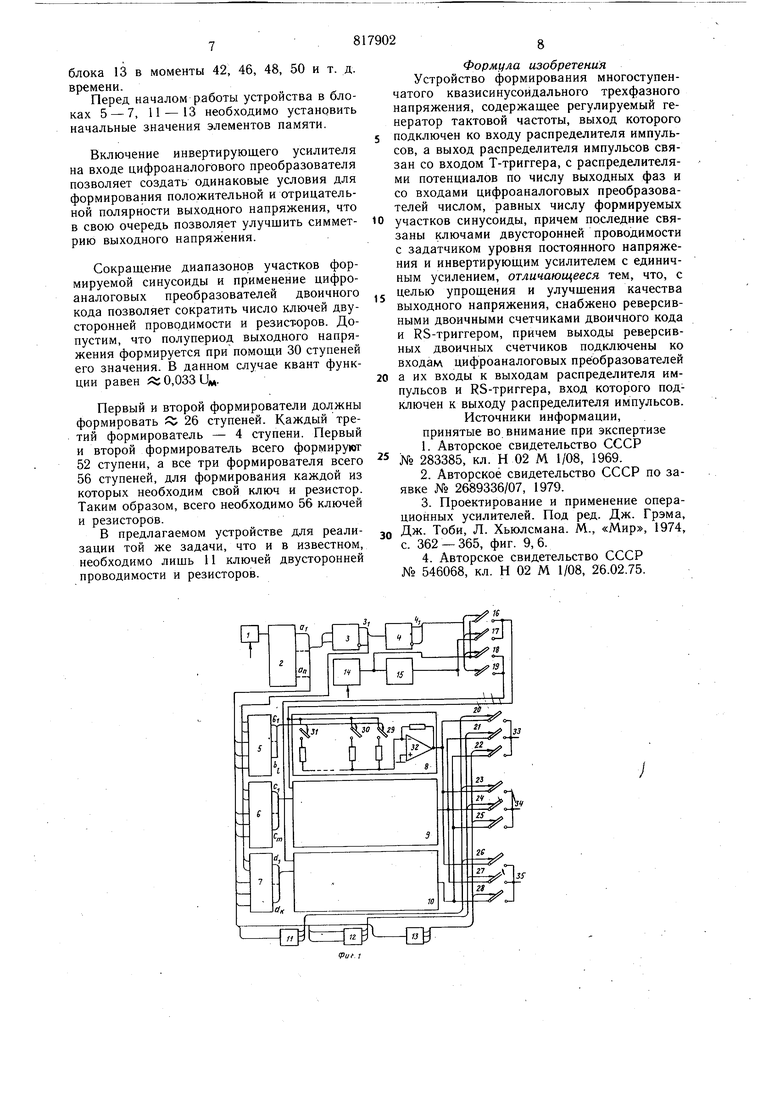

На фиг. 1 изображена блок-схема предлагаемого устройства; на фиг. 2 приведены временные диаграммы работы устройства. Схема содержит регулируемый генератор 1 тактовой частоты, распределитель 2 импульсов, RS-триггеры 3, Т-триггер 4, реверсивный двоичный счетчик 5, вырабатывающий двоичный код функции от 0,0 UM до 0,5 UM, реверсивный двоичный счетчик 6, вырабатывающий двоичный код функции

от 0,5 UM до 0,86 U/VV реверсивный двоичный счетчик 7, вырабатывающий двоичный код функции от 0,86 UM до UOUw, цифроаналоговый преобразователь 8, формирующий

участок синусоиды от 0,0 до 0,5 U, цифроаналоговый преобразователь 9, формирующий участок синусоиды от 0,5 УмДО 0,86 UM, цифроаналоговый преобразователь 10, формирующий участок синусоиды от 0,86 ОА до 1,0 UM, распределители 11 - 13 потенциалов с тремя выходными каналами, осуществляющие подключение блоков 8-10 для формирования выходных напряжений, задатчик 14 уровня постоянного напряжения инвертирующий усилитель 15 с единичным усилением, ключи 16 - 31 двусторонней проводимости, операционный усилитель 32, выход 33 ступенчато-аппроксимированной синусоиды UM sin , выход 34 ступенчатоаппроксимированной синусоиды U/trt(sin wt -i+ ), выход 35 ступенчато-аппроксимированной синусоиды LU(sin cot Ч-), R, 2К., весовые резисторы, вде Ы - число выходов двоичного счетчика 5, R о-резистор обратной связи, выходное напряжение 36 цифроаналогового преобразователя 8, выходное напряжение 37 цифроаналогового преобразователя 9, выходное напряжение 38 цифроаналогового преобразователя 10, аппроксимированное синусоидальное выходное напряжение 39 фазы 33, аппроксимированное синусоидальное выходное напряжение 40 фазы 34, аппроксимированное синусоидальное напряжение 41 фазы 35, моменты 42 - 56 времени опрокидывания триггера в блоке 3, промежуток времени 57 - 58, когда имеется единица в- канала распределителя импульсов, промежуток времени 59, 60, когда имеется единица в первом канале распределителя импульсов, выходное напряжение 3 RS-триггера на единичном выходе, выходное напряжение 4i Т-триггера на единичном выходе.

Устройство работает следующим образом Блоки 5 - 7 вырабатывают двоичные коды отдельных участков синусоиды, которые при помощи блоков 8-10 преобразуются в аналоговые величины напряжений. Выходы блоков 8-10 к выходам 33-35 устройства подключаются при помощи ключей двусторонней проводимости в следующем порядке: выход блока 8 к выходам 33, 35, 34, 33 и т. д. устройства; выход блока 9 к выходам 35, 33, 34, 35 и т. д. устройства; выход блока 10 к выходам 34, 33, 35, 34 и т. д. устройства.

Напряжения с выходов 33 -г 35 устройства соответствуют позициям 39 - 41. Частоту сдвига единицы в выходных каналах блока 2 определяет выходная частота блока 1. Блок 2 имеет число каналов п, равных числу временных интервалов на участке аргумента л/З, где п - любое четное число. Наличие единицы в конкретном выходном канале блока 2 определяет конкретный промежуток времени существования отдельного участка функции. Например, когда единица

.

она определяет пронаходится в канале

ПС1Л1 ДГ1 1 Л D nClf/J -, П.С1 V llj-C/litVI ЛС I

межуток времени 57 - 58 существования

функции (фиг. 2). Когда единица находится в первом канале, она определяет промежуток времени 59 - 60 существования функции. Изменение состояния блока 3 происходит в моменты времени 42 - 46 и т. д. В перечисленных моментах времени единица находится в первом или каналах блока 2 и, следовательно, они подключены к информационным выходам блока 3.

Временная диаграмма сигнала единичного выхода 31 блока 3 приведена на фиг. 2. При помощи блока 3 устанавливаются режимы сложения или вычитания блоков 5 -7. Если на единичном выходе блока 3 единица, тогда блоки 5 и 7 в режиме сложения, а блок 6 в режиме вычитания. Когда на единичном выходе блока 3 нуль, тогда блоки 5, 7 в режиме вычитания, а блок 6 в режиме сложения. Смена двоичного кода в блоках 5 - 7 происходит только в момент времени, когда соответствующий канал блока 2 подключен ко счетному входу блоков 5 - 7. Выходные разряды блоков 5 - 7 подключены к управляющим цепям ключей двусторонней проводимости. блоков 8-10. На выходе блока 14 устанавливается уровень постоянного напряжения, определяющий амплитудное значение выходного напряжения, которое при помощи блока 15 инвертируется для получения постоянного напряжения той же величины, но противоположного знака. При помощи ключей 16 или 17 выходы блоков 14 или 15 подключаются к выходам блоков 8 и 9, а при помощи ключей 18 или 19 выходы блоков 14 или 15 подключаются к выходу блока 10. Выход блока 3 подключен ко счетному входу блока 4.

Временная диаграмма сигнала единичного выхода 4 приведена на фиг. 2.

Выходы блока 4 к управляющим цепям 16-19 подключены таким образом, что ко входам блоков 8, 9 подключено постоянное напряжение- одной полярности, а к входу блока 10 - постоянное напряжейие противоположного знака. Блоки 11 - 13 каждый имеют три выходных канала. Выходные каналы блока 11 подключены к управляющим цепям 20, 23 и 26, выходные каналы блока 12 подключены к управляющим цепям 21, 24, 27 и выходные каналы блока 13 подключены к управляющим цепям 22, 25, 28. Ко входу блока 11 подключен выходной каналЦ- блока 2, который производит сдвиг единицы .в выходных каналах блока 11 в моменты времени 43, 45, 47, 49 и т. д.

Ко входу блока 12 подключены первый и выходные каналы блока 2, которые производят сдвиг единицы в выходных каналах блока 12 в моменты 42-45 времени и т. д.

Ко входу блока 13 подключен первый выходной канал блока 2, который производит сдвиг единицы в выходных каналах

блока 13 в моменты 42, 46, 48, 50 и т. д. времени.

Перед началом работы устройства в блоках 5 - 7, 11 - 13 необходимо установить начальные значения элементов памяти.

Включение инвертирующего усилителя на входе цифроаналогового преобразователя позволяет создать одинаковые условия для формирования положительной и отрицательной полярности выходного напряжения, что в свою очередь позволяет улучшить симметрию выходного напряжения.

Сокращение диапазонов участков формируемой синусоиды и применение цифроаналоговых преобразователей двоичного кода позволяет сократить число ключей двусторонней проводимости и резист-оров. Допустим, что полупериод выходного напряжения формируется при помощи 30 ступеней его значения. В данном случае квант функции равен Л; 0,033 UMПервый и второй формирователи должны формировать f 26 ступеней. Каждый третий формирователь - 4 ступени. Первый и второй формирователь всего формируют 52 ступени, а все три формирователя всего 56 ступеней, для формирования каждой из которых необходим свой ключ и резистор. Таким образом, всего необходимо 56 ключей и резисторов.

В предлагаемом устройстве для реализации той же задачи, что и в известном, необходимо лишь 11 ключей двусторонней проводимости и резисторов.

Формула изобретения Устройство формирования многоступенчатого квазисинусоидального трехфазного напряжения, содержащее регулируемый генератор тактовой частоты, выход которого

подключен ко входу распределителя импульсов, а выход распределителя импульсов связан со входом Т-триггера, с распределителями потенциалов по числу выходных фаз и со входами цифроаналоговых преобразователей числом, равных числу формируемых

участков синусоиды, причем последние связаны ключами двусторонней проводимости с задатчиком уровня постоянного напряжения и инвертирующим усилителем с единичным усилением, отличающееся тем, что, с

целью упрощения и улучшения качества выходного напряжения, снабжено реверсивными двоичными счетчиками двоичного кода и RS-триггером, причем выходы реверсивных двоичных счетчиков подключены ко входам цифроаналоговых преобразователей

а их входы к выходам распределителя импульсов и RS-триггера, вход которого подключен к выходу распределителя импульсов.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 283385, кл. Н 02 М 1/08, 1969.

2.Авторское свидетельство СССР по заявке № 2689336/07, 1979.

3.Проектирование и применение операционных усилителей. Под ред. Дж. Грэма,

Дж. Тоби, Л. Хьюлсмана. М., «Мир, 1974, с. 362 - 365, фиг. 9,6.

4.Авторское свидетельство СССР № 546068, кл. Н 02 М 1/08, 26.02.75.

Г

41

-

75 i/j 4fl Ц5 46 41 48 f3 50 51 5Z «Jf ,-, S3 54 Jf Sf

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования много-СТупЕНчАТОгО КВАзиСиНуСОидАльНОгОТРЕХфАзНОгО НАпРяжЕНия | 1978 |

|

SU809437A1 |

| Частотно-регулируемый электропривод с широтно-импульсной модуляцией | 1982 |

|

SU1310987A1 |

| Скважинный инклинометр | 1990 |

|

SU1721225A1 |

| ЦИФРОВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ ФАЗОМЕТР | 1973 |

|

SU361447A1 |

| Устройство для передачи и приема информации | 1986 |

|

SU1425753A1 |

| Устройство для управления преобразователем частоты с непосредственной связью | 1983 |

|

SU1127070A1 |

| Способ управления непосредственным преобразователем частоты | 1988 |

|

SU1599954A1 |

| Устройство для управления преобразователем частоты с непосредственной связью | 1981 |

|

SU997227A1 |

| Устройство для формирования @ -фазной системы напряжений с числом фаз 2 @ | 1985 |

|

SU1358052A1 |

| Устройство для управления преобразователем | 1985 |

|

SU1246300A1 |

Авторы

Даты

1981-03-30—Публикация

1979-01-09—Подача