жение сети 15 поступает на вход вто рого аналого-цифрового блока 10, где преобразуется в 2. . Код Z отличается от программного кода на величину не более заданной. На выход блока 2 контроля разности кодов поступает код Z . При нулевом значении кода У ,поступающего с выхода первого аиалог о-цифрового блока 8 на вход нуль-органа 12, с выхода последнего подаемся сигнал на обнуляющий вход блока 1 формирования сигнала, пропорционального программному мгновенному значению ступен- чато-аппроксимированной синусоиды, который обнуляется т.е. код, Ч на его вькоде имеет нулевое значение. Таким образом, ликвидируется смещение фазы напряжения, соответствующего программному коду, отноИзобретение относится к электротехнике, а точнее к преобразователям постоянного напряжения в переменное с квазисинусоидальной или ступенчато синусоидальной формой выходного напряжения, и может быть использовано в установках гарантированного питания потребителей переменного тока.

Цель изобретения - расширение фун кциональных возможностей и области применения устройства.

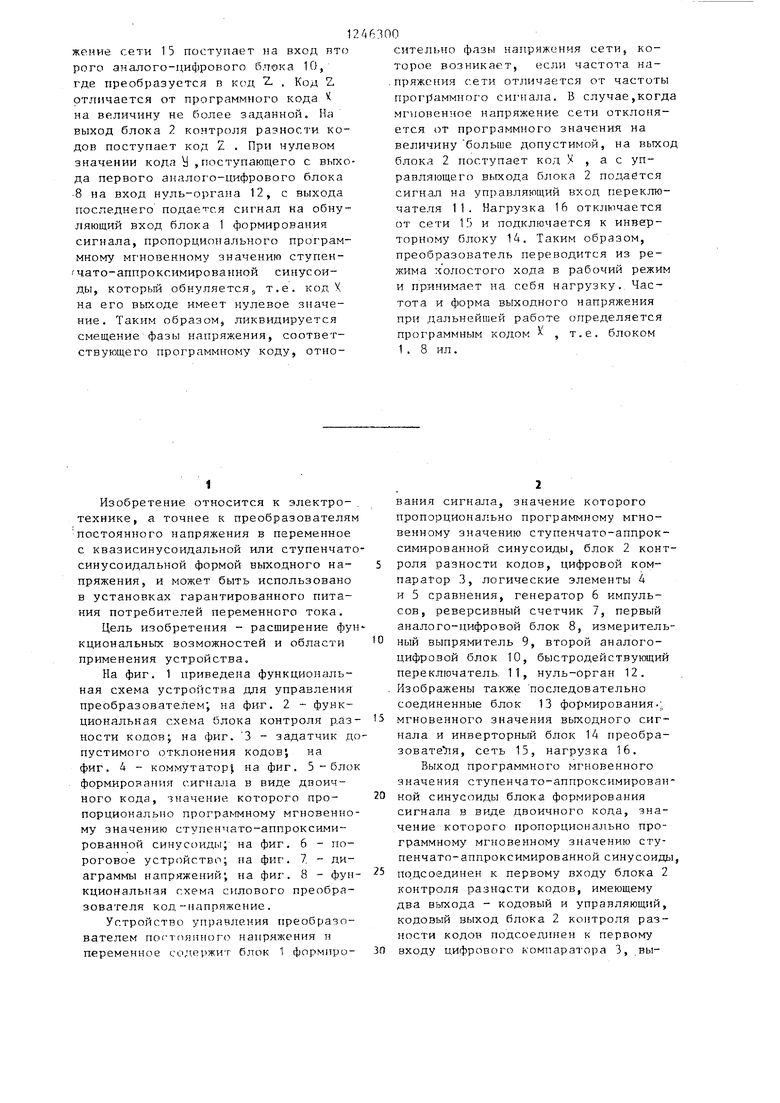

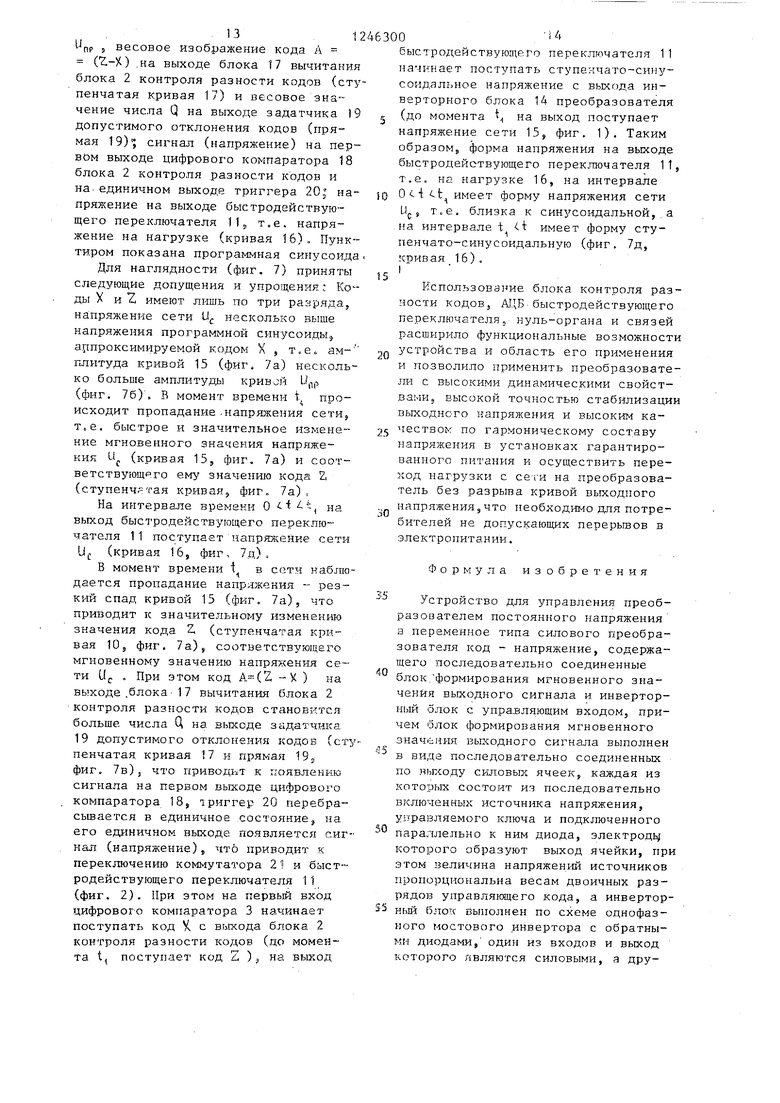

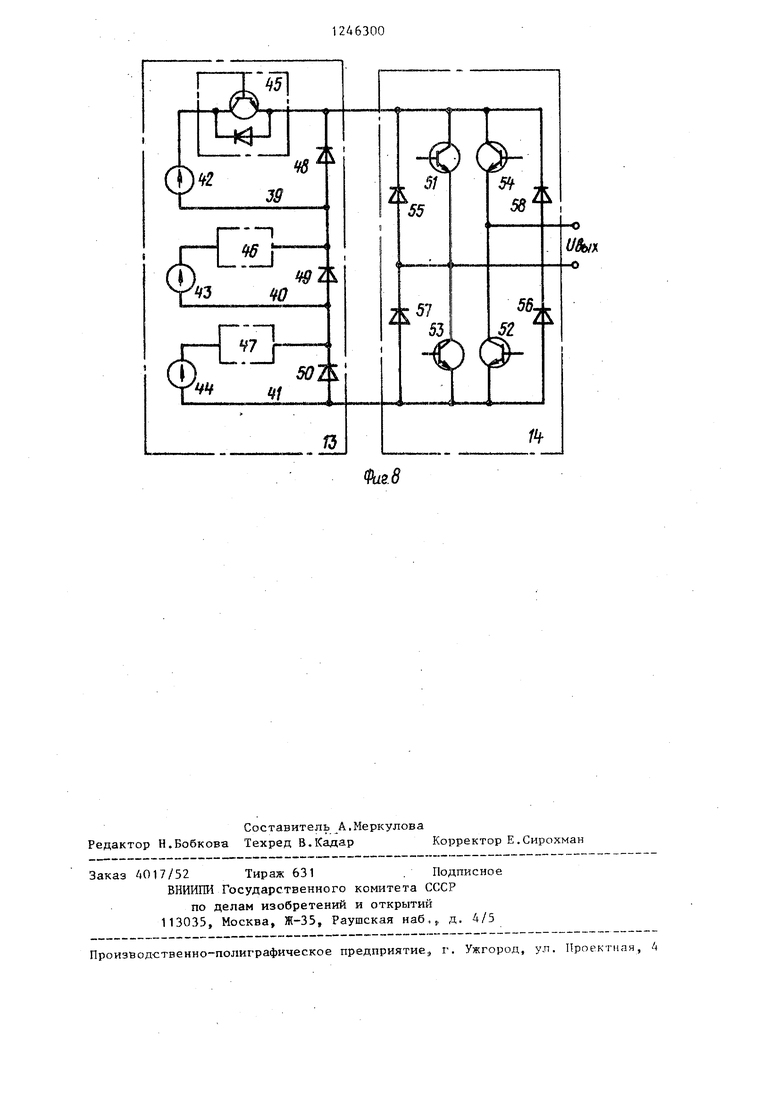

На фиг. 1 приведена функциональная схема устройства ,оля управления преобразователем; на фиг. 2 - функциональная схема блока контроля рлз- ности кодов; на фиг. 3 - задатчик допустимого отклонения кодов , на фиг. 4 - KOMNryTaTopi на фиг. 5 -блок формирования сигнала в виде двоичного кода, значение которого пропорционально программному мгновенному значению ступенчато-аппроксимированной синусоиды; на фиг. 6 - пороговое устр(5йстео; на фиг. 7. - диаграммы напряжений; на фиг. 8 - функциональная схема силового преобразователя код-напряжение.

Устройство управления преобразователем постоянного напряжения в переменное содержит блок 1 формиросительно фазы напряжения сети, которое возникает, если частота на- ,пряжения сети отличается от частоты программного сигнала. В случае,когд мгновенное напряжение сети отклоняется от программного значения на величину больше допустимой, на выхо блока 2 поступает код X , а с управляющего выхода блока 2 подается сигн,ал на управляющий вход переключателя 11. Нагрузка 16 отключается от сети 15 и подключается к инвер- торному блоку 14. Таким образом, преобразователь переводится из режима холостого хода в рабочий режим и принимает на себя нагрузку.. Частота и форма вь ходного напряжения при дальнейшей работе определяется программным кодом , т.е. блоком 1 . 8 ил.

вания сигнала, значение которого пропорциона1 ьно программному мгновенному значению ступенчато-аппроксимированной синусоиды, блок 2 конт- роля разности кодов, цифровой ком- napatop 3, логические элементы 4 и 5 сравнения, resiepaTop 6 импульсов, реверсивный счетчик 7, первый аналого-цифровой блок В, измерительный выпрямитель 9, второй аналого- цифровой блок 10, быстродействующий переключатель. 11, нуль-орган 12. Изображены также последовательно

соединенные блок 13 формирования-;. мгновенного значения выходного сигнала и инверторный блок 14 преобра- зовате Ля, сеть 15, нагрузка 16.

Вы.код программного мгновенного значения ступенчато-аппроксимирован- Ной синусоиды блока формирования сигнала в двоичного кода, значение которого пропорционально программному мгновенному значению ступенчато-аппроксимированной, синусоиды, по.дсоединен к первому входу блока 2 контроля разности кодов, имеющему два выхода - кодовый и управляющий, кодовый выход блока 2 контроля разности кодов подсоединен к первому входу цифрового компаратора 3, вы3

ход приоритета числа на первом де которого подсоединен к первому входу элемента 4 сравнения, а выход приоритета числа на вторим входе - к первому входу элемента 5 сравнь ня к вторым входам элементов 4 и 5 сраз нений подключен генератор 6 импульсов, а выходы элементов Д и 5 сравнения подсоединены к входам (суммирующему и вычитающему) реверсивного счетчика 7, к второму входу цифрового компаратора 3 подсоединен выход первого анало го-цифрового блока 8, вход которого подсоединен к выходу измерительного выпрямителя 9, подключаемого входом к выходу инвбртор- ного блока 14 преобразователя,вход второго аналого-цифрового блока 10 подключается к сети 15, а выход подключен к второму входу блока 2 контроля разности кодов, также к сети 15 подключается один силовой зход быстродействующего переключателя 11, второй силовой вход которого подключается к выходу инверторного блока 14, а управляющий вход соединен с управляющим выходом блока 2 контроля разности кодов, выход быстродействующего пе1зеключателя 11 подключается к нагруз-ке 16, выход первого аналого-цифрового блока 8 подключен к входу Нуль-органа 12, выкод которого подключен к обнуляющему входу блока формирования сигнала, пропорционального программному мгновенному значению ступенчато-аппроксимированной синусоиды, выход реверсивного счетчика 7 подсоединяется к управляю1 им входам соответствующих ключевых элементов блока 13 формирования мгновенного значения выходного сигнала.

Устройство для управления преобразователем работает следующим образом, .

На выходе программного мгновенного -ачения ступенчато-аппроксими- ровр аой синусоиды блока 1 (фиг. 1) формируется код X. , соответствующий мгновенному значению ступенчато-аппроксимированной программной синусо- ,иды. Код X поступает на один вход блока 2 контроля разности кодов, на другой вход которого поступает код .Z с второго аналого-цифрового блока 10; соответствующий м новен- , ному напряжению сети 15. С выхода .блока 2 контроля разности коцов код / или Z поступает на один ЕХОД циф463004

рового компаратора 3, на другой вход которого поступает код У, соответствующий мгновенному значению напряжения на выходе инверторного 5 блока 14, В цифровом компараторе 3 происходит сравнение этих кодов (2) и У вырабатывается команда X(2) d или X(Z)iy . Команда X (2)У 3 виде разрешающего сигнала поступа- 0 ет на вход элемента 4 сравнения, а команда (Z)y - на вход элемента 5 сравнения. В первом случае тактовые импульсы с выхода дополнительного сенератора 6 поступают на сум-- f5 мирующий вход реверсивного счетчика 7, во втором случае - на вычитающий вход реверсивного счетчика 7. Значение управляющего кода, поступающего с выхода реверсивного счетно чика 7 на управляющие.входы блока формирования мгновенного значения выходного сигнала 13, возрастает (во втором случае - убьшает), соответственно возрастает (убывает) 25 мгновенное значение напряжения на выходе блока 13 и инверторного блока 14. Так как напряжение с выхода инверторнбго блока 14 через измерительный выпрямитель 9 поступает 3Q на вход первого аналого-цифрового блока (АЦБ) 8 где преобразуется в код У , то соответственно возраста- ет (убывает) значение кода У до тех пор, пока не сравняются коды X (2) и У , поступающие на входы цифрового коьшаратора 3. Измерительный выпрямитель 9 преобразует переменное напряжение с выхода инверторного блока в однополярные полуволны, прежде Q чем преобразовать аналоговую величину - напряжение в код, т.е. прежде, чем подавать это напряжение на вход АЦБ 8.

В режиме отслеживания напряжение 5 сети 15-через быстродействующий переключатель 11 поступает на нагрузку 16. Также напряжение сети 15 поступает на вход второго АЦБ 10, где преобразуется в код 2 . При этом код 0 2 отличается от программного кода X на величину не более заданной, и на выход 2 блока контроля разности кодов поступает код 2 При нулевом значении кода У , поступающего с 5 выхода первого АЦБ 8 на вход нуль- органа 12, с выхода последнего подается сигнал (импульс) на обнуляющий вход блока 1 формирования сигнала, пропорционального программному мгновенному значению ступенчато-аппроксимированной синусоиды, который обнуляется, т.е. приводится в исходное состояние, когда на его выходе код X имеет нулевое значение. Таким образом, ликвидируется уход или смещение фазы напряжения, соответствующего программному коду отно си- тельно фазы напряжения сети 15, которое неизбежно возникает, если часто- та напряжения сети отличается от частоты программного сигнала (кода X).

В случае, когда мгновенное значение напряжения сети отклоняется от программного значения на величину больше допустимойS т.е. код Z отличается от кода X на величину более заданной, на выход блока 2 контроля разности кодов начинает поступать код У , а с управляющего выхода блока 2 контроля разности кодов подается сигнал на управляющий вход быстродействующего переключателя 11,

Нагрузка 16 отключается от сети 15 и подключается к инверторному блоку 14, т.е. к выходу преобразователя .

Таким образом, преобразователь переводится из состояния холостого хода или ненагруженного резерва в рабочий режим и принимает на себя нагрузку.

Частота и форма выходного напряжения при дальнейшей работе опре деляются кодом XS т.е. блоком формирования сигнала, пропорционального мгновенному значению ступенчато- аппроксимированной синусоиды.

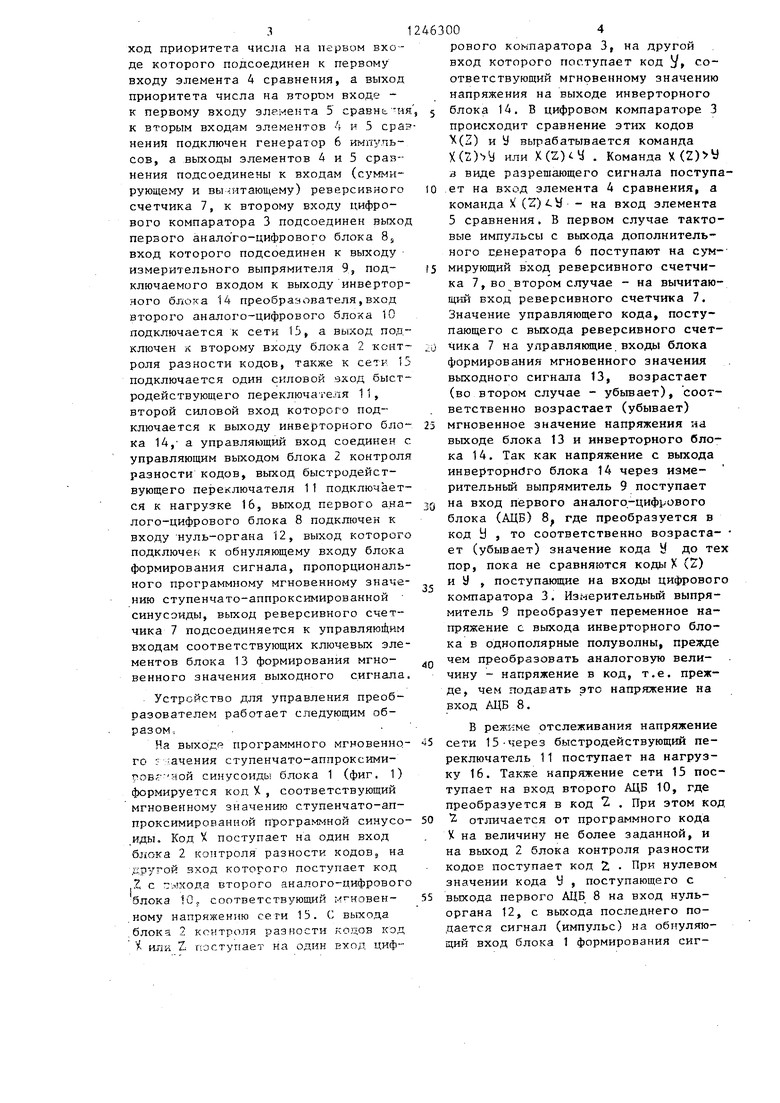

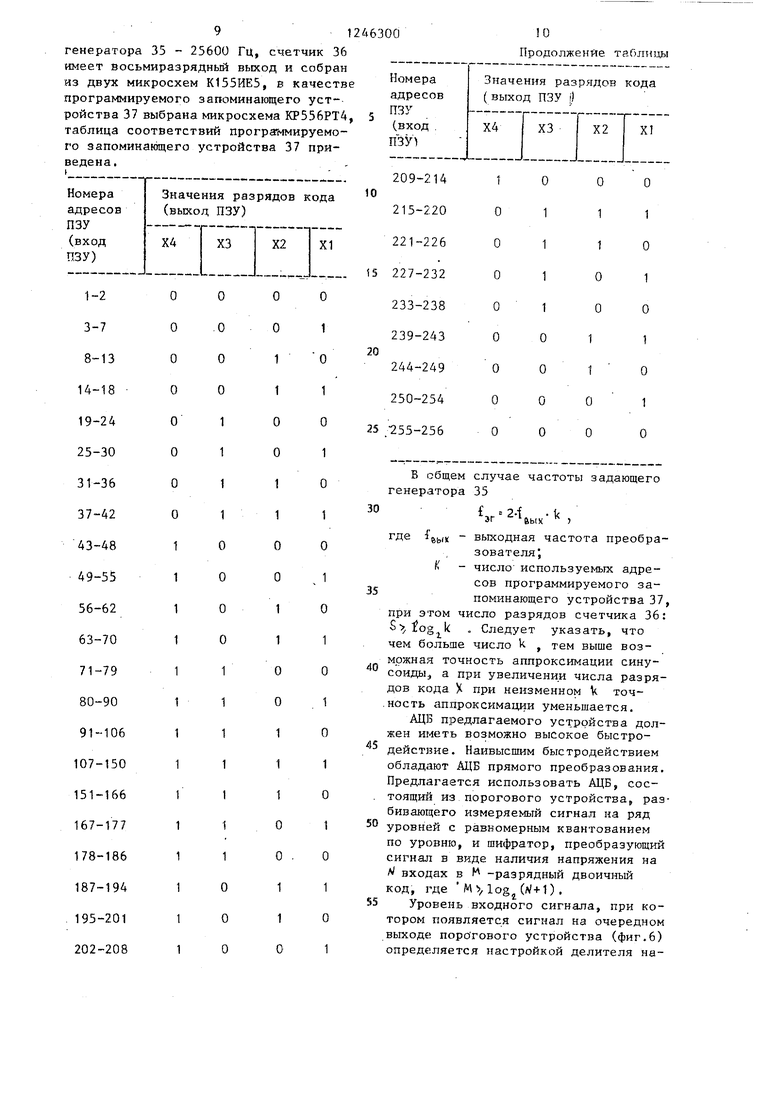

Блок 2 контроля разности кодов (фиг. 2) содержит вычитающий блок 17, цифровой компарато)р 18, задатчик 19 допустимого отклонения кодов, являющийся устройством набора кода, триггер 20, коммутатор 21. Приведены также второй АЦБ 10, цифровой компаратор 3, быстродействующий переключатель 11, блок формирования сигнала, пропорционального мгновенному значению ступенчато- аппроксимированной синусоиды.

Входы блока 17 вычитания, являющиеся входами блока контроля разности кодов, подключены один - к кодовому выходу блока 1, другой - к выходу второго АЦБ 10, выход блока 17 вычитания подключен к одному вхо ду цифрового компаратора 18,, к вто

рому входу KOTopioro подключен за-, датчик 19 допустимого отклонения ко дов, один выход цифрового компаратора 18 подсоединен к единичному вхо- ду триггера 20, -а второй выход - к нулевому входу триггера 20, выход последнего подсоединен к управляющему входу быстродействующего переключателя 11 и к управляюп1ему входу

коммутатора 21, к информационным кодовым входам которого подключены ко-; довый выход блока 1 формирования сигнала пропорционального мгновенному значению ступенчато-аппроксимррованной синусоиды, и второго АЦБ 10, :выход коммутатора 21 подсоединен к одному из ВХОДОВ первого цифрового компаратора 3. ,

Блок 2 контроля разности кодов

работает следующим образом.

С зыхода блока 1 формирования сигнала, пропорционального, мгновенному значению ступенчато-аппроксимированной синусоиды, код V поступает на

первый вход блока 17 вычитания и на первый кодовьш вход коммутатора 21. С выхода второго АЦБ Ю код Z поступает на второй вход блока 17 вычитания и на второй кодовый вход коммутатора 21..

В блоке-17 вычитания происходит постоянное вычитание, т.е. математическое действие (Z - X). С выхода блока 17 вычитания код, равный (Z-X), поступает на один из входов цифрового компаратора 18, на второй вход которого подается код с задатчика 19 допустимого отклонения кодов. В цифровом компараторе 18 происходит постоянное сравнение кода (2. - X) с кодом Q , Если в какой-то момент времени окажется (Z - -Х ) Q , напряжен 1е с выхода компаратора 18 поступает на единичный вход триггера 20, триггер переключается в единичное состояние и с его выхода управляющий сигнал в |Виде напряжения поступает на вход коммутатора 2.1 и на управляющий вход быстродействующего переключателя 11. На вьгх:од коммутатора 21 проходит код У, поступающий с выхода блока 1 на первый кодовый вход коммутатора 21.

В том случае, когда (Z -V ) iQ , разрешающий сигнал в виде напряжения с выхода цифрового компаратора 18 поступает на нулевой вход триггера 20, который находится в нулевом состояний. При этом управляющее напря жение на коммутатор 21 и быстродействующий переключатель 11 не поступает на вход коммутатора 21 проходит код Z, поступающий с выхода второго АЦБ 10 на второй кодовый вход коммутатора 2 1 .

Входящий в состав блока контроля разности кодов блок 17 вычитания может быть построено на основе микросхемы К155ИПЗ В качестве цифрового компаратора 18 может применяться микросхема 533СП1 - схема сравнения двух чисел.

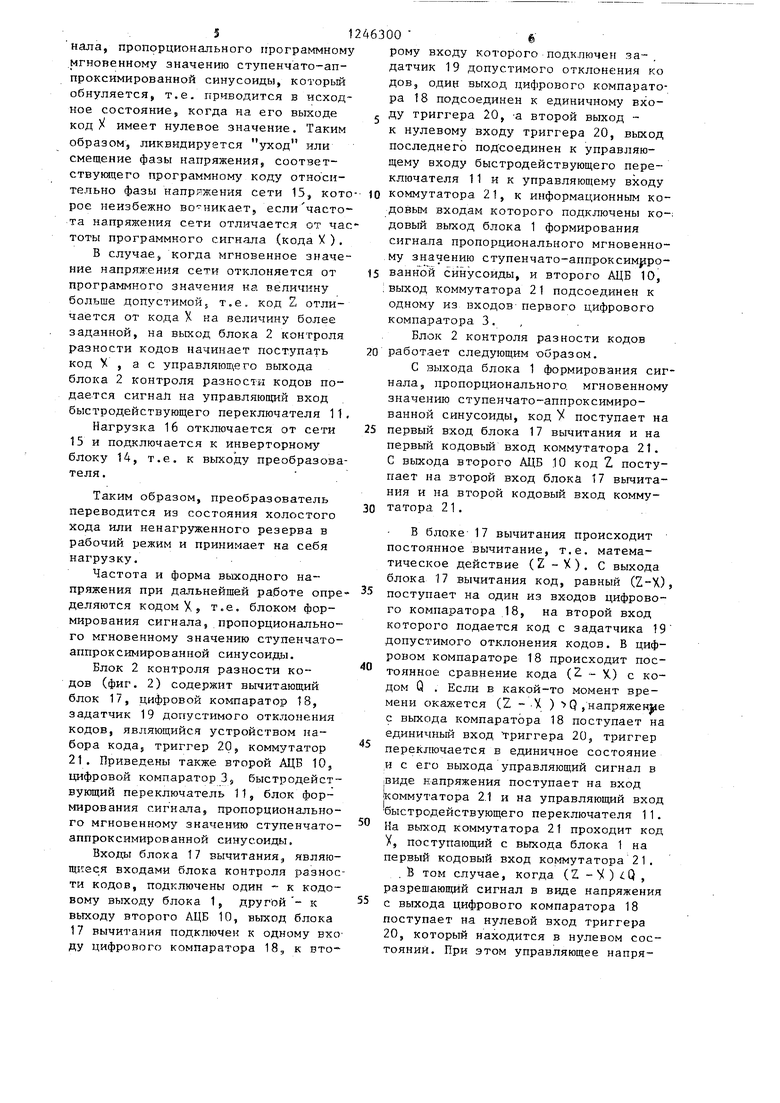

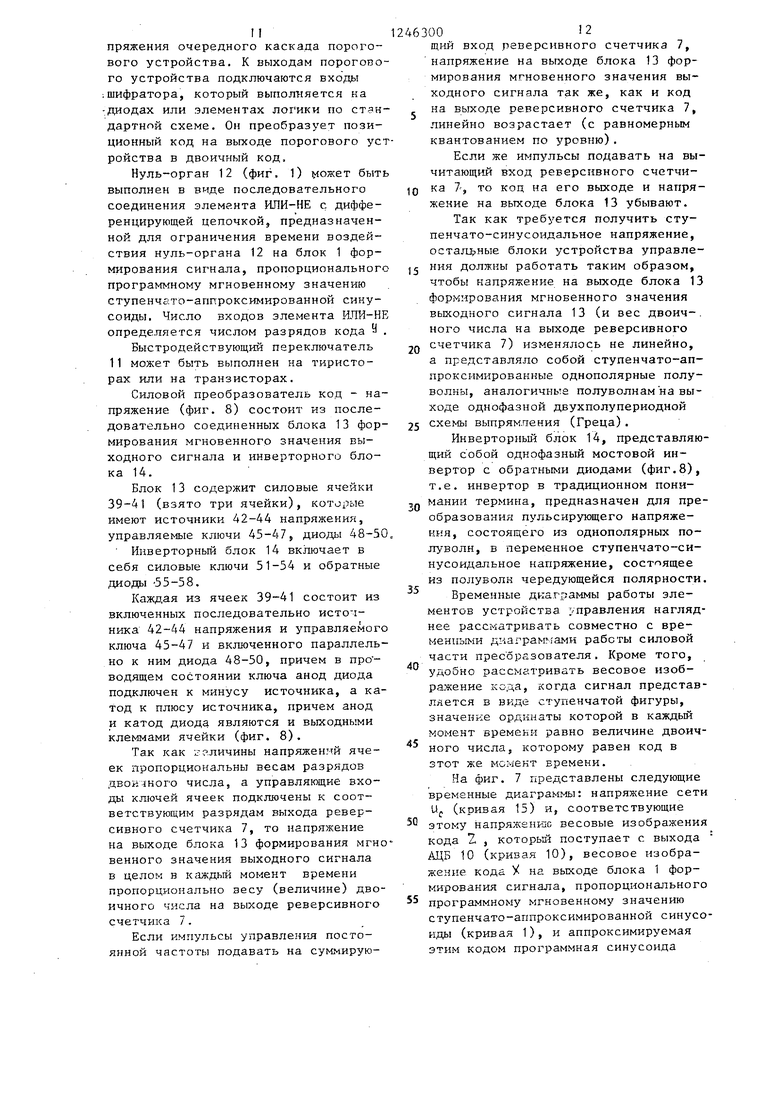

Задатчик 19 допустимого отклонени кодов может быть выполнен или в виде ключей (включаемых поразрядно), или на логических элементах. В качестве примера приведена функциональная схема задатчика допустимого отклонения кодов (фиг. 3), Б котором Q 3. В общем случае

Q

4U

U JT

J

где

V U

:V

максимальное значение кода X (для случая четырехразрядного кода

mcv 15); действующее значение напряжения в сети (номинальное) ;

предел допустимого отклонения мгновенного значения напряжения на нагрузке от расчетного. Функциональная схема коммутатора 21 (фиг, 4) на четыре разряда,выполнена на логических элементах. В состав коммутатора входят восемь элементов И 22-29, элемент НЕ 30 и четыре элемента i-UlH 31-34. Коммутатор 21 имеет управляющий вход, два кодовых входа (вход А и вход Б) и выход.

Схема работает следующим образом Hi кодовый вход А (элементы 22 25) поступает код X , на кодовьм вход Б (элементы 26-29) поступает код Z. Если на управляющий вход не поступает управляющий сигнал, то на выход коммутатора 21 поступает код Z-,, так как элементы 22-25 закрыты, а состояние элементов 26-29 определяется кодом Z , так как на их раз- решающие вхсщы поступает напряжение с выхода элемента 30. Если же на управляющий вход коммутатора 21 подано напряжение (управляющий сигнал), то на выходе элемента 30 напряжения

10

20

2463008

нет, элементы 26-29 закрыты, и на выход поступает код V .

В блок 1 формирования сигнала, пропорционального программному мгно венному значению ступенчато-аппроксимированной синусоиды, с четырех- разрядньгм выходом входят задающий генератор 35, счетчик 36, программируемое запоминающее устройство 37, триггер 38 (фиг, 5). Выход задающего генератора 35 соединен со счетным входом счетчика 36, кодовый выход которого поразрядно подключен к адресным входам программируемого J2 запоминающего устройства 37, а вы- чод переполнения счетчика 36 соединен со счетным входом триггера 38, обнуляющий вход счетчика 36 и единичный вход триггера 38 подключены к общей шине, являющейся обнуляющим входом блока 1 формирования сигнала, пропорционального программному мгновенноьгу значению ступенчато- аппроксимированной синусоиды (фиг. О. 25 Выходные шины программируемого запоминающего устройства 37 образуют кодовый выход (выход 1), на котором формируется код К , а выход триггера 38 является триггерным выходом блока 1, на котором формируются сигналы управления инверторным блоком 14 (фиг. 1).

Схема работает следующим образом. При подаче напряжения на обнуляющий вход схема приводится в исходное состояние: триггер 38 устанавливается в единичное состояние, в счетчик 36 записывается О.

В дальнейшем (после снятия обнуля ющего сигнала) импульсы с выхода задающего генератора 35 поступают на вход счетчика 36. Ка выходе счетчика формируется двоичный восьмиразрядный равномерно возрастающий код, который поступает на вход пpoгpaммиpveмoгo запоминающего устройств 37. В соответствии с изменением кода изменяютсэ номера адресов в программируемом за- поминающем устройстве 37, подключенных к его выходу. При этом в адреса программируемого запоминающего устройства 37 должны быть записаны такие значения кода X , которые бы соответствовали аппроксимации синусои- . ды весовыми значениями кода X . 55 Так, для рассматриваемого варианта (четырехразрядный код V , частота выходного напряжения преобразователя 50 Гц) частота на выходе задаюи(его

30

35

40

45

50

91246300

генератора 35 - 25600 Гц, счетчик 36 имеет восьмиразрядньй выход и собран из двух микросхем К155ИЕ5, в качестве nporpaNtMHpyeMoro запоминающего устройства 37 выбрана микросхема КР556РТ4, 5 таблица соответствий програ чмируемо- го запоминающего устройства 37 при10Продолжение таОлшды

пряжения очередного каскада порогового устройства, К выходам порогового устройства подключаются вхо ды ;шифратора, который выполняется ка диодах или элементах логики по стандартной схеме. Он преобразует позиционный код на выходе порогового усройства в двоич 1ый код.

Нуль-орган 12 (фиг, 1) может быт выполнен в виде последовательного соединения элемента ИЛИ-НЕ с дифференцирующей цепочкой, предназначенной для ограничения времени воздействия нуль-органа 12 на блок 1 формирования сигнала, пропорциональног программному мгновенному значению ступенчато-аппроксимированной синусоиды. Число входов элемента ИПИ-Н определяется числом разрядов кода 9

Быстродействующий переключатель 11 может быть выполнен на тиристорах или на транзисторах.

Силовой преобразователь код - напряжение (фиг. 8) состоит из последовательно соединенных блока 13 формирования мгновенного значения выходного сигнала и инверторного блока 14.

Блок 13 содержит силовые ячейки 39-41 (взято три ячейки), которые имеют источники 42-44 напряжения, управляемые ключи 45-47, диоды 48-50

Инверторный блок 14 включает в себя силовые ключи 51-54 и обратные диоды -55-58.

Каждая из ячеек 39-41 состоит из включенных последовательно исто 1- ника 42-44 напряжения и управляемого ключа 45-47 и включенного параллельно к ним диода 48-50, причем в про - водящем состоянии ключа анод диода подключен к минусу источника, а катод к плюсу источника, причем анод и катод диода являются и выходными клеммами ячейки (фиг. 8).

Так как г .личины напряжений ячеек пропорциональны весам разрядов двок-шого числа, а управляющие входы ключей ячеек подключены к соответствующим разрядам выхода реверсивного счетчика 7, то напряжение на выходе блока 13 формирования мгно венного значения выходного сигнала в целом в каждый момент времени пропорционально весу (величине) двоичного числа на выходе реверсивного счетчика 7.

Если импульсы управления постоянной частоты подавать на суммирую46300 2

щий вход реверсивного счетчика 7, напряжение на выходе блока 13 формирования мгновенного значения выходного сигнала так же, как и код на выходе реверсивного счетчика 7, линейно возрастает (с равномерным квантованием по уровню),

Если же импульсы подавать на вычитающий вход реверсивного счетчи- (Q ка 7, то коц на его выходе и напряжение на выходе блока 13 убывают.

Так как требуется получить ступенчато-синусоидальное напряжение, остальные блоки устройства управле- 55 ния должны работать таким образом, чтобы напряжение на выходе блока 13 формирования мгновенного значения выходного сигнала 13 (и вес двоич-. ного числа на выходе реверсивного 2Q счетчика 7) изменялось не линейно, а представляло собой ступенчато-аппроксимированные однополярные полуволны, аналогичные полуволнам на выходе однофазной двухполупериодной 25 схемы выпрямления (Греца).

Инверторный блок 14, представляющий собой однофазный мостовой инвертор с обратными диодами (фиг.8), т.е. инвертор в традиционном пони- , мании термина, цредназначен для преобразования пульсирующего напряжения, состоящего из однополярных полуволн, в переменное ступенчато-синусоидальное напряжение, состоящее из полуволн чередующейся полярности.

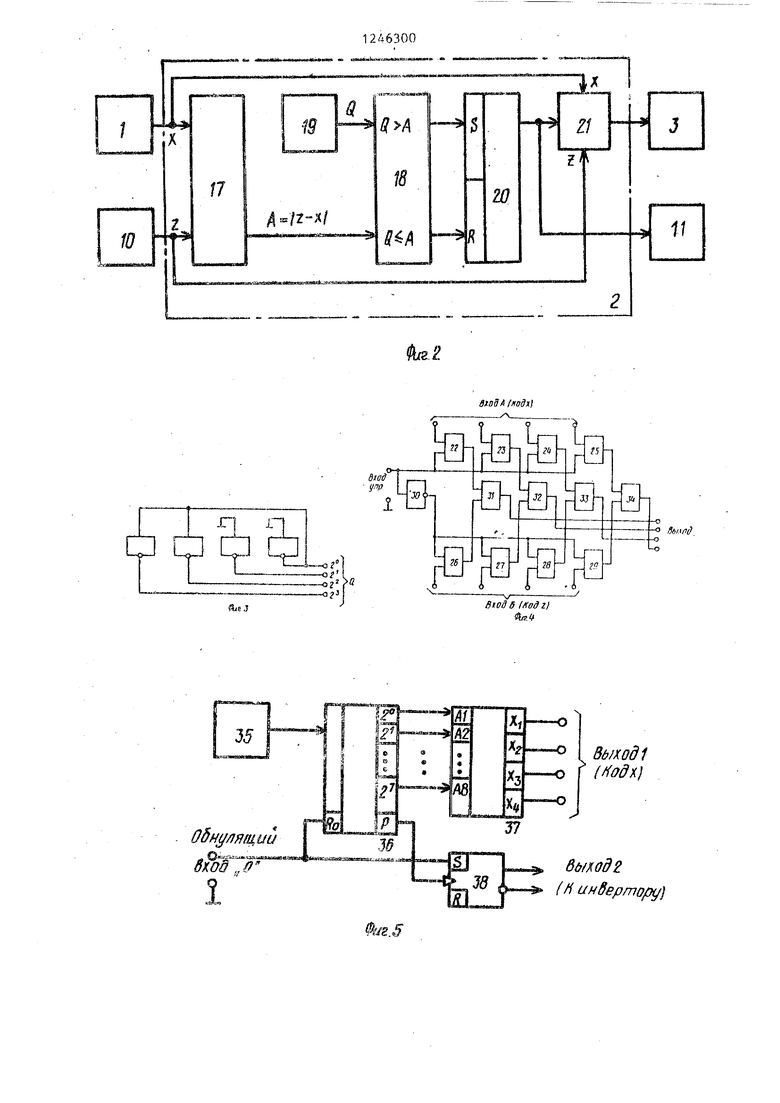

Временные диаграммы работы элементов устройства управления нагляднее рассматривать совместно с временными диаграммами работы силовой части преобразователя. Кроме того, удобно рассматривать весовое изображение кода, когда сигнал представляется в виде ступенчатой фигуры, значение ординаты которой в каждьш момент времени равно величине двоичного числа, которому равен код в этот же момент времени.

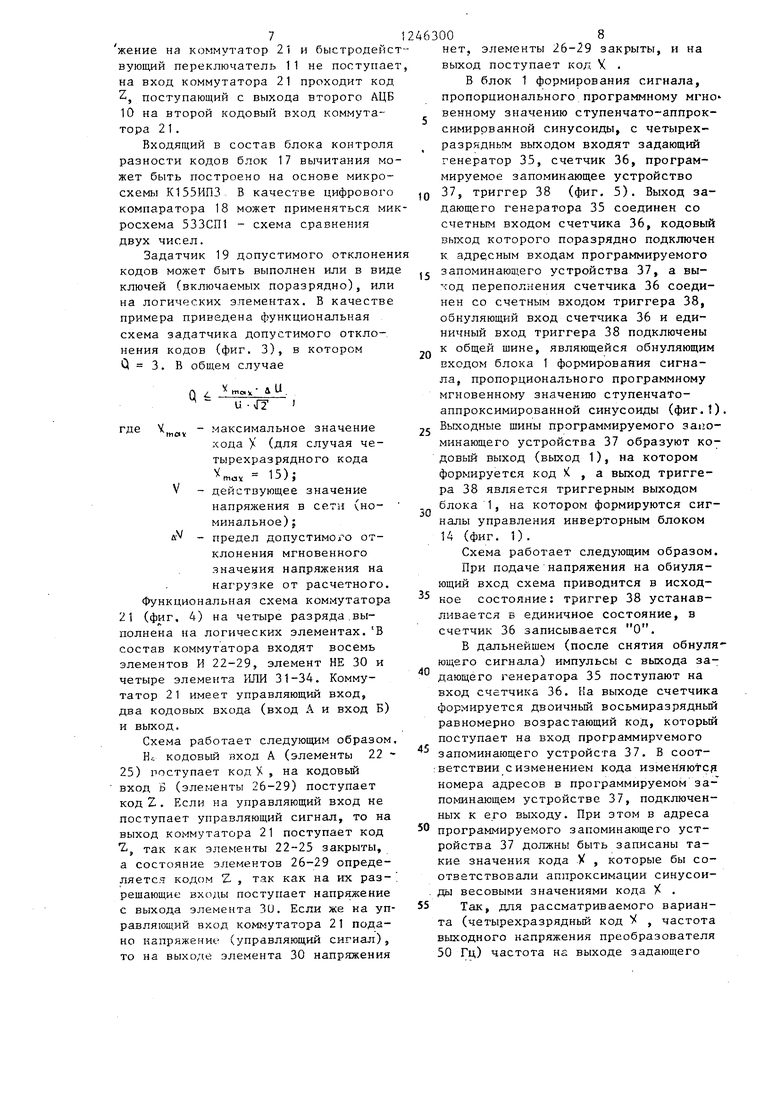

На фиг. 7 представлены следующие временные диаграммы: напряжение сети Uj (кривая 15) и, соответствующие 5 этому Напрях енкс весовые изображения кода 2. J которьй поступает с выхода АЦБ 10 (кривая 10), весовое изображение кода X на выходе блока 1 формирования сигнала, пропорционального 55 программному мгновенному значению ступенчато-аппроксимированной синусоиды (кривая 1), и аппроксимируемая этим кодом программная синусоида

35

40

45

u

13

пр 5 весовое изображение кода А (Z-X) .на выходе блока 17 вычитания блока 2 контроля разности кодов (ступенчатая кривая 17) и весовое значение числа Q на выходе задатчика 19 допустимого отклонения кодов (прямая 19) сигнал (напряжение) на первом выходе цифрового компаратора 18 блока 2 контроля разности кодов и на. единичном выходе триггера 20,; напряжение на выходе быстродействующего переключателя 11 j, т.е. напряжение на нагрузке (кривая 16). Пунктиром показана программная синусоида

Для наглядности (фиг, 7) приняты следующие допущения и упрощения: Коды У и Z имеют лишь по три разряда, напряжение сети U несколько выше напряжения программной синусоиды арпроксимируемой кодом X , т.е. амплитуда кривой 15 (фиг. 7а) несколько больше амплитуды кривой U,-ip (фиг. 7б) . В момент времени t происходит пропадание.напряжения сети, т.е. быстрое и значительное изменение мгновенного значения напряжения U (кривая 15, фиг. 7а) и соответствующего ему значению кода Z (ступенч - гая кривая, фиг, 7а) .

На интервале времени О i - на выход быстродействующего переключателя 11 поступает напрялсение сети U(, (кривая 16, фиг, 7д) ,

В момент времени i в сети наблюдается пропадание напряжения - резкий спад кривой 15 (фиг. 7а), что приводит к значительному изменению значения кода 2, (ступенчатая кривая 10, фиг, 7а), соответствующего мгновенному значению напряжения сети Uj, , При этом код A(Z --X ) на выходе .блока.17 вычитания блока 2 контроля разности кодов становится больше числа Q на выходе задатчика. 19 допустимого отклонения кодов (стпенчатая, кривая 17 и прямая 19; фиг. 7в)5 что приводит к появлению сигнала на первом вьпходе цифрового компаратора 18, 1риггер 20 перебрасывается в единичное состояние, на его единичном выходе появляется сигнал, (напряжение), что приводит к переключению коммутатора 21 и быстродействующего переключателя 11 (фиг. 2). При этом на первый вход цифрового компаратора 3 начинает поступать код У, с выхода блока 2 контроля разности кодов (до момента t. поступает код Z )з на выход

1

300

быстродействующего переключателя 11 начинает поступать ступенчато-синусоидальное напряжение с выхода ин- верторного блока 14 преобразователя

(до момента на выход поступает напряжение сети 15, фиг. 1). Таким образом, форма напряжения на выходе быстродействующего переключателя 11, т.е. на нагрузке 16, на интервале Oti t имеет форму напряжения сети т.е. близка к синусоидальной,.а

U

s

0

5

0

на интервале t t имеет форму ступенчато-синусоидальную (фиг, 7д,

кривая 16).

Использование блока контроля разности кодов, АЦБ быстродействующего переключателя, нуль-органа и связей расширило функциональные возможности устройства и область его применения и позволило применить преобразовате- .пи с высокими динамическими свойствами, высокой точностью стабилизации выходного напряжения и высоким качеством по гармоническому составу напряжения в установках Гарантированного пич ания и осуществить переход нагрузки с сеч и на преобразователь без разрыва кривой выходного напряжения,что необходимо для потребителей не допускающих перерьшов в электропитании.

Формула изобретения

Устройство для управления преобразователем постоянного напряжения в пер.зменное типа силового преобразователя код - напряжение, содержащего последовательно соединенные блок. формирования мгновенного значения выходного сигнала и инвертор- ный блок с управляющим входом, причем блок формирования мгновенного значения вькодного сигнала выполнен в виде последовательно соединенных по вьпсоду ершовых ячеек, каждая из которых состоит из последовательно включенных источника напряжения, угфавляемого ключа и подключенного параллельно к ним диода, электродь которого образуют выход ячейки, при этом величина напряжений источников пропорциональна весам двоичных разрядов управляющего кода, а инвертор- ный блок выполнен по схеме однофазного мостового .инвертора с обратными диодами, один из входов и выход KOTOiJoro являются силовыми, а дру

гой зход - управляющим, содержащее блок формирования сигнала в виде двоичного кода, значение которого пропорционально програмт ному мгновенному значению ступенчато-аппрокси- мировчнной синусоиды, с выходом программного мгновенного значения ступенчато-аппроксимированной синусоиды и выходом полярности полуволны выходного сигкчла, измерительный вы- прямитель, входом подключенный к выходу инверторного блока, первьй аналого-цифровой блок, входом подключенный к выходу измерительного выпрямителя, цифровой компаратор с выходом приоритета числа на первом входе н выходом приоритета числа на втором входе, причем второй вход компаратора подключен к вьтходу первого аналого-цифрового блока, два логи- ческих элемента совпадения, первые входы которых соединены с выходом цифрового компаратора, вторые входы подключены к выходу генератор;а импульсов, а также реверсивный счетчик суммирующим входом соединенный с выходом первого логического элемента совпадения, вычитающим входом - с выходом второго логического элемента

совпадения, а выход его поразрядно подключен к управляющим входам блока формирования мгновенного значения выходного сигнала, отличаю.- щ е е с я тем, что, с целью расширения функциональных возможностей, оно снабжено быстродействующим переключателем, нуль-органом, вторым аналого-цифровым блоком, блоком контроля разности кодов, включающим в себя задатчик допустимого отклонения кодов, блок вычитания, цифровой компаратор с выходом приоритета выходного сигнала задатчика допустимого отклонения кодов и выходом приоритета выходного сигнала блока вычитания, KO f ,рый также является выходом равенства этих сигналов, триггер, коммутатор для переключения кодовых пшн

j 10 f5 20 25

0

5

0

5

причем один силовой вход быстродействующего переключателя подключен к питающей сети,а другой - к выходу инверторного блока, выход перек;почателя подключается к нагрузке, выход мгновенного значения ступенчато-аппроксимированной синусоиды блока формирования сигнала в виде двоичного кода, значение которого пропорционально программному мгновенному значению ступенчато-аппроксимиройанной синусоиды, подключен к первому входу блока вычитания, вход второго аналого-цифрового блока подключен к питающей сети, а выход подключен к второму входу блока вычитания, выход коммутатора является первым, кодовым, выходом блока контроля разности кодов и подключен к первому входу цифрового компаратора, выход, триггера, яв- ляющийс я в то рым,управляющим,выходом блока контроля разности кодов, подключен к третьему, управляющему, входу быстродействуняцего переключателя, нуль-орган входом соединен с выходом первого аналого-цифрового блока, а выходом подключен к обнуляющему вйоду блока формирования сигнала в виде двоичного кода,значение которого пропорционально про- . граммному мгновенному значению ступенчато-аппроксимированной синусоиды, внутри блока контроля разности кодов вькод задатчика допустимого отклонения кодов подключен к первому входу цифрового компаратора, к второму входу которого подключен выход блока вычитания, первый выход цифрового компаратора подключен к единичному входу триггера, второй выход - к нулевому входу триггера, имеющего один выход, к которому подключен первый, управляющий, вход коммутатора, второй, кодовый вход которого соединен с первым входом блока вычитания, а третий вход, также кодовый, с в-горым входом блока вычитания.

SusdA /кода

о:

jq ГП

I-i-0 г°,

02 Ли

-ог

Й/е.7

TI:

TI - даф

to 1л HVr

tb

L

FJ г

1

i

t

C

fSbiffld

Si Од S I Под г) tf

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления преобразователем источника гарантированного питания | 1987 |

|

SU1603506A1 |

| Устройство для управления преобразователем постоянного напряжения в многоступенчатое квазисинусоидальное | 1983 |

|

SU1319206A1 |

| Преобразователь постоянногоНАпРяжЕНия B пЕРЕМЕННОЕ | 1978 |

|

SU813629A1 |

| Преобразователь постоянного напряжения в многоступенчатое квазисинусоидальное | 1980 |

|

SU905962A1 |

| Устройство двухступенчатого аналого-цифрового преобразования | 1985 |

|

SU1266003A1 |

| Способ управления тиристорным преобразователем | 1987 |

|

SU1539934A1 |

| Агрегат гарантированного питания | 1990 |

|

SU1742942A1 |

| Устройство для контроля показателейКАчЕСТВА элЕКТРичЕСКОй эНЕРгии ВТРЕХфАзНыХ СЕТяХ | 1979 |

|

SU838593A1 |

| Преобразователь угловых перемещений в код | 1985 |

|

SU1311024A1 |

| Фазометр | 1990 |

|

SU1797076A1 |

Изобретение относится к электротехнике, а точнее к преобразователям постоянного напряжения в пе ременное с квазисйнусоидальной или ступенчато-синусоидаль-ной формой выходного напряжения, и может быть использовано в -установках гарантированного питания потребителей переменного тока. Целью изобретения является расширение функциональных возможностей и области применения устройства. Цель изобретения достигается тем, что в режиме отслеживания напряжение сети 15 черег быстродействующий переключатель 11 поступает на нагрузку 16. Также напряго 4ib О) 00

Обн(//}яа1,ии

| B; ;ii t-t3i5

SxoS ,,ff

ol

I

. Г (/fffdK) J

вд/KodZ

(fi анбертору}

Bbmodf SifxodJ

f-0

Sb/iodf -l 8б/10д

11

П

CK) СЮ

-0 +

Составитель А.Меркулова Редактор Н.Бобкова Техред В.Кадар Корректор Е.Сирохман

Заказ А017/52 Тираж 631 . Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,„ д. 4/5

Производственно-полиграфическое предприятие,, г. Ужгород, ул. Проектная, 4

| Преобразователь постоянногоНАпРяжЕНия B пЕРЕМЕННОЕ | 1978 |

|

SU813629A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Преобразователь постоянного напряжения в квазисинусоидальное переменное | 1977 |

|

SU731532A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-07-23—Публикация

1985-01-07—Подача