(54) УСТРОЙСТВО ФОРМИРОВАНИЯ МНОГОСТУПЕНЧАТОГО КВАЗИСИИУСОИДАЛЬНОГО ТРЕХФАЗНОГО НАПРЯЖЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство формирования многоступен-чАТОгО КВАзиСиНуСОидАльНОгО ТРЕХфАз-НОгО НАпРяжЕНия | 1979 |

|

SU817902A1 |

| Фотоэлектрический анализатор количества и размеров частиц | 1987 |

|

SU1518727A1 |

| Цифровой измеритель температуры | 1986 |

|

SU1364910A1 |

| Цифровой измеритель составляющих комплексных сопротивлений | 1987 |

|

SU1456907A1 |

| Интегрирующий преобразователь напряжения в код | 1986 |

|

SU1410275A1 |

| ЭЛЕКТРОННЫЙ СЧЕТЧИК АКТИВНОЙ ЭНЕРГИИ | 1993 |

|

RU2075755C1 |

| Компаратор | 1988 |

|

SU1631512A1 |

| СПОСОБ ДВУХТАКТНОГО АНАЛОГО-ЦИФРОВОГО ПРЕОБРАЗОВАНИЯ ИНТЕГРИРУЮЩЕГО ТИПА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2014 |

|

RU2564909C1 |

| Цифровой измеритель параметров комплексных сопротивлений | 1985 |

|

SU1302211A1 |

| Задающий генератор многоступенчатого трехфазного напряжения | 1980 |

|

SU1001436A1 |

1

Изобретение относится к полупроводниковой преобразовательной технике и может быть использовано для фор )лирования квазисинусоидального эталонного напряжения, используемого в управлении преобразователем для последующего сравнения его с мгновенными значениями входного напряжения преобразователя и получения информации о целесообразном переключении его силовых ключей.

Известно устройство формирования квазисинусоидального напряжения, выполненное в виде последовательно соединенных генератора тактовых импульсов, триггерного счетчика и дешифратора, разные выходы которого одновременно связаны с одной диагональю мостовым переключателем и с ключами дополнительного преобразователя, причем выходы последних нагружены на другую диагональ переключателя l .

Однако в данном устройстве согласование выходов с последующей частью системы управления усложняется из-за необходимости применения развзывающих узлов.

Известно также устройство, в кот ром квазисинусоидальное трехфазное

управляющее напряжение формируется блоком, содержащим регулируемый источник постоянного тока, включенный между общей точкой ключей коммутатора и сумматором, параллельно которому включены две цепочки из последовательно соединенных первичной полуобмотки трансформатора-и ключевого элемента,управляемого от высокочастотного генератора, а каждая вторичная полуобмотка указанного трансформатора подключена к нагрузке также через ключевой элемент, управляемый от триггера, причем вход триггера связан с выходом указанного коммутатора 2 .

Недостатки этого устройства заключаются в том, что необходимо иметь специальные нестандартные узлы преобразователя код-аналог, а также в нетехнологичности моточных элемен-тов.

Наиболее близким к предлагаемому является устройство, содержащее

5 преобразователь напряжение-частота (который представляет собой регулируемый генератор тактовой частоты), счетчик импульсов и дешифратор, которые, будучи последовательно включенными, представляют собой цифрофункциональные генераторы, и формирователи по числу фаз, которые ресшизуют функции цифроаналоговыхI преобразователей. Кроме того, устройство содержит дополнительный счетчик, дополнительный дешифратор, .триггеры по количеству фаз формируемого напряжения и дополнительные ключи, количество которых определяется фазностью формируемого напряжения, причем выход каждого формирователя подключен к суммирующей точке каждой фазы через соответствукядие дополнительные пары ключей, цепи управления которых связаны с дополнительным дешифратором, управляющие также через соответствующие триггеры дополнительными выходными ключами, а вход дополнительного дешифратора связан со счетчиком через дополнительный счетчик и инвертор, который выполняет функции инвертирующего усилителя с единичным усилением.

При работе устройства вначале формируют однополярные полупериоды аппроксимированной синусоиды для каждой выходной фазы и к выходу в один полупериод напряжение подключается прямо, а в другой - через инвертор. На выходе инвертора сигнал будет не только противоположной полярности относительно входного, но и с измененной фазой и амплитудой. Такой метод формирования выходного напряжения приводит к асимметрии выходного напряжения 3 .

Недостатком известного устройства является относительная его сложность и недостаточно высокое качество выходного напряжения.

Цель изобретения - упрощение преобразователя и улучшение качества выходного напряжения.

Поставленная цель достигается тем, что в устройстве формирования многоступенчатого квазисинусоидального трехфазного напряжения, содержащем инвертирующий усилитель с единичным усилением, а также последовательно соединенные регулируемый генератор тактовой частоты с числом равным числу выходных фаз, цифрофункциональные генераторы двоичного кода, выходы которых соединены со входами цифроаналоговых преобразо- вателей, причем входы последних подключены к задатчику уровней постоянного напряжения, упомянутый инвертирующий усилитель с единичным усилением включен между выходом задатчика уровня постоянного напряжения и входами цифроаналоговых преобразователей. Кроме того, устройство, цифро-функциональные генераторы которого включают в себя Т-триггёр со счетным входом и входом тактирования, .каждый цифро-функциональный генератор дополнительно содержит линию задержки второго такта, линию

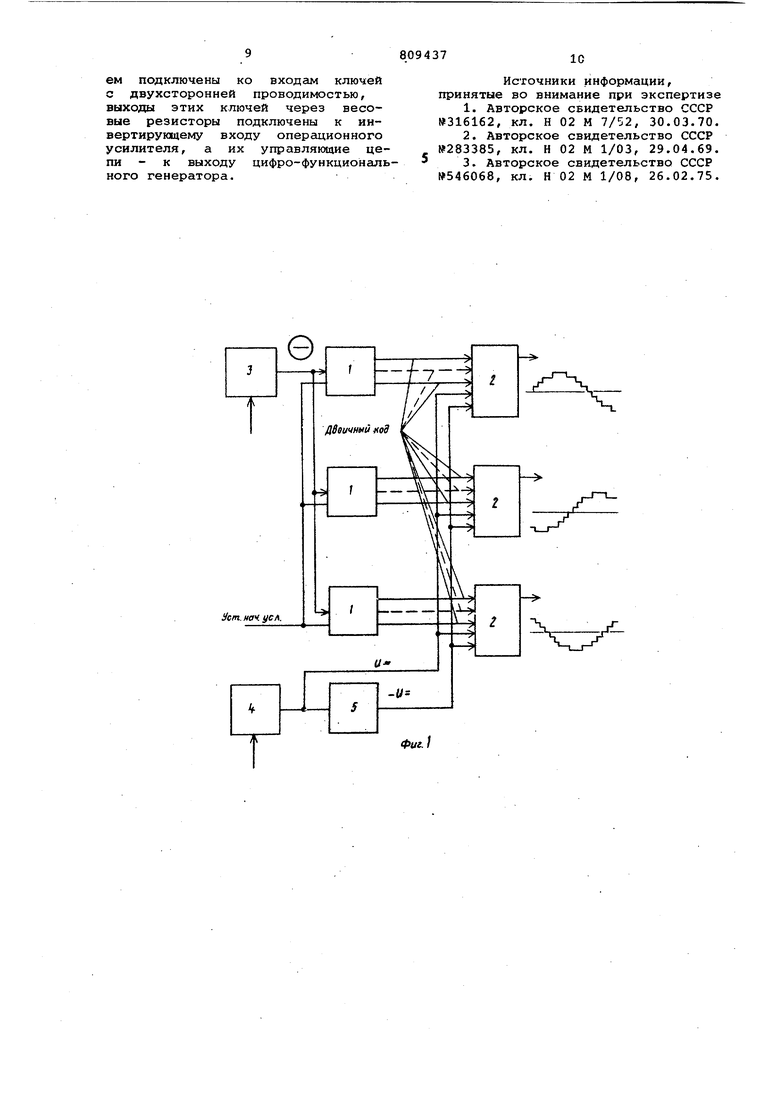

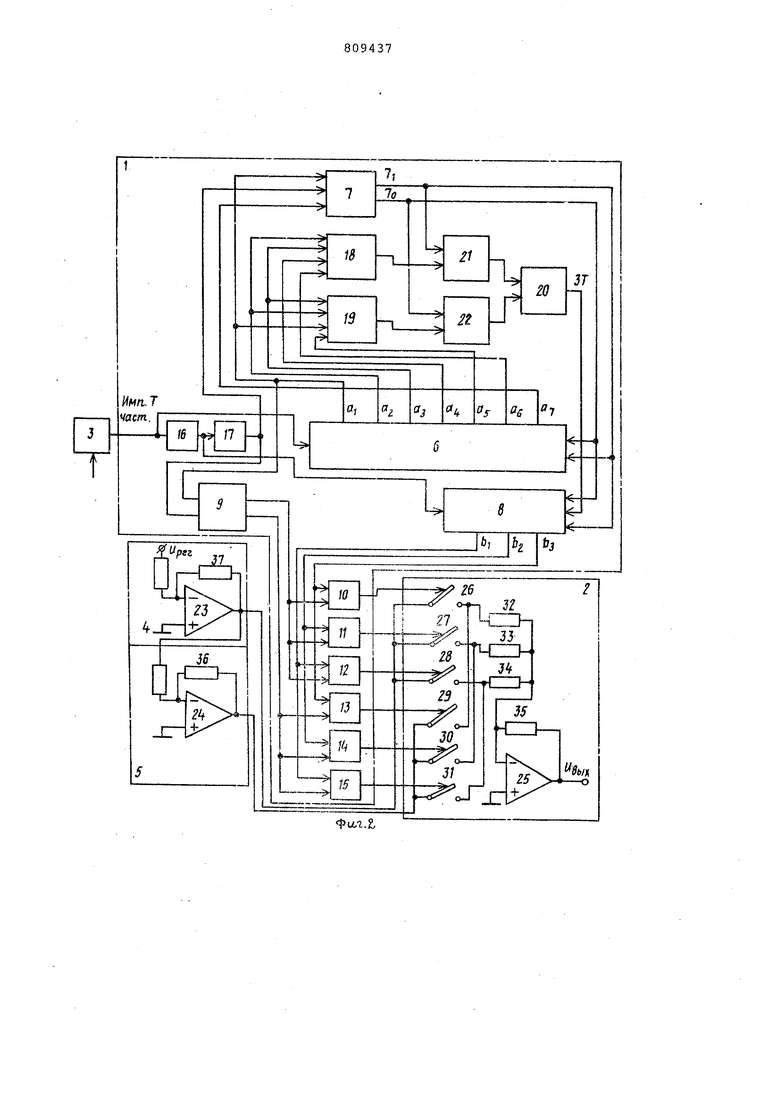

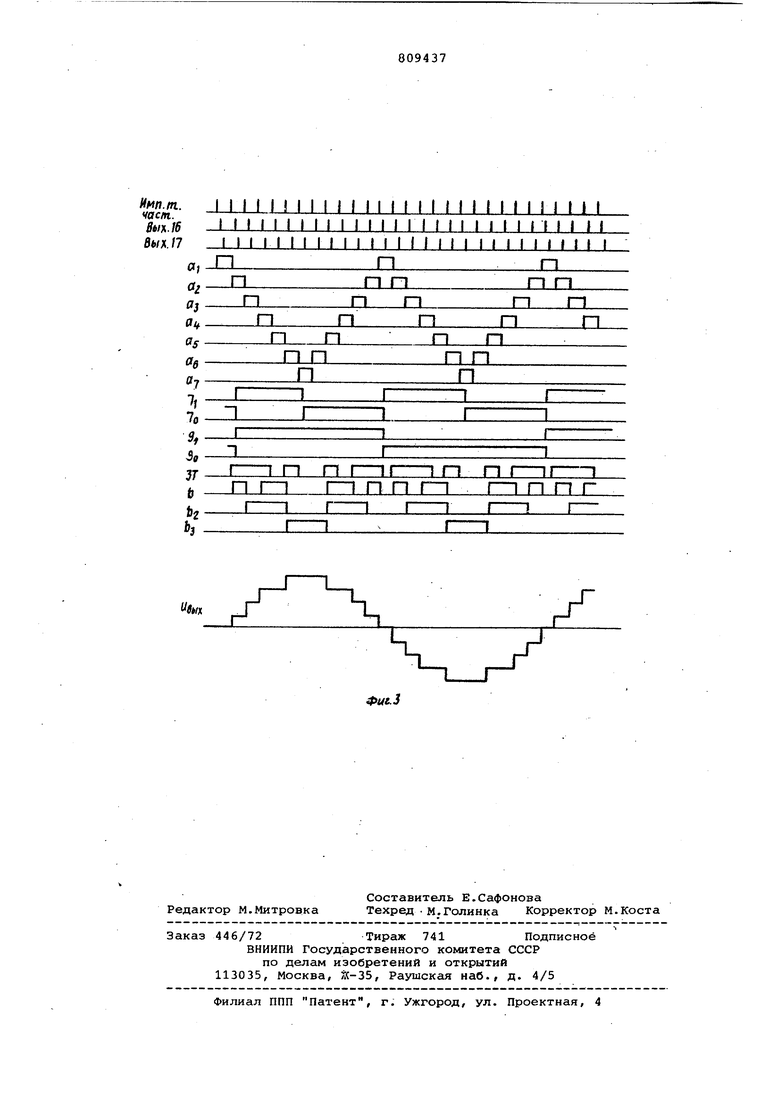

задержки третьего такта, реверсивный двоичный счетчик с управляющими счетным и тактирующим входами, датчик времени со входом тактирования первого такта и со входом тактирования третьего такта, двухвходовые логические элементы И, причем вход линии задержки второго такта подключены к выходу регулируемого генератора тактовой частоты и ко входу тактирования .первого такта датчика времени, выход линии задержки второго такта подключен ко входу тактирования реверсивного двоичного счетчика и ко входу линии задержки третьего такта, а выход линии задержки третьего такта подключен ко входу тактирования Т-триггера и ко входу тактирования третьего такта датчика времени, выходы датчика времени подключены к счетному входу Т-триГгера, к счетному входу реверсивного двоичного счетчика и к управлягацим входам реверсивного двоичного счетчика, а каждый выход реверсивного двоичного счетчика совместно с выходами Т-триггера подключен ко входам двух двухвходовых логических элементов И. Датчик времени содержит реверсивный сдвигающий регистр с тактируквдим и управля1Свцими входами. RS-триггер с информационными и тактирующим входами , вспомогательные двухвходовые логические элементь И, логические элементы ИЛИ, причем выходы реверсивного сдвигающего регистра подключены ко входам логических элементов ИЛИ и к информационным входам RS-триггера, входы логических элементов И подключены к выходам RS-триггера и к выходам логических элементов ИЛИ, выходы вспомогательных логических элементов И подключены ко входам ло гического элемента ИЛИ, а выходы RS-триггера подключены к управляющим цепям реверсивного сдвигающего регистра. Кроме того, в устройстве, .цифроаналоговые преобразователи: которого включают в себя весовые резисторы и ключи с двухсторонней проводимостью, цифроаналоговый преобразователь содержит резистор обратной связи и операционный усилитель с инвертирующим и неинвертирующим входами, причем резистор обраной связи подключен к выходу операционного усилителя и к инвертирующему входу операционного усилителя, а неинвертирукяций вход операционного усилителя подсоединен к общей точке устройства, выходы задатчика уровня постоянного напряжения и инвертирующего усилителя с единичным Усилением подключены ко входгии ключей с двухсторонней проводимостью, выходы этих ключей через весовые резисторы подключены к инвертирующему входу операционного усилителя, а их управлякяцие цепи - к выходу цифро-функционального генератора. На фиг. 1 представлена принципи.альная электрическая схема предлагае мого устройства; на фиг. 2 - то же, с более детальной структурной прора боткой узлов; на фиг. 3 - временные диаграммы, поясняющие принцип работы устройства. Устройство содержит блоки 1 цифро-функциональных генераторов, блок 2 щифроаналоговых: преобразователей блок 3 регулируемого генератора так товой частоты, блок 4 задатчика уро ня ПОСТОЯННОГО напряжения, блок 5 инвертирующего усилителя с единичным усилением, блок б реверсивного сдвигающего регистра с управляющими входами (сдвиг вправо - сдвиг влево и входом тактирования, блок 7 RSтриггера с информационными входами (R - установка нуля, S - установка единицы) и входом тактирования, блок 8 реверсивного двоичного счетчи ка с управляющими входами (суммирование - вычитание), с счетным входом и входом тактирования, блок 9 Т-триг гера с счетным входом и входом тактирования, двухвходовые логические элементы 10-15 И, линию 16 задержки второго такта, линию 17 задержки третьего такта, логические элементы 18-20 ИЛИ, вспомогательные логические элементы 21 и 22 И, блоки 23-25 операционных усилителей, ключи 2631 с двухсторонней проводностью, весовые резисторы 32-34, резистор 35 обратной связи, а также резисторы 36 и 37. На временных диаграммах работы устройства по фиг.З обозначены выходные импульсы Ими.т.част, блока 3, выходные импульсы Вых.16 и Вых.17 блоков 16 и 17 соответственно, выход ные разряды реверсивного сдвигающего регистра, сигнал U единичного выхода блока 7, сигнал U J-Q нулевого выхода блока 7, сигнал Ug.j единичного выхода блока 9, сигнал (ig нулевого выхода блока 9, сигнал ЗТ счетного входа блока 8, первый выходной разряд Ь блока 8 (млад ший), второй выходной разряд bg блока 8, третий выходной разряд Ь, блока 8 (старший) и выходное напряжение блока 25. Каждая фаза устройства состоит из последовательно включенных выходов блоков 1 со входами блоков 2. Все входы блоков 1 подключены к общему блоку 3, а выходы последовательно включенных между собой блоков 4 и 5 подключены ко всем входам блоков 2. Выполнение всех фаз устройства с применением блоков 1 и блоков 2 одинаково. Работа всех трех фаз устройства отличается лишь установкой начальных условий, т.е. двоичных слов в блоках 1 с временным сдвигом на 1/3 периода периодически повторяющего двоичного кода аппроксими- рованной синусоиды. Общим для всех трех фаз является блок 3, регулированием частоты которого осуществляют изменение частоты нагряжания выходных фаз. Изменением выходного напряжения блока 4 осуществляют регулиро;вание амплитуды напряжения выходных фаз устройства. Для описания работы одной фазы устройства в качестве примера расг смотрим случай, когда квант функции -И аргумент между собой одинаковы и численное значение их равно 0,26. Амплитудное значение функции равно единице и аргумент функции выражен в радианах. Величина кванта в каждом конкретном случае выбирается в зависимости от необходимой точности формирования аппроксимированной синусоиды. Устройство работает следующим образом. Перед работой устройства устанавливается начальное условие в блоках 1. В каждом блоке 1 меняется последовательность двоичных слов, определяю1ДИХ число квантов функции аппроксимированной синусоиды. Выходы блоков 1 подключены к входам блоков 2, при помощи которых двоичные слова блоков 1 преобразуют в аналоговые величины формируемого напряжения. Подробнее рассмотрим работу блока 1. Блоки 7-9 блока 1 имеют входы тактирования, т.е. изменение внутреннего состояния этих узлов происходит только в том случае, если имеется сигнал на счетном или информационном входе при подаче разрешгияцего тактируемого импульса. При подаче тактируемого импульса с выхода блока 3 на вход блока 1 можно выделить три такта работы, в первом из них при помощи сигнала Имп.т.част, происходит сдвиг единицы в блоке6, во втором при помощи импульса Вых.16 происходит смена двоичного кода в блоке 8, если на счетный вход подан сигнал и в третьем при помощи импульса Вых.17 при наличии импульса на счетном входе блока 9 происходит изменение внутреннего состояния этого блока, а также изменение внутреннего состояния блока 7 при наличии входного сигнала на одном информационном входе. В начальный момент времени, когда единица наисодится в первом разряде блока 6, на выходе блока 7 появляетя единица, которая подключает выход лока 18 через блоки 19 и 20 к счетному входу блока 8, кроме того, вы-одной Сигнал блока,,7 подключен управлякщим входам блоков 6 и 8. ЛОК 6 установлен в режиме сдвиг вправо, а блок 8 - в режиме сумирования. Каждый разряд блока 6 пределяет кратное численное значе- ие аргумента, а также временной

интервал. Разряды блока 6, в которых происходит изменение значения функции, подключены к входу блока 18. Когда появляется сигнал U7o з. йыходе блока7, югда к счетному входу блока В подключен выход блока 21, блок б находится в режиме сдвиг влево, а блок 8 в режиме вычитания.

Таким образом, на выходе блока 8 периодически повторяются двоичные слова, определяющие однополярные значения функции аппроксимированной синусоиды. При помощи блока 9, счетный вход которого подключен к первому разряду блока.6, выходы блока 8 поочередно подключаются ко входам блока 2 при помощи логических элементов 10-12 в один полупериод, а в другой полупериод - при помощи логических элементов 13-15.

Задержка тактируемых импульсов в блоках 16 и 17 происходит на время 5 . Время больше переходных процессов блоков б и 8. На входы ключей 26-28 подключено постоянное напряжение с выхода блока 4 для формирования одного полупериода выходного напряжения, а с выхода блока 5 подключено ко входам ключей 29-31 блока 2 постоянное напряжение противоположной выходному напряжению полярности блока 4 для формирования другого полупериода выходного напряжения .

Таким образом, предлагаемое устрой ство проще, так как оно не содержит специальные нестандартные узлы преобразователя код-ансшог.

Формула изобретения

генератора тактовой частоты и ко входу тактирования йервого такта датчика времени, выход линии задержки второго такта подключен ко входу тактирования реверсивного двоичного

5 счетчика и ко входу линии задержки третьего такта, а выход линии задержки третьего такта подключен ко входу тактирования Т-триггера и ко входу тактирования третьего такта датчика

Q времени, выхо; датчика времени подключены к счетному входу Т-триггера, к счетному входу реверсивного двоичного счетчика и к управляющим входам реверсивного двоичного счетчика, а каждый выход реверсивного двоичного счетчика подсоединен ко входам двух двухвходовых логических элементов И, к которым также подключены выходы Т-триггера.

времени содержит реверсивный сдвигающий регистр с тактирующим и управляющими входами, RS-триггер с информационными и тактирукяцим входгьми,

5 вспомогательные двухвходовые логические элементы И, логические элементы ИЛИ, причем выходы реверсивного сдвигающего регистра подключены ко входам логических элементов ИЛИ и к

Q информационным входам RS-триггера, входы логических элементов И подключены к выходам RS-триггера и к выходам логических элементов ИЛИ, выходы вспомогательных логических элементов И подключены ко входам логического

5 элемента ИЛИ, а выходы RS-триггера подсоединены к управляющим цепям реверсивного сдвигаквдего регистра.

г содержит резистор обратной связи и операционный усилитель с инвертирующим и неинвертирующим входами, причем резистор обратной связи подключен к выходу операционного усилителя и к инвертирующему входу

0 операционного усилителя, а неинвертирующий вход операционного усилителя подключен к общей точке устройства, выходы задатчика уровня постоянного напряжения и инвертирующего усилителя с единичным усилением подключены ко входам ключей с двухсторонней проводимостью, выходы этих ключей через весовые резисторы подключены к инвертирующему входу операционного усилителя, а их управлянвдие цепи - к выходу цифро-функционального генератора.

Источники информации, принятые во внимание при экспертизе

Фиг. /

u.l.t w««. Kte flwx/7 I I И М I I I М I И I I I t I И I I MM It I I M I I M I I I I I I I I M I M M n M M I I I I I I I I I I I I I И I M I M I M I M t I

УЛ«

/1

Авторы

Даты

1981-02-28—Публикация

1978-11-28—Подача