(54) УСТРОЙСТВО ДЛЯ ПОВЕРКИ ЦИФРОВЫХ ПРИБОРОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для поверки цифровых измерителей девиации фазы | 1990 |

|

SU1781651A1 |

| Устройство для автоматической поверки цифровых преобразователей | 1976 |

|

SU651279A1 |

| СПОСОБ АВТОМАТИЧЕСКОЙ ПОВЕРКИ СТРЕЛОЧНЫХ ИЗМЕРИТЕЛЬНЫХ ПРИБОРОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2009 |

|

RU2404440C1 |

| Устройство для автоматизированной поверки измерительных приборов | 1982 |

|

SU1051478A2 |

| Способ автоматической поверки стрелочных измерительных приборов и устройство для его осуществления | 1986 |

|

SU1383242A1 |

| Устройство для поверки цифровых приборов | 1987 |

|

SU1437818A1 |

| Устройство для проверки цифровых приборов | 1988 |

|

SU1599817A2 |

| Устройство для автоматизированной поверки измерительных приборов | 1986 |

|

SU1348761A1 |

| Устройство для поверки цифровых приборов | 1985 |

|

SU1337844A1 |

| ВСЕСОЮЗНАЯ ?^'ТШТ^О"]?лЩг'Г'ш^; | 1973 |

|

SU361453A1 |

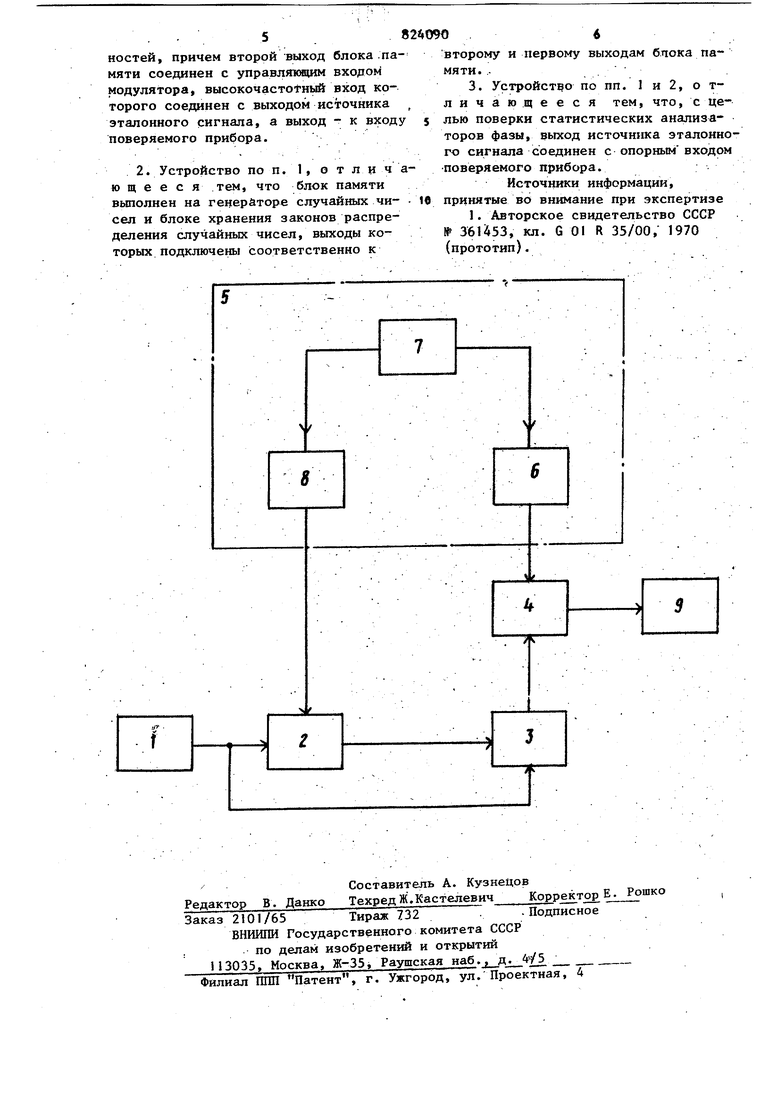

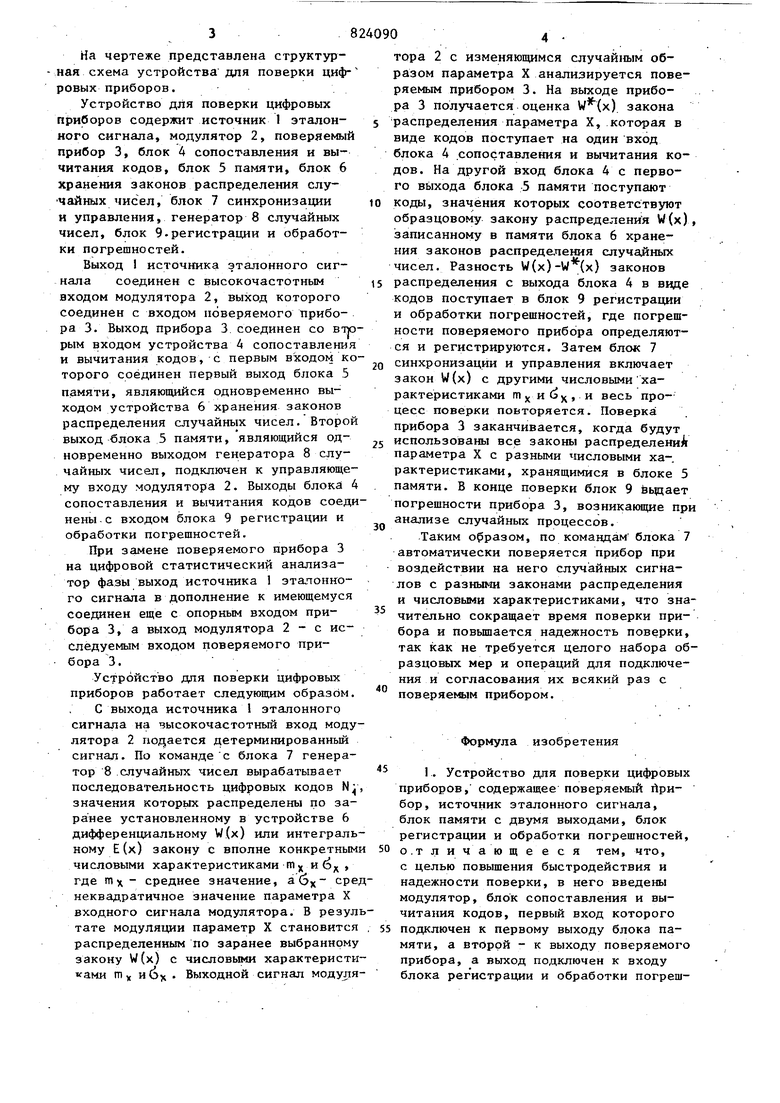

Изобретение относится к измеритед ной технике и используется для повер ки статистических анализаторов, имею щих выходные кодовые сигналы, соответствующие их показаниям или резуль татам измерения. Известно устройство, содержащее поверяемый прибор, источник эталонно го сигнала, блок памяти с двумя выхо дамй, блок регистрации и обработки погрешностей Q Недостатками данного устройства является низкая надежность и низкое быстродействие. Цель предпагаемого изобретения заключается в повышении быстродействия и надежности поверки .. Для достижения указанной цели в устройстве для поверки цифровых приборов, содержащее поверяемый прибор, источник эталонного сигнала, блок памяти с двумя выходами, блок регистрации и обработки погрешностей, введены модулятор, блок сопоставления и вычитания кодов, первый вход которого подключен к первому выходу блока памяти, второй - к выходу поверяемого прибора, а выход подключен к входу блока регистрации и обработки погрешностей, причем второй выход блока памяти соединен с управляющим входом модулятора, высокочастотный вход которого соединен с выходом источника эталонного сигнала, а выход подключен к входу поверяемого прибора. Блок памяти выполнен на генераторе случайных чисел и блоке хранения законов распределения случайных чисел, выходы которых подключены соответственно к второму и первому выходам блока памяти.. Кроме того, с цф1ью поверки статистических -анализаторов фазы, выход источника эталонного сигнала соединен с опорным входом поверяемого приора. На чертеже представлена структур- ная схема устройствадля поверки цифровых приборов. Устройство для поверки цифровых приборов содержит источник 1 эталонного сигнала, модулятор 2, поверяемый прибор 3, блок 4 сопоставления и вычитания кодов, блок 5 памяти, блок 6 хранения законов распределения случайных чисел, блок 7 синхронизации и управления, генератор 8 случайных чисел, блок 9.регистрации и обработки погрешностей. Выход 1 источника эталонного сигнала соединен с высокочастотным входом модулятора 2, выход которого соединен с входом поверяемого прибора 3. Выход прибора 3. соединен со вто рым входом устройства 4 сопоставления и вычитания кодов, с первым входом ко торого соединен первый выход блока 5 памяти, являющийся одновременно выходом устройства 6 хранения законов распределения случайных чисел. Второй выход блока 5 памяти, являющийся одновременно выходом генератора 8 случайных чисел, подключен к управляющему входу модулятора 2. Выходы блока сопоставления и вычитания кодов соеди нены -с входом блока 9 регистрации и обработки погрешностей. При эамене поверяемого прибора 3 на цифровой статистический анализатор фазы выход источника 1 эталонного сигнала в дополнение к имеющемуся соединен еще с опорным входом прибора 3, а выход модулятора 2-е исследуемым входом поверяемого прибора 3. Устройство дпя поверки цифровых приборов работает следующим образом. С выхода источника 1 эталонного сигнала на высокочастотный вход моду лятора 2 подается детерминированный сигнал. По командес блока 7 генератор 8 .случайных чисел вырабатывает последовательность цифровых кодов N значения которых распределены по заранее установленному в устройстве 6 дифференциальному W(x) или интеграль ному Е(х) закону с вполне конкретным числовыми характеристиками rrijj и б где Шх - среднее значение, а6х сре неквадратичное значение параметра X входного сигнала модулятора. В резул тате модуляции параметр X становится распределенным по заранее выбранном закону W(x) с числовыми характерист f ами m у и (Sx Выходной сигнал модул тора 2 с изменяющимся случайным образом параметра X анализируется поверяемым прибором 3. На выходе прибора 3 получается оценка (x) закона распределения параметра X, которая в виде кодов поступает на один вход блока 4 сопоставления и вычитания кодов. На другой вход блока 4 с первого выхода блока 5 памяти поступают коды, значения которых соответствуют образцовому закону распределения W(x), ;записанному в памяти блока 6 хранения законов распредепения случайных чисел. Разность W(x)-W(x} законов распределения с выхода блока 4 в ввде кодов поступает в блок 9 регистрации и обработки погрешностей, где погрешности поверяемого прибора определяются и регистрируются. Затем блок 7 синхронизации и управления включает закон W(x) с другими числовыми характеристиками m X и j X и весь процесс поверки повторяется. Поверка прибора 3 заканчивается, когда будут использованы все законы распределений параметра X с разными числовыми ха-. рактеристиками, хранящимися в блоке 5 памяти. В конце поверки блок 9 йьщает погрешности прибора 3, возникающие при анализе случайных процессов. Таким образом, по командам блока 7 автоматически поверяется прибор при воздействии на него Случайных сигналов с разньлни законами распределения и числовыми характеристиками, что значительно сокращает время поверки прибора и повьш1ается надежность поверки, так как не требуется целого набора образцовых мер и операций для подключения и согласования их всякий раз с поверяемым прибором. Формула изобретения 1. Устройство для поверки цифровых приборов, содержащее поверяемый йрибор, источник эталонного сигнала, блок памяти с двумя выходами, блок регистрации и обработки погрешностей, о.тличающе еся тем, что, с целью повышения быстродействия и надежности поверки, в него введены модулятор, блок сопоставления и вычитания кодов, первый вход которого подключен к первому выходу блока памяти, а второй - к выходу поверяемого прибора, а выход подключен к входу блока регистрации и обработки погрешностей, причем второй выход блока .памяти соединен с управлякяцим входом модулятора, высокочастотный вход которого соединен с выходом источника эталонного сигнала, а выход - к входу поверяемого прибора.

второму и первому выходам блока памяти. 3. Устройство по пп. 1 и 2, отличающееся тем, что, с целью поверки статистических анализаторов фазы, выход источника эталонного сигнала соединен с опорным входом поверяемого прибора..

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-04-23—Публикация

1979-07-11—Подача