1

Изобретение относится к вычислительной технике и может использоваться в устройствах контроля узлов синхронизации и кодирования.

Известно устройство для выделения ошибок из М-последовательностей, содержащее ключ, регистр сдвига, селектор, полусумматоры и счетчик совпадений 1 ,

Однако такое устройство обладает недостаточной точностью контроля.

Известно также устройство выделения ошибок из испытательног-о Т1севдослучайного сигнала, работа которого основана на умножении исследуемой М-последовательности с периодом 2-1 на ее порождающий многочлен, делении последовательности, полученной в результате умножения, (непрерывно на порожданвдий многочлен пРИ наличии п+1 тактах сигналов М-последовательности и последовательности, полученной в результате умножения) прекращении деления при отсутствии последних и регистрации ошибок 2.

Недостатком известного устройства яв.пяется то, что в блок умножения iM-последовательности на ее порождающий многочлен входит такой же генератор М-последовательности, то есть

появление сбоев в генераторе исследуемой М-последовательности и блоке умножения М-последовательности на ее порождающий многочлен равновероятно.

Наиболее близким по технической сущности к изобретению является устройство для контроля формирователей М-11оследовательностей, содержащее регистр сдвига, .между выходами со0ответствукяцих разрядов и входом которого включен блок прямого сдвига кода, элемент сравнения, блок обратного сдвига кода и элемент задерж-. ки f4j ,

5

Недостатком устройства является то, что элемент сравнения работает на частоте генерируемой м-последоватёльности что затрудняет определение единичных сбоев в устройстве

0 при работе генератора на высокой тактовой частоте, а также необходимость и сложность расчета алгоритма работы блока обратного сдвига кода и элемента задержки.

5

Цель изобретения - упрощение устройства за счет некритичности его работы к фазам сравниваемых последователь ндстей .

Поставленная цель достигается тем,

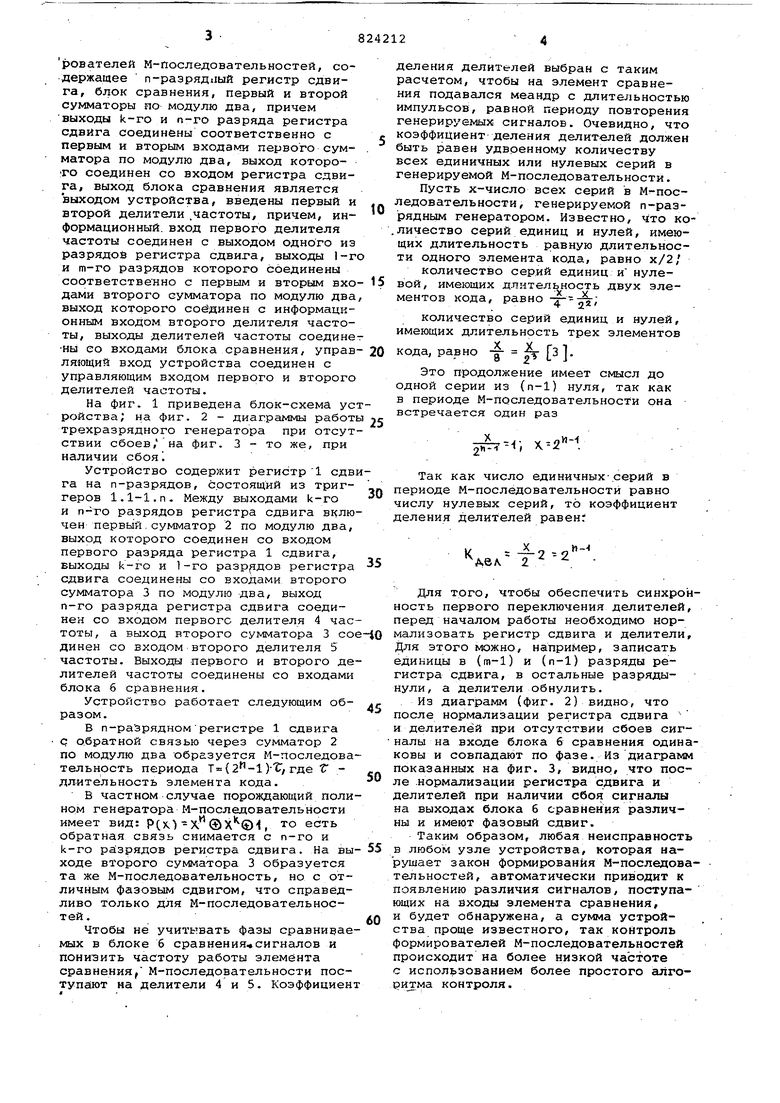

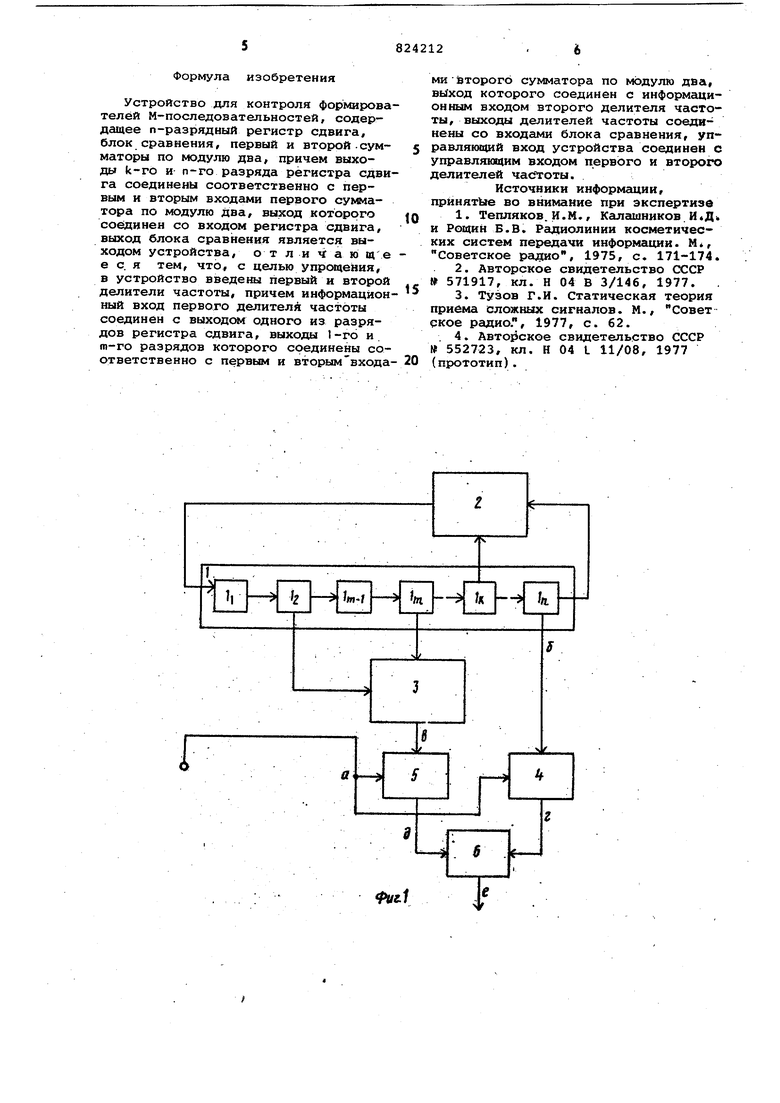

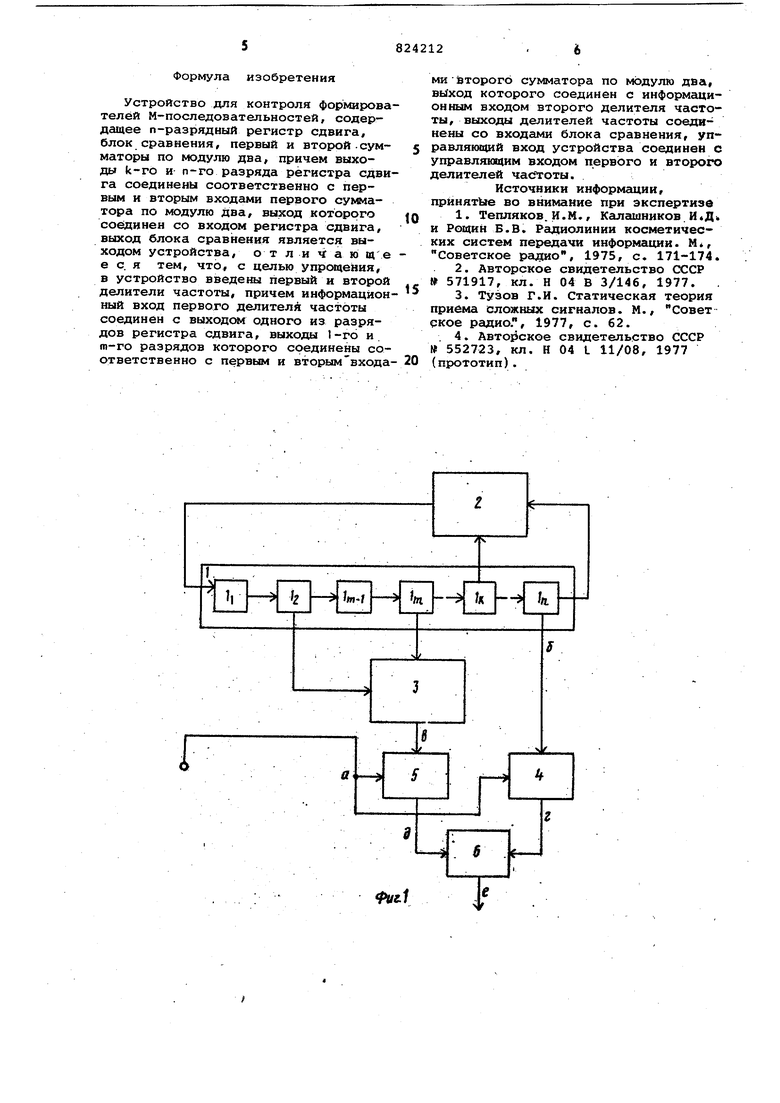

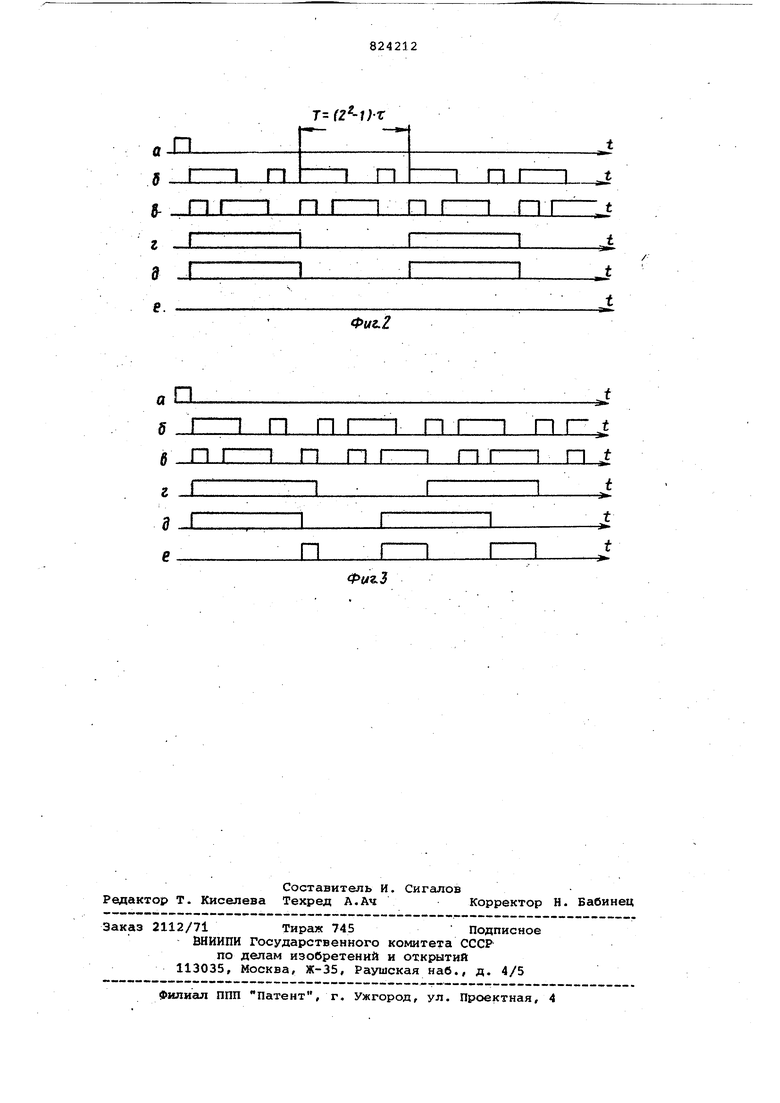

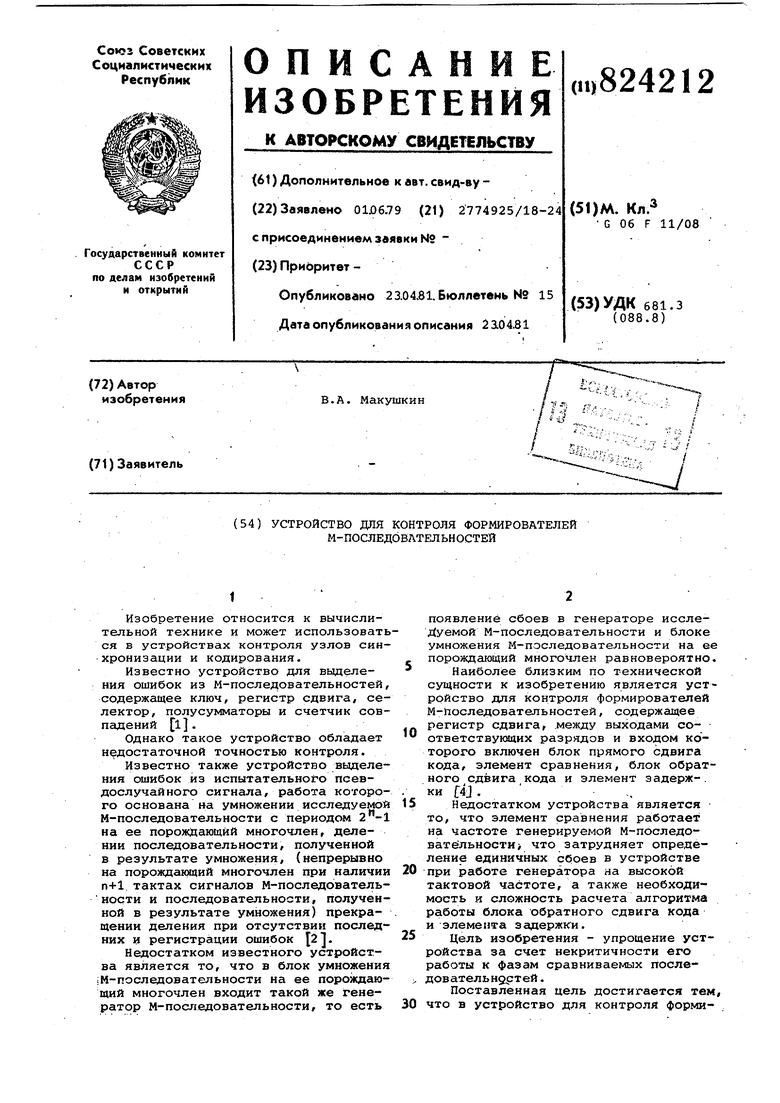

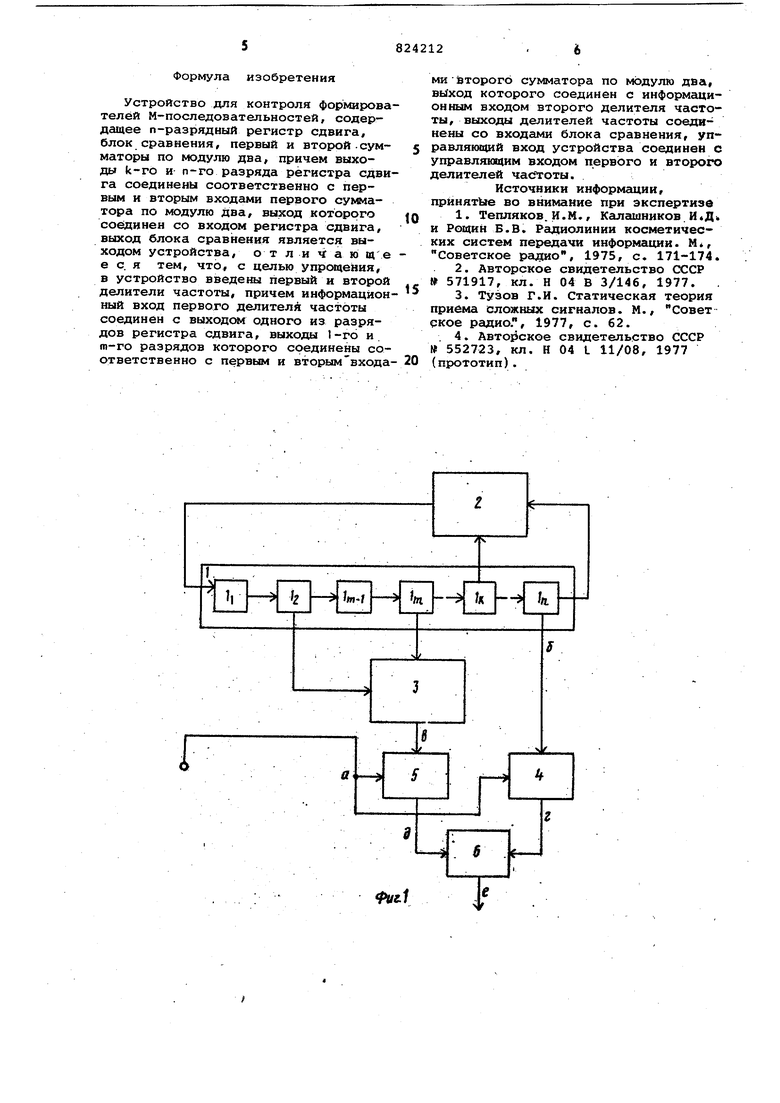

0 что в устройство для контроля формирователей М-последовательностей, содержащее п-разрядный регистр сдвига, блок сравнения, первый и второй сумматоры по модулю два, причем выходы k-ro и п-го разряда регистра сдвига соединены соответственно с первым и вторым входами первого сумматора по модулю два, выход которого соединен со входом регистра сдвига, выход блока сравнения является выходом устройства, введены первый и второй делители .частоты причем, информационный, вход первого делителя частоты соединен с выходом одного из разрядов регистра сдвиха, выходы 1-г и т-го разрядов которого соединены соответственно с первым и вторым вхо дами второго сумматора по модулю два выход которого соединен с информационным входом второго делителя частоты, выходы делителей частоты соедине ны со входами блока сравнения, управ ляющий вход устройства соединен с управляющим входом первого и второго делителей частоты. На фиг. 1 приведена блок-схема ус ройства; на фиг. 2 - диаграммы работ трехразрядного генератора при отсут ствии сбоев, на фиг. 3 - то же, при наличии сбоя Устройство содержит регистр 1 сдв га на п-разрядов, состоящий из триггеров 1.1-1.п. Между выходами k-ro и п-го разрядов регистра сдвига вклю чен первый . сумматор 2 по модулю два, выход которого соединен со входом первого разряда регистра 1 сдвига, выходы k-ro и 1-го разрядов регистра сдвига соединены со входами второго сумматора 3 по модулю два, выход п-го разряда регистра сдвига соединен со входом первого делителя 4 час тоты, а выход второго сумматора 3 co динен со входом второго делителя 5 частоты. Выходы первого и второго де лителей частоты соединены со входами блока б сравнения. Устройство работает следующим образом. В п-разрядномрегистре 1 сдвига с обратной связью через сумматор 2 по модулю два образуется М-последова тельнрсть периода )-tr, где f длительность элемента кода. В частном случае порождающий поли ном генератора М-последовательности имеет вид: Р(х.) , то есть обратная связь снимается с п-го и k-ro ра:зрядав регистра сдвига. На вы ходе второго сумма-тора 3 образуется та же М-последовательность, но с отличным фазовым сдвигом, что справедливо только для М-последовательностей. Чтобы не учитывать фазы сравнивае мых в блоке 6 сравнения сигналов и понизить частоту работы элемента сравнения, М-последовательности поступают на делители 4 и 5. Коэффициен деления делителей выбран с таким расчетом, чтобы на элемент сравнения подавался меандр с длительностью импульсов, равной периоду повторения генерируемых сигналов. Очевидно, что коэффициент деления делителей должен быть равен удвоенному количеству всех единичных или нулевых серий в генерируемой М-последовательности, Пусть х-число всех серий в М-последовательности, генерируемой п-раэрядным генератором. Известно, что количество серий единиц и нулей, имеющих длительность равную длительности одного элемента кода, равно х/2, количество серий единиц и нулевой, имеющих длительность двух элементов кода, равно количество серий единиц и нулей, имеющих длительность трех элементов кода, равно в з . Это продолжение имеет смысл до одной серии из (п-1) нуля, так как в периоде М-последовательности она встречается один раз -JL, .{-nH-l 2 -1 Так как число единичных-серий в периоде М-последовательностИ равно числу нулевых серий, то коэффициент деления делителей равенг I/ JLn . 2 . Для того, чтобы обеспечить синхронность первого переключения делителей, перед началом работы необходимо нормализовать регистр сдвига и делители. Для этого можно, например, записать единицы в (т-1) и (п-1) разряды регистра сдвига, в остальные разрядынули, а делители обнулить. Из диаграмм (фиг. 2) видно, что после нормализации регистра сдвига и делителей при отсутствии сбоев сигналы на входе блока б сравнения одинаковы и совпадают по фазе. Из диаграмм показанных на фиг. 3, видно, что после .нормализации регистра сдвига и делителей при наличии сбоя сигналы на выходах блока б сравнения различны и фазовый сдвиг. Таким образом, любая неисправность в любом узле устройства, которая нарушает закон формирования М-послеДовательностей, автоматически приводит к появлению различия сигналов, поступающих на входы элемента сравнения, и будет обнаружена, а сумма устройства проще известного, так контроль формирователей М-последовательностей происходит на более низкой частоте с использованием более простого алгоpиJмa контроля. Формула изобретения Устройство для контроля формирова телёй М-последовательностей, содер- дащее п-разрядный регистр сдвига, блок сравнения, первый и второй-сумматоры по модулю два, причем выходы k-ro и п-го разряда регистра сдви га соединены соответственно с первым и вторым входами первого сумматора по модулю два, выход которого соединен со входом регистра сдвига, выход блока сравнения является выходом устройства, о т л и ч а ю щ е е с. я тем, что, с целью упрощения, в устройство введены первый и второй делители частоты, причем информацйон ный вход первого делителя частоты соединен с выходом одного из разрядов регистра сдвига, выхода 1-го и т-го разрядов которого соединены соответственно с первым и вторымвхода мивторого сумматора по модулю два, выход которого соединен с информационным входом второго делителя частоты, выходы делителей частоты соединены со входами блока сравнения, управлякнций вход устройства соединен с управляющим входом первого и второго делителей частоты. Источники информации, принятие во внимание при экспертизе 1.Тепляков. И.М., Калашников.И«Д и Рощин Б.В. Радиолинии косметических систем передачи информации. М , Советское радио, 1975, с. 171-174. 2.Авторское свидетельство СССР 571917, кл. Н 04 В 3/146, 1977. 3.Тузов Г.И. Статическая теория приема сложных сигналов. М., Совет ское радио, 1977, с. 62. 4.Авторское свидетельство СССР № 552723, кл. Н 04 L 11/08, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления синдромов кода Рида-Соломона | 1990 |

|

SU1751860A1 |

| Устройство для умножения в конечных полях | 1982 |

|

SU1061134A1 |

| Устройство для кодирования линейных полиномиальных кодов | 1989 |

|

SU1711338A1 |

| Декодер циклического кода | 1988 |

|

SU1599996A1 |

| Устройство для деления многочлена на многочлен | 1980 |

|

SU951298A1 |

| Устройство для кодирования циклических кодов | 1988 |

|

SU1569997A1 |

| Устройство для умножения элементов конечных полей | 1984 |

|

SU1226445A1 |

| Многовходовой сигнатурный анализатор | 1987 |

|

SU1478219A1 |

| Генератор псевдослучайных последовательностей | 1984 |

|

SU1228236A1 |

| УСТРОЙСТВО ДЕКОДИРОВАНИЯ ЦИКЛИЧЕСКОГО КОДА ХЕММИНГА | 2004 |

|

RU2270521C1 |

if

r-(

s.

Фиг.2

Фиг.3

Авторы

Даты

1981-04-23—Публикация

1979-06-01—Подача