9,

Вт 7,

Мг- .

Отб,-

Мп

Яг

I- Qml,4

Ь : в,

э

оо

1C

со

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с контролем информации | 1984 |

|

SU1288758A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1185338A1 |

| МНОГОКАНАЛЬНЫЙ СИГНАТУРНЫЙ АНАЛИЗАТОР | 1995 |

|

RU2087030C1 |

| Генератор цифровых последовательностей | 1987 |

|

SU1513449A1 |

| Счетчик | 1986 |

|

SU1422403A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

| Устройство для деления многочленов | 1986 |

|

SU1483461A1 |

| Устройство для исправления ошибок | 1984 |

|

SU1216832A1 |

| Устройство для умножения полиномов над конечными полями GF (2 @ ) по модулю неприводимого многочлена | 1989 |

|

SU1661759A1 |

| Генератор тестовых последовательностей | 1986 |

|

SU1388999A1 |

Изобретение относится к вычислительной технике и может найти применение в системах контроля и диагностирования цифровых устройств. Целью изобретения является повышение быстродействия. Анализатор содержит высокочастотные входы 1, тактовый вход 2, выходы 3 регистров, к групп из N блоков 4 умножения по модулю L, к блоков 5 сложения по модулю L, предназначенных для объединения входной последовательности данных с текущим значением сигнатуры, к блоков 6 деления по модулю L, N регистров 7, предназначенных для хранения сигнатур, блоков 8 ортогональной памяти, к групп 9 параллельных выходов блока ортогональной памяти, делитель 10 тактовой частоты для получения внутренней тактовой частоты анализатора. Блок 8 ортогональной памяти содержит к регистров сдвига для преобразования входной двоичной последовательности из последовательного кода в параллельный и к буферных регистров. 1 з.п. ф-лы, 2 ил.

-т

31

ЦЬ

Г

Г Г Г- Г

х&чг)

г I

3

ъ

-э

Г

Изобретение относится к вычислительной технике и может быть использовано в системах контроля и диагностирования цифровых устройств.

Целью изобретения является повышение быстродействия.

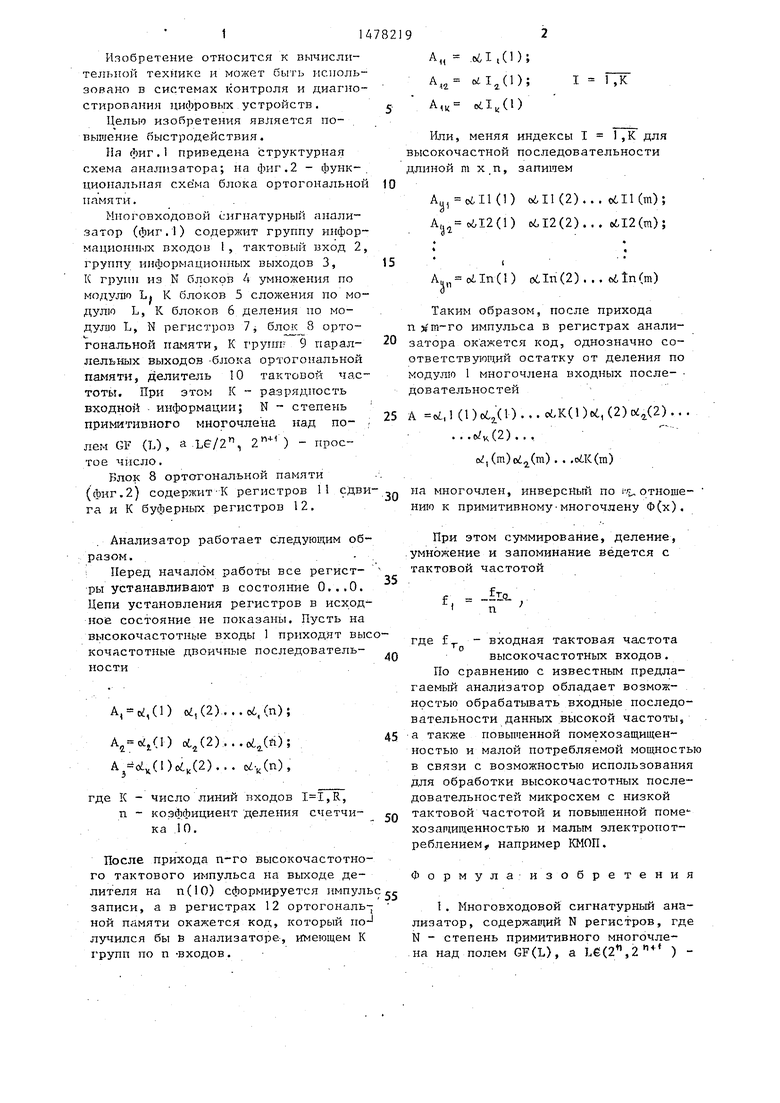

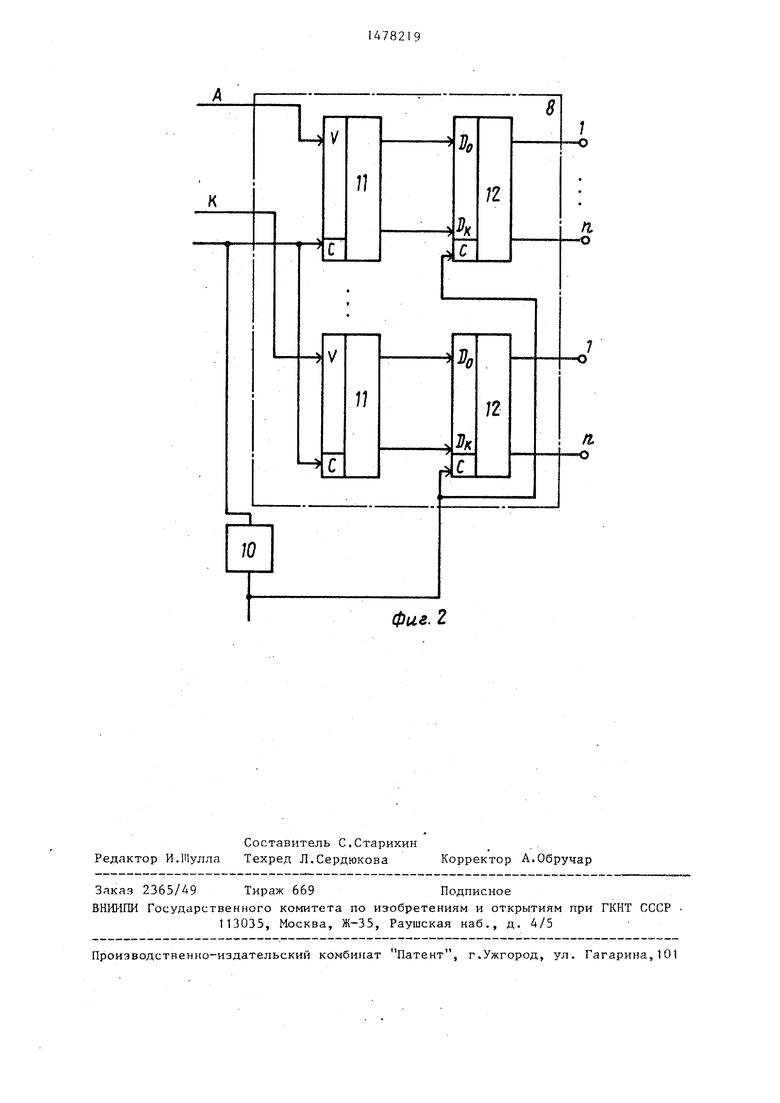

На фиг.1 приведена структурная схема анализатора; на фиг.2 - функциональная схе ма блока ортогональной памяти.

Мпоговходовой t игнатурный анализатор (фиг.1) содержит группу информационных входов 1, тактовый вход 2, группу информационных выходов 3, К групп из N блоков 4 умножения по модулю L. К блоков 5 сложения по модулю L, К блоков 6 деления по модулю L, N регистров 7, блок 8 ортогональной памяти, К групп 9 параллельных выходов блока ортогональной памяти, делитель 10 тактовой частоты. При этом К - разрядность входной информации; N - степень примитивного многочлена над полем GF (L), a , ) - простое число.

Блок 8 ортогональной памяти (фиг.2) содержит К регистров 11 сдвига и К буферных регистров 12.

Анализатор работает следующим образом.

Перед началом работы все регист- ры устанавливают в состояние 0...0. Цепи установления регистров в исходное состояние не показаны. Пусть на высокочастотные входы 1 приходят выс кочастотные двоичные последовательности

А, «,() ci,(2)...o6,(n);

A2(D 44(2)...oi4(ft); А 0(1)0(2)... oi-K(n),

где К - число линий входов ,R, п - коэффициент деления счетчика 10.

После прихода n-го высокочастотного тактового импульса на выходе делителя на п(10) сформируется импульс« записи, а в регистрах 12 ортогональ- ной памяти окажется код, который noj лучился бы в анализаторе, имеющем К групп по п -входов.

А„ об1 ,(1); etI4(l); А,к cilk(l)

Т 1 ,К

Или, меняя индексы I 1,К для высокочастной последовательности длиной m х п, запишем

Ад, et Ll(l) о611 (2)... ctll(m); (1) Л 12(2)... еЫ2(т);

А„ oiln(l) can (2). .. oiln(m)

d

Таким образом, после прихода п jf m-ro импульса в регистрах анализатора окажется код, однозначно соответствующий остатку от деления по модулю 1 многочлена входных последовательностей

A et,l (1Ы1(1)...ЛК(1)е61(2)(2)... ...в/к (2)...

((пОоЦОтг). . .oiK(m)

на многочлен, инверсный по отношению к примитивному многочлену Ф(х).

При этом суммирование, деление, умножение и запоминание ведется с тактовой частотой

гя.

п

ч

40

45

50

«

где f.

- входная тактовая частота

высокочастотных входов. По сравнению с известным предлагаемый анализатор обладает возможностью обрабатывать входные последовательности данных высокой частоты, а также повышенной помехозащищенностью и малой потребляемой мощностью в связи с возможностью использования для обработки высокочастотных последовательностей микросхем с низкой тактовой частотой и повышенной поме1- хозапщщенностью и малым электропотреблением, например КМОП.

Формула изобретения

I. Многовходовой сигнатурный анализатор, содержащий N регистров, где N - степень примитивного многочлена над полем GF(L), a L6(2tl,2 ) простое число, К блоков сложения по модулю L, где К - разрядность входной информации, К блоков деления по модулю L, К групп из N блоков умножения по модулю N, причем входы з-го блока сложения по модулю L(, К) соединены с входами i-ro блока деления по модулю L, выходы которого соединены с информационными входами (K-i+I)-го регистра и с входами j-гр блока умножения по модулю L, j ,i(K+j-i)-ft группы, выходы 1-го регистра, 1,N, соединены с входами m-го блока умножения по модулю L, ,N-1+1, т-й группы, группа информационных входов Р-го регистра, ,N, соединена с группой выходов (Р-К)-го регистра, группы выходов блоков умно- жения по модулю L i-й группы соединены с соответствующими группами входов 1-го блока сложения по модулю два, отличающийся тем, что, с целью повышения быстродейст- вия, анализатор содержит блок ортогональной памяти и депитель тактовой частоты, причем группа информационных входов блока ортогональной

0

S

0 5

памяти является соот стгтпукгдей группой входов анализатора, 1-я группа информационных выходов блока ортогональной памяти соединена с (К+1)-й группой входов 1-го сумматора по модулю L,вход делителя тактовой частоты соединен с первым так-1- товым входом блока ортогональной памяти и образует тактовый вход анализатора, выход делителя тактовой частоты соединен с вторым тактовым входом блока ортогональной памяти к с синхровходами регистров,

фиг. 2

| Устройство для контроля двоичных последовательностей | 1983 |

|

SU1116431A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальный сигнатурный анализатор | 1984 |

|

SU1185338A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-05-07—Публикация

1987-04-06—Подача