(54) УСТРОЙСТВО ДЛЯ ИНДИКАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для цифровой индикации | 1975 |

|

SU549820A1 |

| УСТРОЙСТВО ДЛЯ ЦИФРОВОЙ ИНДИКАЦИИв п т в^!1П <^-'ч''^^!^'^'^ЛП|НД sj;ii>&;li:e^i08 | 1973 |

|

SU399858A1 |

| Устройство для индикации | 1980 |

|

SU928398A1 |

| Способ компенсации погрешностей акустических локационных уровнемеров и устройство для его осуществления | 1985 |

|

SU1529047A1 |

| Устройство для отображения знакографической информации | 1987 |

|

SU1439673A1 |

| Устройство для индикации | 1979 |

|

SU873265A1 |

| Устройство горизонтального отклонения электронно-лучевого осциллографа | 1986 |

|

SU1370572A2 |

| Цифровые первичные часы | 1976 |

|

SU600508A1 |

| ИЗМЕРИТЕЛЬ УРОВНЯ | 1992 |

|

RU2029248C1 |

| Цифровой частотомер с нониусной интерполяцией | 1980 |

|

SU868612A1 |

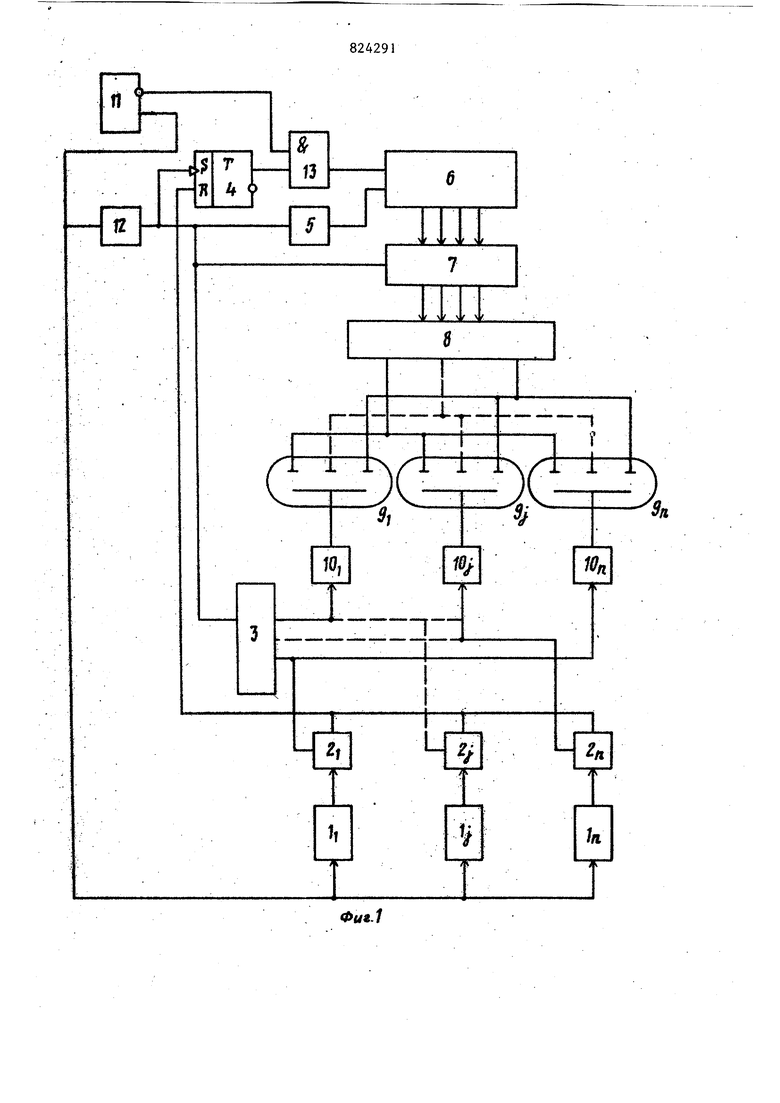

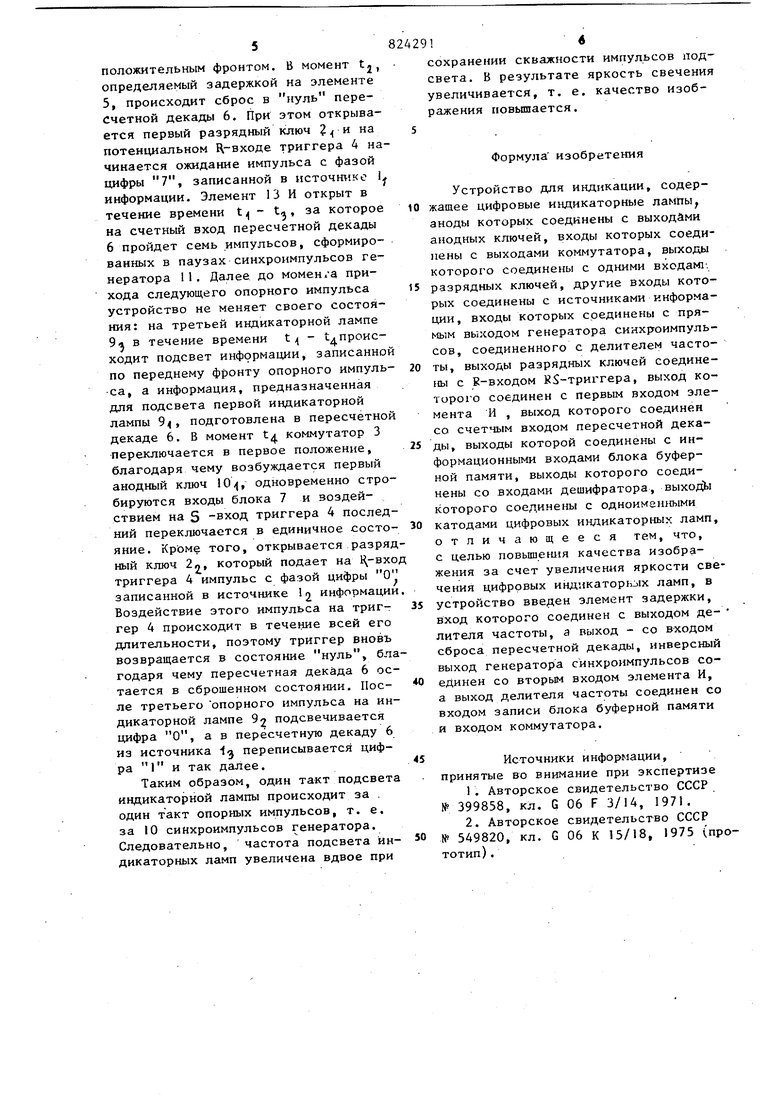

Изобретение относится к автоматике и вычислительной технике и может быть использовано для визуального представления информации. Известны устройства для цифровой индикации, работающие по принципу динамической индикации, содержащие источники информации, цифровые индикаторные лампы, анодные формирователи, коммутатор, блок управления, пересчетную декаду и дешифратор |. Недостатком этих устройств является зависимость скважности импульсо подсвета ивдикаторов от состояний ис точников информации. Наиболее близким к предлагаемому по технической сущности является уст ройство для цифровой индикации, соде ржащее цифровые индикаторные лампы, аноды которых соединены с выходами анодных формирователей, одноиме ные катоды объединены и подключены к выходам дешифратора, входы инфор|мации которого подключены к соответствующим выходам буферного запоминающего блокад пересчетную триггерную декаду, выходы которой подключены к соответствующим входам буферного запоминающего блока, счетный вход - к управляемому выходу блока управления, у которого второй выход синхроимпульсов подключен ко входам источников информации; разрядные ключи, входы которых соединены с выходами соответствующих источников информации, а выходы объединены и подключены ко входу остановки пересчета блока управления; коммутатор, у которого вход объединен со входом записи информации буферного запс шнающего устройства, каждый выход соединен с входами соотвётствуюпщх анодных формирователей и управляющими входами последующих разрядных ключей, а последний выход коммута тора - с управляющим входом первого разрядного ключа. в этом устройстве введен1- ый двухтактный формирователь импульсов преобразует один импульс опорной последовательности в импульс управлеьшя буферным запоминающим блоком и коммутатором (смена информации и адреса), следующий импульс - в импульс сброса триггерной декады и пересчета в нее импульсов блока управления (подготовка и запись информации для подсвета следующей индикаторной лампы) . Один такт подсвета происходит за два такта импульсов опорной последовательности, т. е. за 20 импульсов генератора в блоке управления Г22. Целью изобретения является повышение качества изображения за счет увеличения яркости свечения индикаторных ламп. Поставленная цель достигается тем, что в устройстве исключен двухтактный формирователь и введен элемент задержки, вход которого подключен к вых.оду делителя частоты, а выход - ко входу сброса пересчетной триггерной декады. На элемент И подключается не прямой, а инверсный выход генератора. Цепь входов коммутатора и записи информации блока буфер ной памяти подключается к выходу делителя частоты. При этом смена информации в блок буферной памяти и адреса в коммутаторе, а также сброс пересчетнои три герной декады осуществляется в тече ние импульса опорной последовательности, с делителя частоты, а запись информации для подсвета следующего индикатора в пересчетную триггерную декаду - в течение паузы между указан ными импуль с ами. На фиг. 1 показана структурная схема устройства; на фиг. 2 - временные диаграммы его работы. Предлагаемое устройство содержит индицируемые источники 1 - 1 rj информации, выполненные на фазоимпульс ных многоустойчивых элементах, к вы . ходу KoToptJx подключены разрядные ключи 2 - 2, управляемые коммутатором 3, Каждый выход коммутатора 3 соединен ,с управляющим входом после дующего разрядного ключа, а последний выход - с управляющим входом пе вого ключа 2, Выходы разрядных ключей объединены и подключены к Д914входу триггера 4 для остановки пересчета . элемента 5 задержки подключен ко входу сброса пересчетной декада 6, выходы которого соединены с информационными входами блока 7 буферной памяти. Выходы последнего через дешифратор 8 связаны с объединенными цифровыми катодами индикаторных ламп 9 - 9, аноды которых через анодные ключи Ю - lOj, соединены с соответствующими выходами коммутатора 3. У генератора II синхроимпульсов прямой выход подключен ко входам источников 1 ц - ко входу делителя I2 частоты, а инверсный выход - к первому входу элемента 13 И, второй вход которого соединен с выходом, триггера 4, а выход - со счетным входом пересчетной декады 6. Делитель 12 частоты вырабатывает управляющую опорную последовательность импульсов, находящихся в фазе с импульсами цифры О от источников Ц - Ifj информации. Выход делителя 12 частоты подключен к счетному входу коммутатора 3j к 5 -входу , триггера 4 для разрешения пересчета ко входу элемента 5 задержки для сброса пересчетной декады 6, ко входу записи блока 7 буферной памяти для смены информации в нем методом вытеснения. На эпюрах а - е (фиг. 2) показаны временные диаграммы в наиболее характерных точках. На эпюре а показаны импульсы прямого выхода генератора 11, на эпюре б - импульсы опорной последовательности, сформированные делителем 12 частоты, на эпюре & - импульсы на выходе элемента 5 задержки. На эпюре г показаны импульсы на К,-входе триггера 4, на эпюре д - импульсы на выходе триггера 4, на эпюре е - серии импульсов на входе пересчетнои декады 6. Устройство работает следующим образом. В момент t появляется импульс опорной последовательности на выходе делителя 12, по переднему фронту которого коммутатор 3 переключается в третье (последнее) положение, блок 7 буферной памяти осуществляет прием информации из пересчетной дека- i ды 6, а на динамический S -вход триггера 4 опорный импульс воздействует положительным фронтом. В момент t определяемый задержкой на элементе 5, происходит сброс в нуль пересчетной декады 6. При этом открывается первый разрядный ключ и на потенциальном Я-входе триггера 4 на чинается ожидание импульса с фазой цифры 7, записанной в источт кс информации. Элемент 13 И открыт в течение времени t - t, за которое на счетный вход пересчетной декады 6 пройдет семь импульсов, сформированных в паузах синхроимпульсов генератора 11. Далее до момен/а прихода следующего опорного импульса устройство не меняет своего состояния: на третьей индикаторной лампе 9- в течение времени t. происходит подсвет информации, записанно по переднему фронту опорного импуль са, а информация, предназначенная для подсвета первой индикаторной лампы 9, подготовлена в пересчетно декаде 6. В момент t коммутатор 3 переключается в первое положение, благодаря чему возбуждается первый анодный ключ 10(, одновременно стро бируются входы блока 7 и воздействием на 5 -вход триггера 4 послед НИИ переключается в единичное состо яние. Кроме того, открывается разряд ный ключ 2о, который подает на триггера 4 импульс с фазой цифры О записанной в исто.чнике 12 информации Воздействие этого импульса на триггер 4 происходит в течение всей его длительности, поэтому триггер вновь возвращается в состояние нуль, бла годаря чему пересчетная декада 6 остается в сброшенном состоянии. Носле третьего опорного импульса на индикаторной лампе 92 подсвечивается цифра О, а в перёсчетную декаду 6 из источника l переписывается цифра 1 и так далее. Таким образом, один такт подсвета индикаторной лампы происходит за . один такт опорных импульсов, т. е. за 10 синхроимпульсов генератора. Следовательно, частота подсвета индикаторных ламп увеличена вдвое при 2 , сохранении скважности импульсов подсвета. В результате яркость свечения увеличивается, т. е. качество изображения повьппается. Формула изобретения Устройство для индикации, содержащее цифровые индикаторные ламПы, аноды которых соединены с выходами анодных ключей, входы которых соединены с выходами коммутатора, выходы которого соединены с одними входам -. разрядных ключей, другие входы которых соединены с источниками информации, входы которых соединены с прямым выходом генератора синхроимпульсов, соединенного с делителем частоты, выходы разрядных ключей соединеifl i с 8-входом RS-триггера, выход которого соединен с первым входом элемента И , выход которого соединен со счетным входом пересчетной декады, выходы которой соединены с информационными входами блока буферной памяти, выходы которого соединены со входами дешифратора, выходЬ которого соединены с одноименными катодами цифровых индикаторных ламп, отличающееся тем, что, с целью поБышеш1я качества изображения за счет увеличения яркости свечения цифровых индикаторных ламп, в устройство введен элемент задержки, вход которого соединен с выходом делителя частоты, а выход - со входом сброса пересчетной декады, инверсный выход генератора синхроимпульсов соединен со вторым входом элемента И, а выход делителя частоты соединен со входом записи блока буферной памяти и входом коммутатора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 399858, кл. G 06 F 3/14, 1971. 2.Авторское свидетельство СССР № 549820, кл. G 06 К 15/18, 1975 (прототип) .

Фи.1 в JlJmгlлnлJlГLШlЛJUlJlш j n jп i

r

д

.ртШПШ

«

Фиг.2

п.

Авторы

Даты

1981-04-23—Публикация

1979-05-28—Подача