1

(21)3929238/24-10

(22)12.07,85

(46) 15.12.89. Бюл. № 46

(71)Новосибирский электротехнический институт

(72)А.Д. Владимиров, Н.В. Гуляев, Г.П. Каблов и O.K. Кочергин

(53)534.232(088.8)

(56)Авторское свидетельство СССР № 690310, кл. С 01 F 23/28, 1975.

Авторское свидетельство СССР № 1160244, кл. G 01 F 23/28, 1985.

Авторское свидетельство СССР № 765659, кл. G О F 23/28, 1979.

(54)СПОСОБ КОМПЕНСА1ШИ ПОГРЕШНОСТЕЙ АКУСТШЕСКИХ ЛОКАЦИОННЫХ УРОВНЕМЕРОВ И УСТРОЙСТВО ЛЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ

(57)Изобретение относится к ультразвуковой технике и может быть использовано для измерения и контроля уровня жидкости или сыпучих веществ в емкости методом ультразвуковой локации. Целью изобретения является расширение функциональных возможностей. Отраженные от отражателя 12.и поверхности жидкости 13 реперный и измерительный ультразвуковые сигналы принимаются приемником 9 акустического датчика 8, усиливаются усилителем 10 и поступают на разделитель 11, В каждом новом цикле измерения в момент прихода реперного сигнала значение числа в регистре 16 памяти обновляется в соответствии с условиями распространения ультразвука и служит опорным числом при формировании последовательности счетных импульсов. Счетные импульсы f формируются на выходе управляемого делителя и подсчитываются декадными счетчиками делителя 4. В результате всех преобразований фиксированному расстоянию -fp всегда ставится в соответствие постоянное, кратное 10, количество счетных импульсов, что эквивалентно разбиению этого расстояния на соответствующее число элементарных долей. 1 3.п. ф-лы, 3 ил.

(/)

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ КОМПЕНСАЦИИ ПОГРЕШНОСТЕЙ АКУСТИЧЕСКИХ ЛОКАЦИОННЫХ УРОВНЕМЕРОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1995 |

|

RU2129703C1 |

| Устройство для записи параметров движения | 1984 |

|

SU1273811A1 |

| Делитель частоты с изменяемым коэффициентом деления | 1980 |

|

SU900459A2 |

| ПРЕОБРАЗОВАТЕЛЬ ДВОИЧНОГО КОДА В ДЕСЯТИЧНЫЙ | 1971 |

|

SU432486A1 |

| Счетчик импульсов с визуальной индикацией | 1978 |

|

SU767973A1 |

| Устройство для ввода-вывода информации | 1983 |

|

SU1116422A1 |

| Устройство для деления чисел | 1972 |

|

SU448461A1 |

| Счетное устройство | 1984 |

|

SU1210221A1 |

| Преобразователь цифрового кода в частоту следования импульсов | 1983 |

|

SU1169170A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

Изобретение относится к ультразвуковой технике и может быть использовано для измерения и контроля уровня жидкости или сыпучих веществ в емкости методом ультразвуковой локации. Целью изобретения является расширение функциональных возможностей. Отраженные от отражателя 12 и поверхности жидкости 13 реперный и измерительный ультразвуковые сигналы принимаются приемником 9 акустического датчика 8, усиливаются усилителем 10 и поступают на разделитель 11. В каждом новом цикле измерения в момент прихода реперного сигнала значение числа в регистре 16 памяти обновляется в соответствии с условиями распространения ультразвука и служит опорным числом при формировании последовательности счетных импульсов. Счетные импульсы Fсч формируются на выходе управляемого делителя и подсчитываются декадными счетчиками делителя 4. В результате всех преобразований фиксированному расстоянию Lр всегда ставится в соответствие постоянное, кратное 10, количество счетных импульсов, что эквивалентно разбиению этого расстояния на соответствующее число элементарных долей. 1 з.п.ф-лы, 3 ил.

rLg-.4-.X -..

ip teffe

/V

Из-обретение относится к ультразвуковой технике и может быть использовано для измерения и контроля уровня жидкости или сыпучих веществ в емкостях методом ультразвуковой локации без непосредственного контакта акустического датчика с контролируемым веществом.

Целью изобретения является расши- рение функциональных возможностей за счет компенсации ошибок измерения в больших пределах и устойчивости работы измерителя.

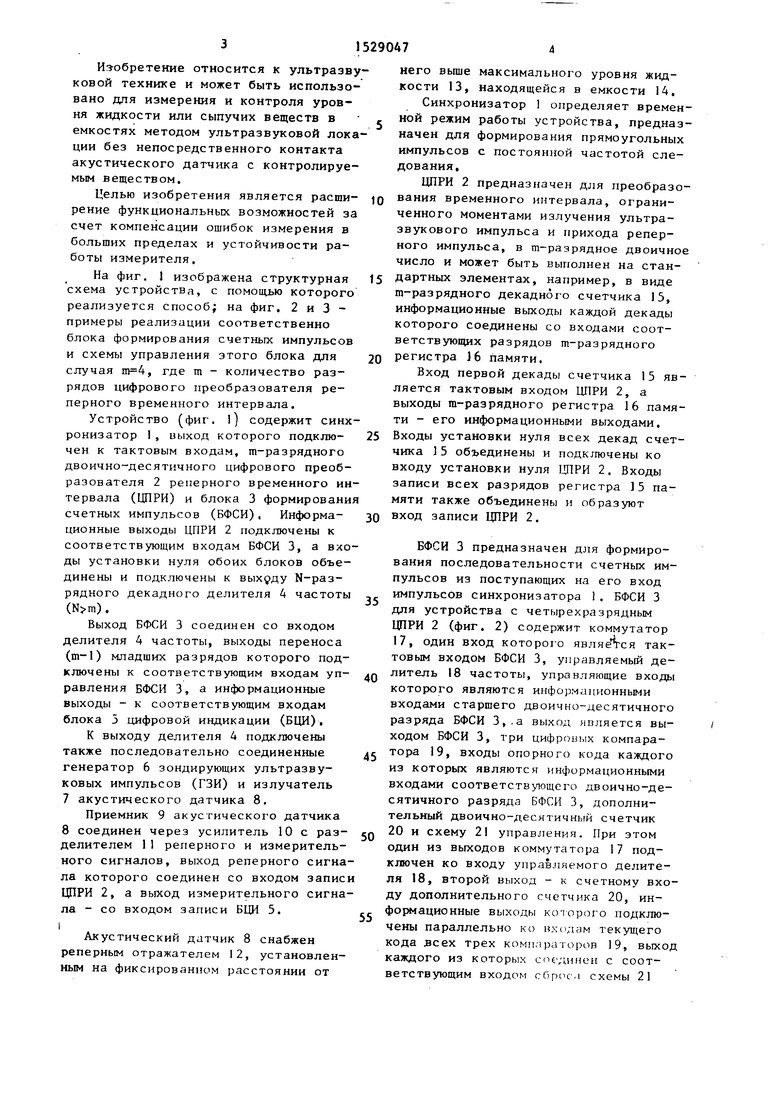

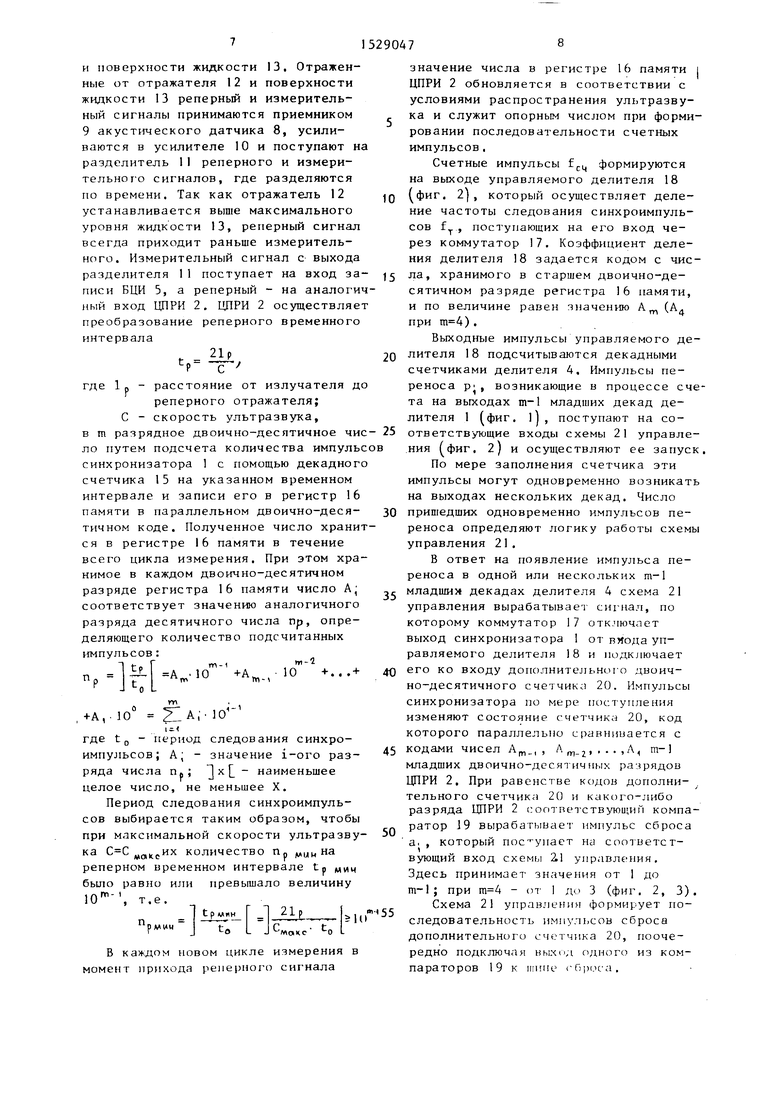

На фиг, изображена структурная схема устройства, с помои ью которого реализуется способ; на фиг, 2 и 3 - примеры реализации соответственно блока формирования счетных импульсов и схемы управления этого блока для случая , где m - количество разрядов цифрового преобразователя ре- перного временного интервала.

Устройство (фиг. 1) содержит синхронизатор 1, выход которого подклю- чен к тактовым входам, т-разрядного двоично-десятичного цифрового преобразователя 2 реперного временного интервала (ЦПРИ) и блока 3 формирования счетных импульсов (БФСИ), Информа- ционные выходы ЦПРИ 2 подключены к соответствующим входам БФСИ 3, а входы установки нуля обоих блоков объединены и подключены к вых9ДУ N-раз- рядного декадного делителя 4 частоты ().

Выход БФСИ 3 соединен со входом делителя 4 частоты, выходы переноса (т-1) младших разрядов которого подключены к соответствующим входам уп- равления БФСИ 3, а информационные выходы - к соответствующим входам блока 5 цифровой индикации (БЦИ),

К выходу делителя 4 подключены также последовательно соединенные генератор 6 зондирующих ультразвуковых импульсов (ГЗИ) и излучатель

7акустического датчика 8,

Приемник 9 акустического датчика

8соединен через усилитель 10 с раз- делителем 11 реперного и измерительного сигналов, выход реперного сигнала которого соединен со входом записи ЦПРИ 2, а выход измерительного сигнала - со входом записи БЦИ 5,

I

Акустический датчик 8 снабжен

реперным отражателем 12, установленным на фиксированном расстоянии от

него выше максимального уровня жидкости 13, находящейся в емкости 14,

Синхронизатор 1 определяет временной режим работы устройства, предназначен для формирования прямоугольных импульсов с постоянной частотой следования,

ЦПРИ 2 предназначен для преобразования временного интервала, ограниченного моментами излучения ультразвукового импульса и прихода реперного импульса, в т-раэрядное двоично число и может быть выполнен на стандартных элементах, например, в виде т-разрядного декадного счетчика 15, информационные выходы каждой декады которого соединены со входами соответствующих разрядов т-разрядного регистра J6 памяти.

Вход первой декады счетчика 15 является тактовым входом ЦПРИ 2, а выходы т-разрядного регистра 16 памяти - его информационными выходами. Входы установки нуля всех декад счетчика 15 объединены и подключены ко входу установки нуля ЦПРИ 2, Входы записи всех разрядов регистра 15 памяти также объединены и образуют вход записи ЦПРИ 2,

БФСИ 3 предназначен для формирования последовательности счетных импульсов из поступающих на его вход импульсов синхронизатора 1, БФСИ 3 для устройства с четырехразрядным ЦПРИ 2 (фиг, 2) содержит коммутатор 17, один вход которого являе ся тактовым входом БФСИ 3, управляемый делитель 18 частоты, управляющие входы которюго являются информационными входами старшего двоично-десятичного разряда БФСИ 3,.а выход является выходом БФСИ 3, три цифро1л 1х компаратора 19, входы опорного кода каждого из которых являются информационньЕМи входами соответствующего двоично-десятичного разряда БФСИ 3, дополнительный двоично-десятичный счетчик 20 и схему 21 управления. При этом один из выходов коммутатора 17 подключен ко входу управляемого делителя 18, второй выход - к счетному входу дополнительного счетчика 20, информационные выходы которого подключены параллельно ко нходам текущего кода всех трех комилраторов 19, выхо каждого из которых соединен с соответствующим входом сбрснм схемы 21

управления, один из выходов которой соединен со входом сброса дополнительного счетчика 20, второй выход - с другим входом коммутатора 17. Управляющие входы схемы 21 управления являются управляющими входами БФСИ 3 а вход установки нуля - входом установки нуля БФСИ 2.

Коммутатор 17 предназначен для коммутации сигнала синхронизатора 1 в соответствии с сигналом управления формируемым схемой 21 управления, либо на вход управляемого делителя 18, либо на счетный вход дополнительного счетчика 20, может быть вьтолнен, например, на стандартных логических элементах цифровой техники.

Управляемый делитель 18 предназначен для деления частоты поступающих на его вход импульсов в соответствии с заданным на его управляющих входах кодом десятичного числа.

Цифровые компараторы 19 предназначены для сравнения поступающих на его входы опорного и текущего кодов чисел и формирования вькодного сигнала в момент их равенства.

Дополнительный счетчик 20 предназначен для формирования текущего кода числа, сравниваемого в компараторах 19, и может быть выполнен на основе стандартного двоично-десятичного счетчика.

Схема управления предназначена для формирования сигнала управления коммутатором 17 и сигнала дополнительного счетчика 20 и представляет собой логический автомат, выполненный на типовых функциональных элементах цифровой техники.

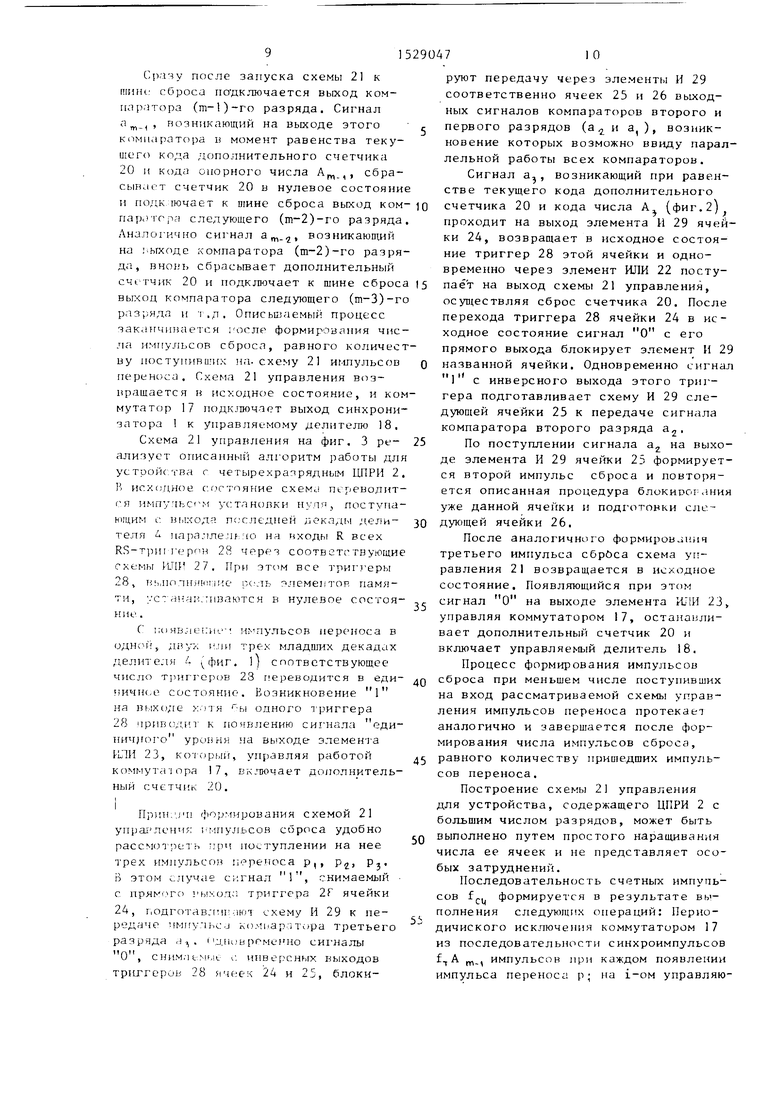

Схема 21 управления (фиг. 3) для рассматриваемого примера содержит два трехвходовых логических элемента ИЛИ 22 и 23, выход одного из которых является вьсходом сброса схемы управления, а выход второго - со вторым выходом, а также три одинаковых ячейки 24-26 управления, каждая из которых включает в себя двухвходо вой логический элемент ИЛИ 27, КЗ- триггер 28 и трехвходовой логический элемент И 29. При этом первый вход элемента И 29 каждой ячейки 24- 26 является соответствующим входом сброса схемы 21 управления, второй вход соединен с соответствующим входом элемента ИЛИ 23 и подключен к прямому выходу RS-триггера 28, а вы0

5

0

5

0

0

5

0

5

ход - к соответствующему входу элемента ИЛИ 22 и одному из входов входового элемента ИЛИ 27. Третий вход элемента И 29 подключен соответственно для ячейки 24 к источнику 1, для ячейки 25 - к инверсному выходу RS-триггера 28 ячейки 24, для ячейки 26 - к инверсному выходу RS- триггера 28 ячейки 25.

Вторые входы элементов ИЛИ 27 всех ячеек 24-26 объединены и являются входом установки нуля схемы 21 управления. Выход элемента ИЛИ 27 -|:аждой ячейки 24-26 соединен со входом RS-триггера 28 соответствующей ячейки.

Входы S RS-триггеров 28 являются соответствующими управляющими входами схемы 21 управления.

ГЗИ 6 предназначен для запоминания кода текущего состояния декадного счетчика делителя 4 в момент прихода измерительного сигнала, преобразования его в код управления цифровым индикатором и отображения результата измерения в цифровом виде и может быть выполнен на типовых элементах цифровой техники.

ГЗИ 6, акустический датчик 8, усилитель 10, разделитель П репер- ного и измерительного-сигналов и реперный отражатель 12 предназначены соответственно для формирования, излучения, приема, усиления и разделения реперного и измерительного сигналов .

Устройство работает следующим об- , разом.

Синхронизатор 1 вырабатывает прямоугольные импульсы с постоянным периодом следования, которые поступают одновременно на тактовые входы т-раз- рядного ЦПРИ 2 и БФСИ 3. Лреобразова- ная в БФСИ 3 последовательность импульсов синхронизатора поступает на делитель 4, выполненный в виде N-разрядного () декадного счетчика. Делитель 4 вырабатывает на выходе старшей декады сигнал, определяющий начало цикла измерения, который устанавливает в исходные состояния ЦПРИ 2, БФСИ 2, БФСИ 3 и запускает ГЗИ 6. Выходной сигнал ГЗИ 6 возбуждает пьезоэлектрический преобразователь 7 и сформированный ультразвуковой импульсный сигнал излучается им в направлении реперного отражателя 12

и поверхности жидкости 13. Отраженные от отражателя 12 и поверхности жидкости 13 реперный и измерительный сигналы принимаются приемником 9 акуст1тческого датчика 8, усиливаются в усилителе 10 и поступают на разделитель 1I реперного и измерительно г о сигналов, где разделяются по времени. Так как отражатель 12 устанавливается выше максимального уровня жидкости 13, реперный сигнал всегда приходит раньше измерительного. Измерительный сигнал с выхода разделителя 11 поступает на вход за- писи БЦИ 5, а реперный - на аналогичный вход ЦПРИ 2, ЦПРИ 2 осуществляет преобразование реперного временного интервала

t, Ц.,

где 1р расстояние от излучателя до

реперного отражателя; С - скорость ультразвука, в m разрядное двоично-десятичное чис ло путем подсчета количества импульс синхронизатора 1 с помощью декадного счетчика 15 на указанном временном интервале и записи его в регистр 16 памяти в параллельном двоично-десятичном коде. Полученное число хранится в регистре 16 памяти в течение всего цикла измерения. При этом хранимое в каждом двоично-десятичном разряде регистра 16 памяти число А; соответствует значению аналогичного разряда десятичного числа пр, определяющего количество подсчитанньрх

импульсов:

т-1 10 +А,

Пр

А,

W-2

10 +...+

о 10

А; 10

1-1

где tn - Период следования синхроимпульсов; А; - значение i-oro разряда числа п.; х - наименьшее целое число, не меньшее X.

Период следования синхроимпульсов выбирается таким образом, чтобы при максимальной скорости ультразвука количество Пр дд|дк на реперном временном интервале tp ич было равно или превышало величину , т.е.

1 tp Г Л.Я.Р , |ь рмии J to L to L

в каждом новом цикле измерения в момент прихода реперного сигнала

5

5

0

5

значение числа в регистре 16 памяти i ЦПРИ 2 обновляется в соответствии с условиями распространения ультразвука и служит опорным числом при формировании последовательности счетных импульсов.

Счетные импульсы f формируются на выходе управляемого делителя 18 фиг. 2), который осуществляет деление частоты следования синхроимпульсов f, поступающих на его вход через коммутатор 17. Коэффициент деления делителя 18 задается кодом с числа, хранимого в старшем двоично-десятичном разряде регистра 16 памяти, и по величине равен значению А (А. при ).

Выходные импульсы управляемого делителя 18 подсчитываются декадными счетчиками делителя 4. Импульсы переноса р , возникающие в процессе счета на выходах т-1 младших декад делителя 1 (фиг. l, поступают на соответствующие входы схемы 21 управления фиг. 2) и осуществляют ее запуск.

По мере заполнения счетчика эти импульсы могут одновременно возникать на выходах нескольких декад. Число пришедших одновременно импульсов переноса определяют логику работы схемы управления 21.

В ответ на появление импульса переноса в одной или нескольких т-1 младшим декадах делителя 4 схема 21 управления вырабатывает сигнал, по которому коммутатор 17 отключает выход синхронизатора 1 от вмода управляемого делителя 18 и подключает его ко входу дополнительного двоично-десятичного счетчика 20. Импульсы синхронизатора по мере поступления изменяют состояние счетчика 20, код которого параллельно сравнивается с

45 кодами чисел А

т-1

А

т-2

50

- 55

младших двоично-десятичных разрядов ЦПРИ 2. При равенстве кодов дополнительного счетчика 20 и KaKoro-jui6o разряда ЦПРИ 2 соответствующий компаратор 19 вырабатывает импульс сброса а. , который пос упает на соответствующий вход cxeMfji 7. управления. Здесь принимает значения от 1 до m-l; при - от 1 до 3 (фнг. 2, 3). Схема 21 управления формирует последовательность импульсов сброса дополнительного счетчика 20, поочередно подключая выход одного из компараторов 19 к типе с Ojx.ifa ,

Срачу после запуска схемы 21 к iiinHt: сброса подключается выход ком- iKip. iTopa (m-l)-ro разряда. Сигнал возникающий на выходе этого компаргттора н момент равенства текущего кода дополнительного счетчика 20 и кода опорного числа А,, сбрасывает счетчик 20 в нулевое состояние

и подк 1ючает к шине сброса выход ком- ю счетчика 20 и кода числа А (фиг.2)

/ /ч X

napJTopf следующего (п1-2)-го разряда, Аналогично сигнал а, возникаюпдай на МХ(щс компаратора (т-2)-го разряда., BHOL b сбрасьгоает дополнительный счетчик 20 и подключает к шине сброса |5 выход компаратора следующего (т-З)-го разряда и т.д. Описьшаемый процесс зак11нчинается 1 осле формирования числа импульсов сброса, равного количеству постуииви. их на. схему 21 и.шульсов Q переноса. Схема 21 управления воэ- пращается в исходное состояние, и коммутатор 17 подк1Ш)чает выход синхронизатора 1 к управляемому делителю 18.

Схема 21 управления на фиг. 3 ре- 25 ализуст описанный алгоритм работы для устройс.тва г четырехразрядным ЦПРИ 2. В исходное с гя-тоякие схем переводится HMoy-ibctv.i установки нуля, поступа- с И 1хода п(;следней |1екад1 | д.ели- теля i параллеЛ{-::(о на нходы R всех КЯ-три1 1 ерг-н 28 через соответствующие схемы }ШИ 27. При этом все триг 1 еры 28, Tis.nnлняи 1:1 :е гл. ль г леме1П Ор, памяти, ус: ана -;: иваются в нулевое состояние .

С i;() явление- и пyльcoв переноса в одн(ч , дпух пли трек младших декадах делителя i . l) соответствующее число триггср)ов 23 переводится в еди- ничн(-е состояние. Возникновение 1 на выхс.1де у. Пя ы одного триггера 28 iipnrscv U T к появлению сиг нала еди- ничдого уровня на выходе элемен-i a ИЛИ 23, который, управляя работой коммута 1ора 17, включает до/голнитель- ный счетчик 20.

30

35

40

45

проходит на выход элемента И 29 ячейки 24, возвращает в исходное состояние триггер 28 этой ячейки и одновременно через элемент ИЛИ 22 поступает на выход схемы 21 управления, осуп1ествляя сброс счетчика 20. После перехода триггера 28 ячейки 24 в исходное состояние сигнал О с его прямого выхода блокирует элемент И 29 названной ячейки. Одновременно сигнал l с инверсного выхода этого триггера подготавливает схему И 29 следующей ячейки 25 к передаче сигнала компаратора второго разряда а,

По поступлении сигнала а на выходе элемента И 29 ячейки 25 формируется второй импульс сброса и повторяется описанная процедура блокирог ния уже данной ячейки и подготовки следующей ячейки 26.

После аналогичного формировлиич третьего импульса сбрйса схема управления 21 возвращается в исходное состояние. Появляющийся при этом сигнал О на выходе элемента ИЛИ 23, управляя коммутатором 17, останавливает дополнительный счетчик 20 и включает управляемый делитель 18.

Процесс формирования импульсов сброса при меньшем числе поступивших на вход рассматриваемой схемы управления импульсов переноса протекает аналогично и завершается после формирования числа импульсов сброса, равного количеству пришедших импульсов переноса.

Построение схемы 21 управления для устройства, содержащего ЦПРИ 2 с большим числом разрядов, может быть выполнено путем простого наращивания числа ее ячеек и не представляет особых затруднений.

np)iH: ,i ii формирования схемой 21 умраг лени ; 1 мпульсов сброса удобно рассмотри - при поступлении на нее трех импульсон переноса р,, р, РЗ- В этом случае с;:гнал 1, снимаемый с прямого ы ;од;; триггера 2Г ячейки

24, подготавлт .;1Ю1 схему И 29 к передаче лмтгульси комиар:5 тора третьего разряда d. I дне вррменно сигналы О, спим,- емме е, инверсных выходов триггеров 28 ячеек 24 и 25, блокируют передачу через элементы И 29 соответственно ячеек 25 и 26 выходных сигналов компараторов второго и первого разрядов (а и а, ), возникновение которых возможно ввиду параллельной работы всех компараторов.

Сигнал а, возникающий при равенстве текущего кода дополнительного

|5 Q5

0

5

0

5

0

проходит на выход элемента И 29 ячейки 24, возвращает в исходное состояние триггер 28 этой ячейки и одновременно через элемент ИЛИ 22 поступает на выход схемы 21 управления, осуп1ествляя сброс счетчика 20. После перехода триггера 28 ячейки 24 в исходное состояние сигнал О с его прямого выхода блокирует элемент И 29 названной ячейки. Одновременно сигнал l с инверсного выхода этого триггера подготавливает схему И 29 следующей ячейки 25 к передаче сигнала компаратора второго разряда а,

По поступлении сигнала а на выходе элемента И 29 ячейки 25 формируется второй импульс сброса и повторяется описанная процедура блокирог ния уже данной ячейки и подготовки следующей ячейки 26.

После аналогичного формировлиич третьего импульса сбрйса схема управления 21 возвращается в исходное состояние. Появляющийся при этом сигнал О на выходе элемента ИЛИ 23, управляя коммутатором 17, останавливает дополнительный счетчик 20 и включает управляемый делитель 18.

Процесс формирования импульсов сброса при меньшем числе поступивших на вход рассматриваемой схемы управления импульсов переноса протекает аналогично и завершается после формирования числа импульсов сброса, равного количеству пришедших импульсов переноса.

Построение схемы 21 управления для устройства, содержащего ЦПРИ 2 с большим числом разрядов, может быть выполнено путем простого наращивания числа ее ячеек и не представляет особых затруднений.

Последовательность счетных импупь- сов f- формируется в результате выполнения следующ 1х операций: Перио- дичиского исключения коммутатором 17 из последовательности синхроимпульсов , импульсов при каждом появлении импульса переноса р; на i-ом управляющем входе схемы 21 управления, где , 2, 3...(т-1); Деления частоты следования оставшихся импульсов синх- ропоследовательности управляемым делителем 18, коэффициент деления которого задается значением числа А старшего разряда ЦПРИ 2.

В результате выполнения этих операций суммарное число исключенных импульсов на временном интервале, равном реперному, составляет п,,, ... ...+А, 1

т- , л10° А:10

Количество счетных импульсов, образующихся на выходе управляемого делителя 18, на этом же временном интервале очевидно будет

п PJ.... А„

Полученное значение счетных импульсов не зависит от скорости распространения ультразвука и при выбранной величине сохраняется неизменным .

Таким образом, в устройстве фиксированному расстоянию fp всегда ставится в соответствие постоянное, крат-ЗО 10

ное 10 количество счетных импульсов, что эквивалентно разбиению этого расстояния на соответствующее число элементарных долей. Подсчет количества сформированных описанным способом счетных импульсов в течение измеряемого временного интервала t 21х/С, где €ji - измеряемое расстояние, дает оценку измеряемого расстояния в соответствующих десятичных до- лях фиксированного расстояния,

Эта операция выполняется с помощью декадного делителя 4, состояние которого в момент прихода измерительного сигнала переносится в память БЦИ 5. После соответствующего преобразования двоично-десятичного кода информация об измеряемой глубине вьшодит- ся в цифровом виде на индикатор БЦИ 5.

Формула изобретения

2904712

реперных импульсов, их приеме, усилении и разделении во времени, о т- лич ающийс я тем, что, с це- лью расширения функциональных возможностей за счет компенсации ошибок в больп их пределах и-повышения ус- тойчивости измерения, период следования синхроимпульсов выбирают из ус- Q ловия равенства или превышения их количества на реперном временном интервале при максимальной скорости ультразвука величины 0 , со5

0

5

ответствующей максимальной скорости ультразвука, в каждом цикле излучения импульсов преобразуют реперный интервал в т-разрядное десятичное число, запоминают десятичное число, соответствующее скорости ультразвука, при текущих физических параметрах среды формируют последовательность счетных импульсов путем уменьшения частоты следования синхроимпульсов в А„ раз и периодического исключения из последовательности синхроимпульсов Am-i чмпульсов с периодом ( Ю+А., )to ; А п,-г импульсов

с периодом и до А(

(А

m

,

10+А

т-г

)tc

О 10

импульсов с периодом ( +А,„., . . .+A,)to, где А„

, - значения соответствующих разрядов полученного десятичного числа, а tg - период следования синхроимпульсов, затем определяют количе- ство счетных импульсов в рабочем интервале, отображающее измеряемое расстояние в десятичных долях фиксированного расстояния.

2, Устройство компенсации погрешностей акустических локационных уровнемеров, содержащее синхронизатор, последовательно соединенные делитель частоты, генератор зондирующих импульсов, акустический датчик, состоящий из излучателя и приемника, соединенного через усилитель с разделителем реперного и измерительйого сигналов, а также установленный на фиксированном расстоянии от акустического датчика реперный отражатель, отличающееся тем, что, с целью расширения функциональных возможностей за счет компенсации ошибок в больших пределах и повышения устойчивости работы измерителя, в него введены т-разрядный двоично- десятичный цифровой преобразователь реперного временного интервала, блок

формирования счетньпс импульсов и бл цифровой индикации, причем делитель выполнеи в виде N-разрядного декадного счетчика, а синхронизатор выполнен неуправляемым, при этом тактовый вход т-разрядного двоично-десятичного цифрового преобразователя реперного временного интервала соединен с тактовым входом блока формирования счетных импульсов и подключен к выходу синхронизатора, его вход установки нуля соединен с аналогичным входом блока формирования счетных импульсов и подключен к выходу делителя частоты, вход записи

Г

1г .1:з:т:л

подключен к первому выходу разделителя реперного и измерительного сигналов, а информационные выходы соединены с соответствующими входами блока формирования счетных импульсов, входы управления которого подключены к соответствующим выходам переноса младших разрядов делителя частоты, а выход - к счетному входу делителя частоты, информационные вых оды N де кад которого соединены с соответствующими входами блока цифровой индикации, вход записи которого подключен-, ко второму выходу разделителя реперного и измерительного сигналов.

cvr«

Авторы

Даты

1989-12-15—Публикация

1985-07-12—Подача