(54) СТЕРЕОДЕКОДЕР

| название | год | авторы | номер документа |

|---|---|---|---|

| Стереодекодер | 1990 |

|

SU1838883A3 |

| Стереодекодер | 1983 |

|

SU1223384A1 |

| Стереодекодер сигналов с полярной модуляцией | 1983 |

|

SU1172038A1 |

| Блок перемножителей функций | 1987 |

|

SU1506563A1 |

| Стереодекодер | 1986 |

|

SU1356245A1 |

| СПОСОБ ПЕРЕДАЧИ ДОПОЛНИТЕЛЬНОЙ ИНФОРМАЦИИ В СИСТЕМЕ УКВ-ВЕЩАНИЯ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1992 |

|

RU2030835C1 |

| Стереодекодер | 1984 |

|

SU1166327A1 |

| Устройство фазовой автоподстройки частоты | 1984 |

|

SU1352645A1 |

| Стереодекодер | 1985 |

|

SU1241503A1 |

| Устройство для измерения амплитудно-частотных и фазочастотных характеристик четырехполюсников с преобразованием частоты | 1988 |

|

SU1599811A1 |

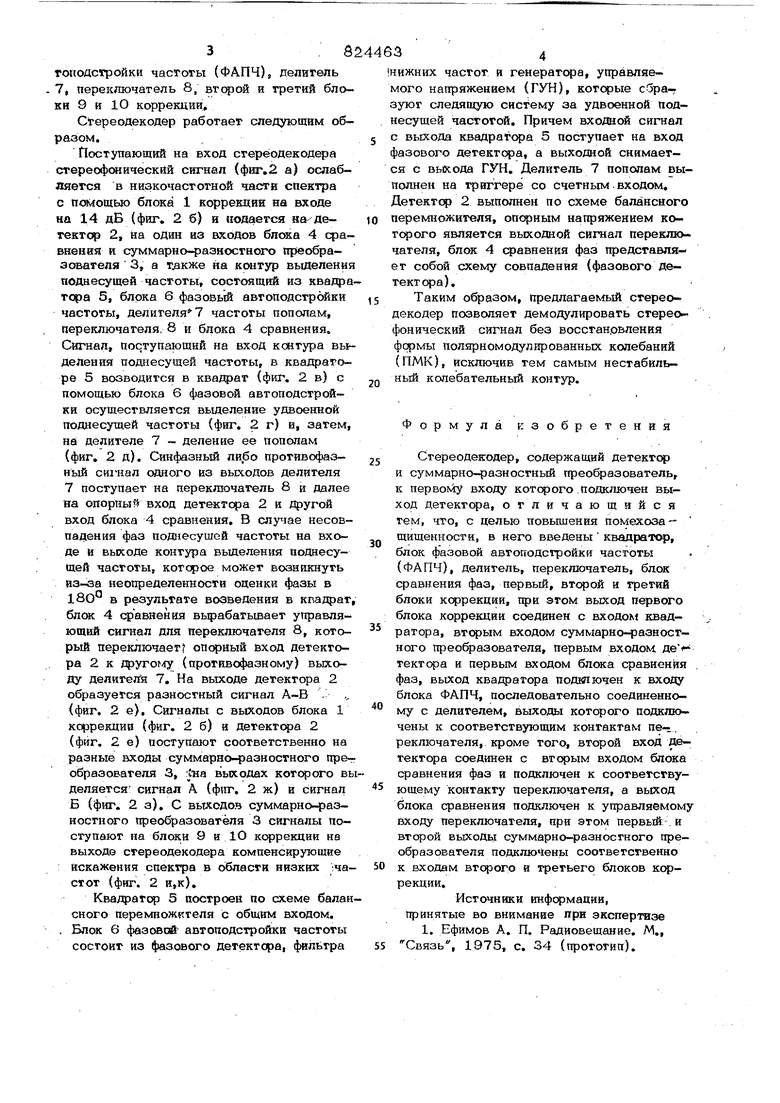

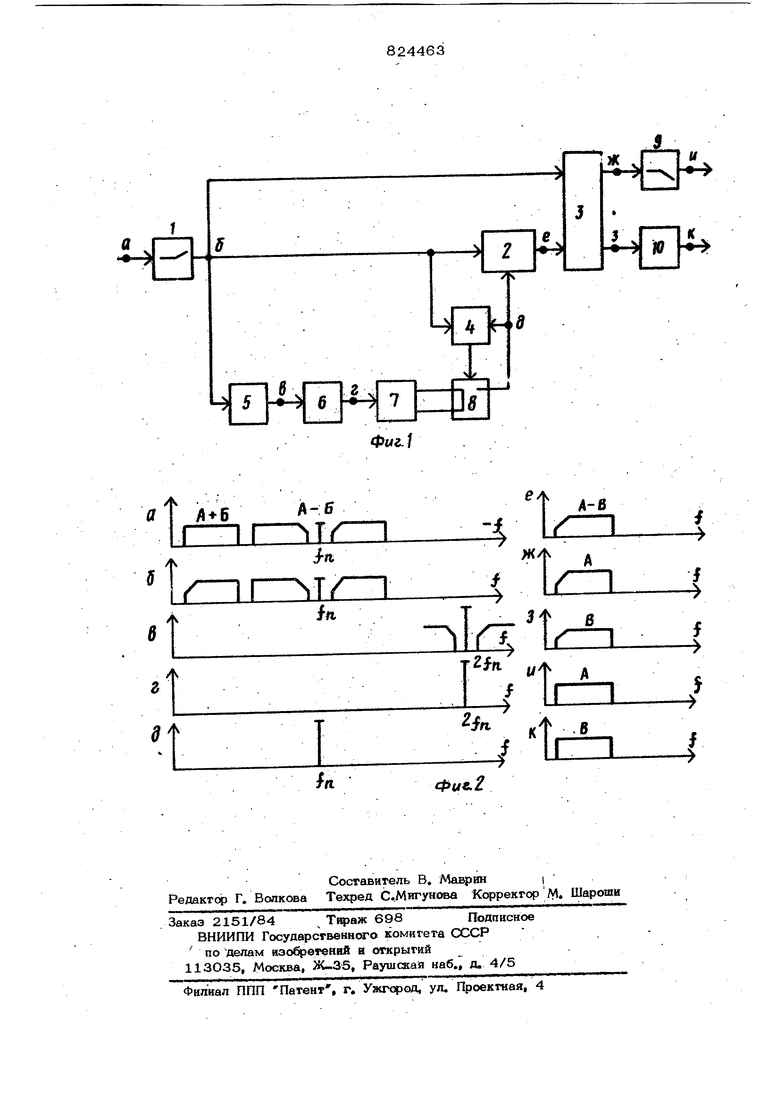

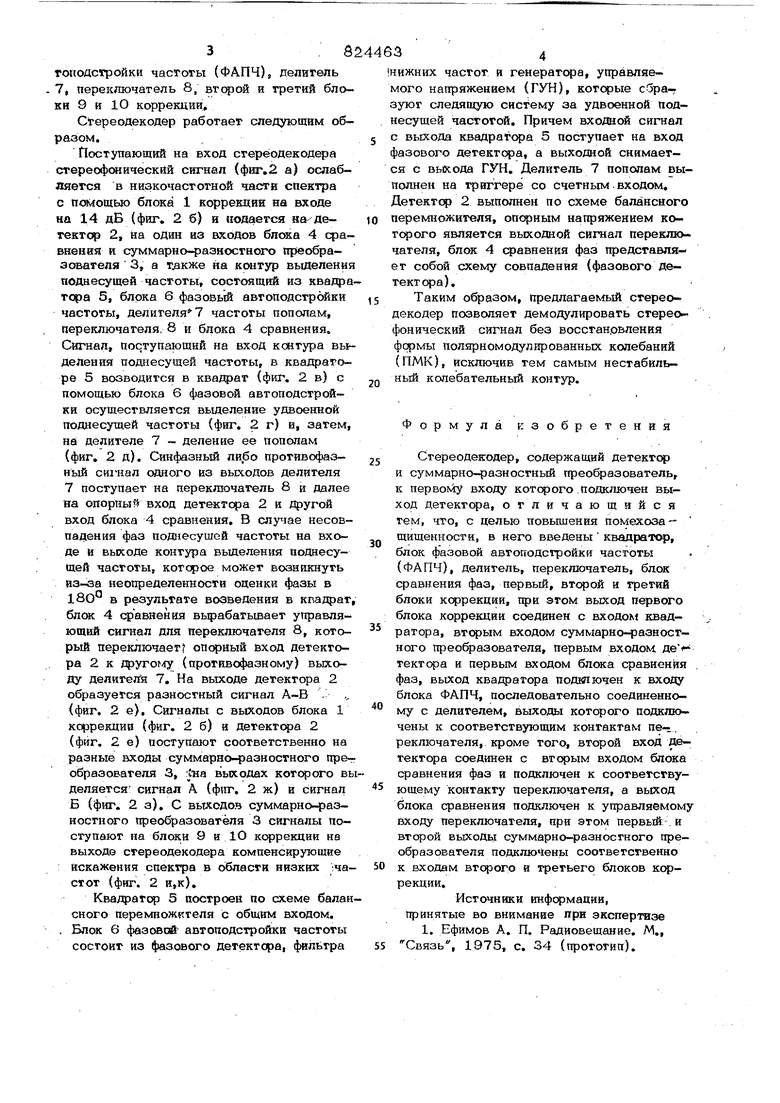

Изобретение огносится к радиотехнике и может использоваться в радиовещательных устройствах при приеме стереофониче ского вешания. Известен стереодекодер, содержащий детектор и суммарно-разностньй преобразователь, к первому входу которого поДключев выход детектора fj. ОшаКо взвестный сгереодекодер имеет недостаточную помехозащищенность. Цепь изобретения - повышение помехозащищенности. Поставленная цель достигается тем, , что стереодекодер, содержащий детектор и суммарно разностный преофазователь, к первому входу которот-о подключен выхо детектора введены квадратсф, блок фЕ13(ю автоподстройки частоты (ФАПЧ), делител переключатель, бпсж сравнения фаз, первый, второй и третий блоки коррекции, при этом выход первого блока коррекдив соединен с входом квадратс| а, вторым входом суммарно-разностнсмпо преофазователя, первым входом детектора, вторым ВХОДОМ суммарно разностного преобразователя, первым входом детектора и первым входом блока сравнения фаз, .выход квасратора подключен к входу блсжа ФАПЧ, последовательно соединенному с делителем,, выходы которого подключены к соответствующим контактам переключателя, кроме того, вторсй вход детектора соединен с вторым входом блсжа сравнения фаз и поДЕл:ючен к соответствующему контакту переключателя, а выход блока сравнения подключен к .управляемому вхсяу переключателя, при этом первый и второй выходы суммарно-разностного сфеобразователя подключены соответственно к входам второго Е третьего блоксе коррекцив. На фиг, 1 приведена структурная электрическая схема предлагаемого устройства; на фиг. 2 - спектры свгяалвв в различных точках схемы Устройство содержит первый бпок 1 ксфрекцив, детектор 2, суммарво-ра; остный преобразователь 3, блок 4 сравне- нвя фаз, квадратор 5, блок 6 фазовой ав3, S гоподстройки частоты (ФАПЧ), делитель . 7, переключатель 8, второй и третий блоки 9 и 10 коррекции, Стереодекодер работает следующим образом, Поступающий на вход стерёодекодера стереофонический сигнал (фиг.2 а) ослабляется в низкочастотной части спектра с помощью блока 1 коррекция на входе на 14 дБ {фиг. 26) и подается на детектор 2, на один из входов блока 4 сравнения и суммарно-разностного преобразователя 3, а йа KtMiTyp вьшеления поднесущей частоты, состоящий из квадра тсэра 5, блока 6 фазовьй автоподстрс ки частоты, делителя7 частоты пополам, переключателя, 8 и блока 4 сравнения. Сигнал, поступающий на вход контура вы деления поднесущей частоты, в квадраторе 5 возводится в квадрат (фиг, 2 в) с помощью блока 6 фазовой автоподстрой кй осуществляется выделение удвоенной поднесущей частоты (фиг, 2 г) и, затем, на делителе 7 - деление ее пополам (фиг. 2 д). Синфазный ли.бо противофазный си1-нал огшого из вььчодов делителя 7 поступает на переключатель 8 и далее на опорный вход детектс а 2 и Другой вход блока 4 сравнения, В случае несовпадения фаз подиесушей частоты на входе и выходе контура выделения аоднесущей частоты, которое может возникнуть из-за неопределенности оценки фазы в 18О в результате возведения в квадрат блсяс 4 сравнения вьфабатывает управляющий сигнал для переключателя 8, который переключает опорный вход детектора 2 к друго 1у (противофазному) выходу делители 7, На выходе детектора 2 образуется разностный сигнал А-В . ,, (фиг, 2 е). Сигналы с выходов блока 1 коррекции (фиг, 2 б) и детектс а 2 (фиг. 2 е) поступают соответственно на разные входы суммарно-разностного преобразователя 3, Сна выходах которого вы деляется сигнал А (фиг, 2 ж) и сигнал Б (фиг. 2 з), С выходов суммарнонразностного преобразователя 3 сигналы поступают на блоки 9 и 10 коррекции на выходе стерёодекодера компенсирующие искажения спектра в области низких :частот (фиг. 2 и,к). Квадратор 5 построен по схеме балан сного пере множителя с общим входом, . Блок 6 фазовой автоподстройки частоты состоит из фазового детектора, фильтра 3 ижних частот и генератора, управляеого напряжением (ГУН), которые сбра-уют следящую систему за удвоенной подесущей частотой. Причем входной сигнал выхода квадратора 5 поступает на вход азового детектора, а выходной снимаетя с вьссода ГУН, Делитель 7 пополам выолнен на фиггере со счетным входом. етектор 2 выполнен по схеме балансного еремножнтеля, опорным напряжением коорого является выходной сигнал переклюателя, блок 4 сравнения фаз представлят собой схему совпадения (фазового детектора). Таким образом, предлагаемый стереоекодер позволяет демодулировать стереофонический сигнал без восстановления фермы полярномодулированных колебаний (ПМК), исключив тем самым нестабильный колебательный контур. Формула изобретения Стереодекодер, содержащий аетектар и суммарно-разностньй преобразователь, к первому входу которого подключен выход детектора, отличающийся тем, что, с целью повышения помехозащищенносги, в него введены квадратор, блок фазовой автоподстройки частоты (ФАПЧ), делитель, переключатель, блок сравнения фаз, первый, второй и третий блоки коррекции, при этом выход первого блока коррекции соединен с входом квадратора, вторым входом суммарно-разностного преобразователя, первым входом де тектора и первым входом блока сравнения фаз, выход кващ)атора подяхючен к входу блока ФАПЧ, последовательно соединенному с делителем, выхода11 которого подключены к соответствующим контактам пе-. реключателя, кроме того, второй вход Детектора соединен с вторым входом блока сравнения фаз и подключен к соответствующему контакту переключателя, а выход блока сравнения подключен к управляемому входу переключателя, при этом первый: . и второй выходы суммарно-разностного преобразователя подключены соответственно к входам второго и третьего блоков коррекции, Источники информации, принятые во внимание яри экспертизе 1. Ефимов А, П. Радиовещание. М., Связь, 1975, с, 34 (прототип).

/а

Фмг./

Фиг. 2

Авторы

Даты

1981-04-23—Публикация

1979-07-24—Подача