i

Изобретение относится к вычислительной технике и может быть использовано при организации внутреннего обмена в многопроцессорньтх вычислительных системах.

Известно многоканальное устройство приоритета, содержащее в каждом канале триггер заявок, узел анализа приоритета и выходной триггер. Триггеры заявок каналов с помощью входных вентилей соединяются с выходными триггерами. Выходные триггеры с помседью элементов ИЛИ, образующих блок анализа приоритета, объединены в последовательную цепь.

Устройство работает синхронно В каждом такте происходит прием заявок на триггеры заявок,, в следукядем такте подача их на выходные триггеры, с выходов которых заявки попадают на блок анализа приоритетов, где происходит анализ заявок, а затем сброс менее приоритетных заявок. С выхода выходного триггера, на который записана заявка с высшим приоритетом, заявка попадает на выходной вентиль, с выхода которого по сигналу опроса заявка с высшим приоритетом попадает на соответст;вующую выходную шину устройства j.

Недостатком такого устройства является низкая пропускная способность

Наиболее близким по технической сущности и достигаемому результату к предлагаемому является многоканальное устройство приоритета, содержащее в каждом канале триггер заявок, узел анализа приоритетов, выходной триггер,.причем процесс выбора и обслуживания заявки осуществляется так ж, как и в описанном устройстве {2j.

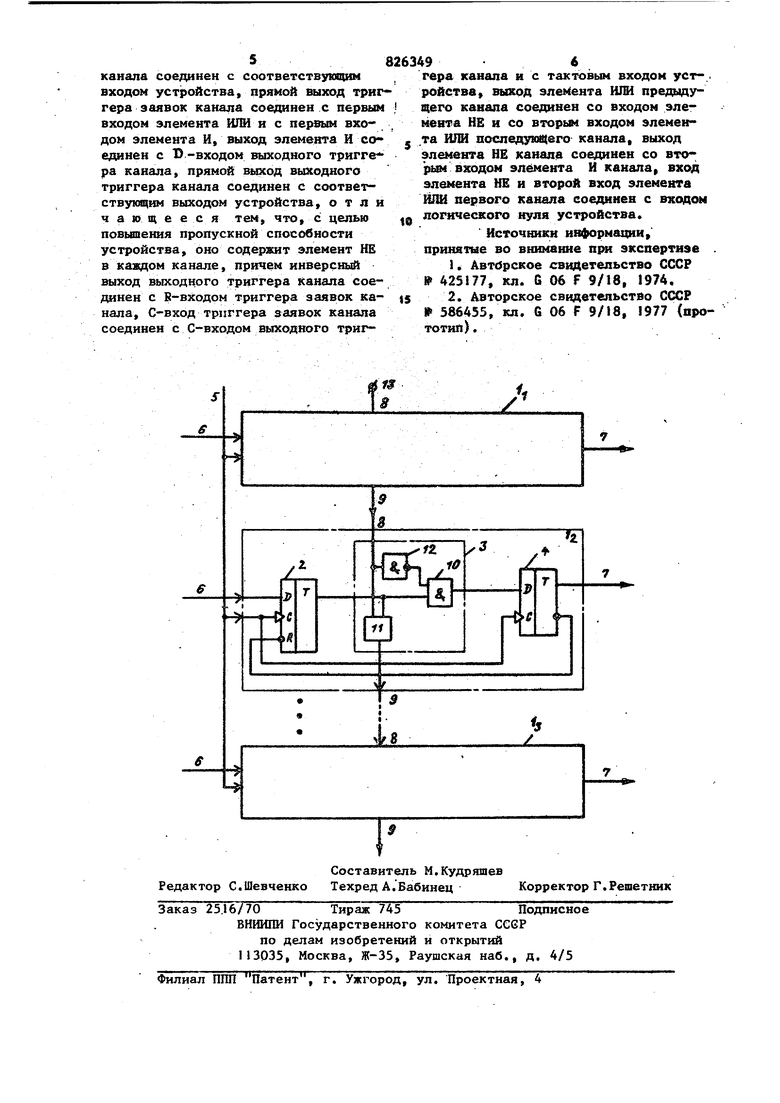

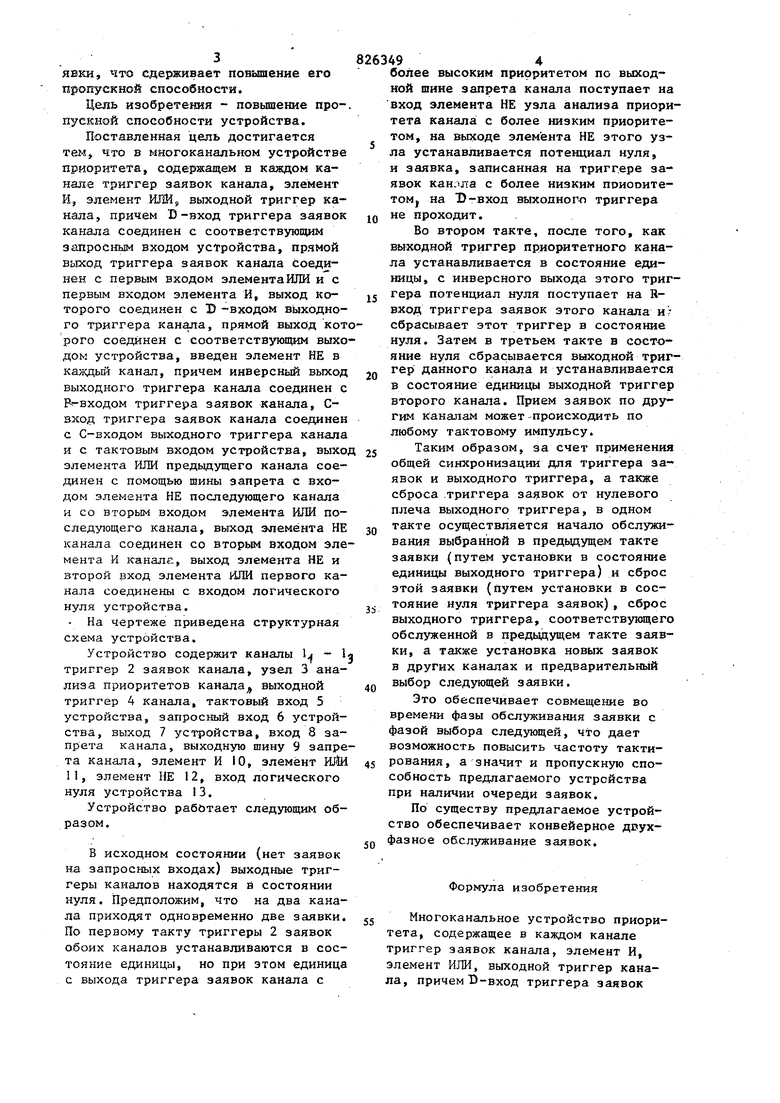

Однако, в этом устройстве анализ приоритет происходит быстрее за счет распараллеливания путей сброса низкоприоритетных заявок с помощью многовходовых элементов ИЛИ, но устройство не обеспечивает совмещения фазы выбора и фазы обслуживания заявки, что сдерживает повышение его пропускной способности. Цель изобретения - повышение пропускной способности устройства. Поставленная цель достигается тем, что в многоканальном устройстве приоритета, содержащем в калздом канале триггер заявок канала, элемент И, элемент ИЛИ, выходной триггер канала, причем D-вход триггера заявок канала соединен с соответствующим запросным входом устройства, прямой вьрсод триггера заявок канала Соединен с первым входом элемента ИЛИ и с первым входом элемента И, выход которого соединен с D -входом выходного триггера канала, прямой выход кот рого соединен с соответствующим выхо дом устройства, введен элемент НЕ в каждый канал, причем инверсный выход выходного триггера канала соединен с Р.-ВХОДОМ триггера заявок канала, Свход триггера заявок канала соединен с С-входом выходного триггера канала и с тактовым входом устройства, выхо элемента ИЛИ предыдущего канала соединен с помощью шины запрета с входом элемента НЕ последующего канала и со вторым входом элемента ИЛИ последующего канала, выход элемента НЕ канала соединен со вторым входом эле мента И канала, выход элемента НЕ и второй 13ХОД элемента ШШ первого канала соединены с входом логического нуля устройства. На чертеже приведена структурная схема устройства. Устройство содержит каналы триггер 2 заявок канала, узел 3 анализа приоритетов каналаJJ выходной триггер 4 канала, тактовый вход 5 устройства, запросный вход 6 устройства, выход 7 устройства, вход 8 запрета канала, выходную шину 9 запре та канала, элемент И 10, элемент НИИ 11, элемент НЕ 12, вход логического нуля устройства 13. Устройство работает следующим образом. В исходном состоянии (нет заявок на запросных входах) выходные триггеры каналов находятся в состоянии нуля. Предположим, что на два канала приходят одновременно две заявки. По первому такту триггеры 2 заявок обоих каналов устанавливаются в состояние единицы, но при этом единица с выхода триггера заявок канала с 494 более высоким приоритетом по выходной шине запрета канала поступает на вход элемента НЕ узла анализа приоритета канала с более низким приоритетом, на выходе элемента НЕ этого узла устанавливается потенциал нуля, и заявка, записанная на триггере заявок канала с более низким поиооитеTOMj на D-вход выходного триггера не проходит. Во втором такте, после того, как вы хрдной триггер приоритетного канала устанавливается в состояние едиШ1цы, с инверсного выхода этого триггера потенциал нуля поступает на Ввход триггера заявок этого канала иг сбрасывает этот триггер в состояние нуля. Затем в третьем такте в состояние нуля сбрасывается выходной триггер: данного канала и устанавливается в состояние единища выходной триггер второго канала. Прием заявок по другим каналам может-происходить по любому тактовому импульсу. Таким образом, за счет применения общей синхронизации для триггера заявок и выходного триггера, а также сброса триггера заявок от нулевого плеча выходного триггера, в одном такте осуществляется начало обслуживания выбранной в предыдущем такте заявки (путем установки в состояние единицы выходного триггера) и сброс этой заявки (путем установки в состояние нуля триггера заявок), сброс выходного триггера, соответствующего обслуженной в предыдущем такте заявки, а также установка новых заявок в других каналах и предварительньШ выбор следукицей заявки. Это обеспечивает совмещение во времени фазы обслуживания заявки с фазой выбора следующей, что дает возможность повысить частоту тактирования, а значит и пропускную способность предлагаемого устройства при наличии очереди заявок. По существу предлагаемое устройство обеспечивает конвейерное доухфазное обслуживание заявок. Формула изобретения Многоканальное устройство приоритета, содержащее в каждом канале триггер заявок канала, элемент И, элемент ИЛИ, выходной триггер канаа, причем В-вход триггера заявок

входом устройства, прямой выход триг гера заявок канала соединен с первым входом элемента ИШ и с первым входом элемента И, выход элемента И соединен с 15.-входом выходного тригге ра канала, прямой выход выходного триггера канала соединен с соответствукщим выходом устройства, о т л и чающееся тем, что, с целью повышения пропускной способности устройства, оно содержит элемент НЕ в каждом канале, причем инверсный клход выходного триггера канала соединен с В-входом триггера заявок канала, С-вход триггера заявок канала соединен с С-входом выходного тригройства, выход элемента ИШ предыдуotero канала соединен со входом элемента НЕ и со вторым входом элемента ШЩ последующего канала, выход элемента НЕ канал В соеда|нен со вторШ4 входом элемента И канала, вход элемента НЕ и второй вход элемента ШШ первого канала соеда{нен с входом логического нуля устройства.

Источники информации, принятые во внимание atm экспертизе

. Авторское свидетельство СССР 425177, кл. G 06 F 9/18, 1974.

2. Авторское свидетельство СССР 586455, кл. G 06 F 9/18, 1977 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство приоритета | 1980 |

|

SU964638A1 |

| Многоканальное устройство приоритета | 1983 |

|

SU1148030A1 |

| Многоканальное устройство дляпОдКлючЕНия иСТОчНиКОВ иНфОРМАцииК ОбщЕй МАгиСТРАли | 1979 |

|

SU849212A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 1992 |

|

RU2108618C1 |

| Многоканальное устройство для подклю-чЕНия иСТОчНиКОВ иНфОРМАции K ОбщЕйМАгиСТРАли | 1979 |

|

SU807298A1 |

| Многоканальное устройство приори-TETA | 1979 |

|

SU840909A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2015 |

|

RU2589317C1 |

| Многоканальное устройство для подключения источников информации к общей магистрали | 1981 |

|

SU1029759A1 |

| Устройство для прерывания резервированной вычислительной системы | 1991 |

|

SU1824636A1 |

| Многоканальное устройство приоритета | 1989 |

|

SU1661765A1 |

Авторы

Даты

1981-04-30—Публикация

1979-09-07—Подача