Изобретение относится к области вычислительной техники и может быть использовано для арбитража в системах обработки информации при организации передачи данных от абонентов к устройству общего пользования.

Известно многоканальное устройство приоритета (RU №2415465 С2, МПК G06F 9/46, заявлен 01.06.2009, опубликован 27.03.2011, Бюл. №9), содержащее М каналов, каждый из которых содержит дешифратор, группу элементов И, первый и второй элементы ИЛИ, а К-й канал (К=1, …, М-1) дополнительно содержит элемент И с прямым и инверсными входами, при этом в каждый канал введен элемент задержки, причем в каждом канале вход запроса соединен со входом элемента задержки, выход которого соединен со вторыми входами всех элементов И группы элементов И своего канала.

В данном устройстве введена дисциплина обслуживания запросов абонентов с абсолютными приоритетами. Если при обслуживании текущего запроса поступает более приоритетный запрос, то обслуживание текущего запроса прерывается, разрешается доступ к устройству общего пользования абоненту с самым приоритетным запросом и после его обслуживания продолжается обслуживание менее приоритетных абонентов.

Недостатком данного устройства является увеличение объема аппаратуры в каждом канале, при подключении новых абонентов, прямо пропорционально количеству каналов М - в каждом канале увеличивается до М количество выходов дешифраторов, количество входов у первого и второго элементов ИЛИ, у элемента И с прямым и инверсными входами, а также количество элементов И в каждой группе.

Известно многоканальное устройство для приоритетного обслуживания запросов (RU №2322689 С2, МПК G06F 9/50, заявлен 05.06.2006, опубликован 20.04.2008, Бюл. №11), содержащее генератор импульсов, два элемента И, два счетчика, схему сравнения, регистр, элемент НЕ, три элемента ИЛИ, элемент ИЛИ-НЕ, сумматор по модулю два, элемент задержки, дешифратор, формирователь импульсов и М каналов, каждый из которых содержит элемент И, элемент ИЛИ, элемент И с прямыми и инверсными входами. В данном устройстве реализована циклическая дисциплина обслуживания запросов и совмещение во времени этапа обслуживания запроса и этапа поиска следующего запроса на обслуживание.

Недостатками данного устройства является большой объем оборудования, обусловленный ростом количества входов прямо пропорционально количеству каналов М у двух элементов ИЛИ, элемента ИЛИ-НЕ, а также в каждом канале у элементов И с прямыми и инверсными входами, и низкое быстродействие, связанное с большим периодом следования импульсов генератора.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является, принятое за прототип, многоканальное устройство для подключения абонентов к общей магистрали (RU №2444780 С1, МПК G06F 13/37, заявлено 04.02.2011, опубликован 10.03.2012, Бюл. №7), содержащее узел анализа приоритета, элемент НЕ устройства, тактовый вход, n запросных входов, n информационных выходов и n каналов, при этом каждый канал содержит элемент И, два элемента ИЛИ, элемент ИЛИ-НЕ, триггер, счетчик и два узла анализа приоритета, причем каждый узел анализа приоритета содержит элемент И, элемент ИЛИ, элемент НЕ, элемент ИЛИ-НЕ, информационный выход канала и запросный вход канала, который соединен с первым входом первого элемента И.

Недостатком данного устройства является большой объем оборудования и низкое быстродействие, что связано с последовательным прохождением сигнала опроса от канала с высшим приоритетом к каналам с более низким приоритетом.

К причинам, препятствующим достижению указанного ниже технического результата, относится отсутствие средств, обеспечивающих одновременную параллельную обработку запросов, так как поиск очередного запроса начинается только после окончания времени для отработки текущего запроса.

Техническим результатом изобретения является уменьшение аппаратных затрат, повышение надежности и быстродействия устройства, расширение функциональных возможностей в части совмещения обслуживания запроса и поиска следующих запросов.

Указанный технический результат при осуществлении изобретения достигается тем, что в многоканальное устройство приоритета, содержащее

N каналов 11, 12, …, 1N, N запросных входов 141, 142, 14N, N выходов ответа канала 161, 162, …, 16N, тактовый вход 21, при этом каждый канал 11, 12, …, 1N содержит элемент ИЛИ 8 и узел анализа приоритета 2, причем каждый узел анализа приоритета 2 содержит первый элемент И 7, элемент ИЛИ 6, первый элемент НЕ 3, информационный выход канала 16 и запросный вход канала 14, который соединен с первым входом первого элемента И 7,

дополнительно введены элемент И 11 устройства, синхронный RS-триггер 12, m разрядный буферный регистр 13, k разрядный информационный выход 17, выход запроса обмена устройства 18, вход окончания обмена 19, вход разрешения работы 20, вход начальной установки 22,

кроме того, в каждом канале 11, 12, …, 1N введены двухвходовые мультиплексоры по m разрядов 9, (m+1) разрядный регистр 10, соответствующие m разрядные информационные входы каналов 151, 152, …, 15N, вход запроса от следующего канала 23, вход разрешения от следующего канала 24, вход передачи запроса от предыдущего канала 25, m разрядный информационный вход от предыдущего канала 26, выход разрешения канала 27, выход передачи запроса канала 28,

а в каждый узел анализа приоритета 2 дополнительно введены второй элемент НЕ 4, второй элемент И 5,

причем вход сброса устройства 22 соединен с соответствующими входами регистров 10, триггера 12 и буферного регистра 13, тактовый вход 21 соединен с входами синхронизации первыми входами регистров 10, триггера 12 и буферного регистра 13,

в каждом канале 11, 12, …, 1N вход запроса канала 14 соединен со вторым входом элемента ИЛИ 8 и адресным входом двухвходовых мультиплексоров 9, m разрядные информационные входы каналов 15 соединены со второй группой входов соответствующих двухвходовых мультиплексоров 9, первые группы входов которых являются m разрядными информационными входами от предыдущего канала 26, а выходы двухвходовых мультиплексоров 9 соединены с первой группой m разрядных информационных входов соответствующих регистров 10, (m+1)-й информационный вход регистра 10 соединен с выходом элемента ИЛИ 8 канала, первый вход которого является входом передачи запроса от предыдущего канала 25,

в каждом узле анализа приоритета 2 вход первого элемента НЕ 3 является входом запроса от следующего канала 23, а выход первого элемента НЕ 3 соединен с первым входом второго элемента И 5, второй вход которого является входом разрешения от следующего канала 24, а выход второго элемента И 5 соединен со вторым входом элемента ИЛИ 6, первый вход которого соединен с выходом второго элемента НЕ 4, вход которого соединен с (m+1)-м информационным выходом регистра 10, который является выходом передачи запроса канала 28, выход элемента ИЛИ 6 соединен со вторым входом первого элемента И 7, с входом загрузки регистра канала 10 и является выходом разрешения канала 27, выход первого элемента И 7 является выходом ответа 16 соответствующего канала 1,

в первом канале 11 вход передачи запроса от предыдущего канала 25 и m разрядный информационный вход от предыдущего канала 26 соединены с логическим нулем,

в каждом канале 12, …, 1N, кроме первого канала 11, вход передачи запроса от предыдущего канала 25 соединен с выходом передачи запроса канала 28, соответствующего предыдущего канала 11, 12, …, 1N-1, a m разрядный информационный вход от предыдущего канала 26 соединен с m разрядным информационным выходом регистра 10, соответствующего предыдущего канала 11, 12, …, 1N-1,

в каждом канале 11, 12, …, 1N-1, кроме последнего канала 1N, вход запроса от следующего канала 23 соединен с входом запроса 14, соответствующего последующего канала 12, …, 1N, а вход разрешения от следующего канала 24 соединен с выходом разрешения канала 27, соответствующего последующего канала 12, …, 1N, вход запроса от следующего канала 23 последнего канала 1N соединен с логическим нулем,

выход передачи запроса канала 28 последнего канала 1N соединен с первым входом элемента И 11 устройства, выход которого соединен с S-входом синхронной установки в единицу триггера 12, R-вход синхронной установки в нулевое состояние триггера 12 соединен с внешним входом окончания обмена 19, инверсный выход триггера 12 соединен с входом разрешения от следующего канала 24 последнего канала 1N, вторым входом элемента И 11 устройства и входом загрузки буферного регистра 13, вход разрешения работы которого соединен с внешним входом разрешения работы 20, группа из m информационных входов буферного регистра 13 соединена с m разрядным информационным выходом регистра 10 последнего канала 1N,

k разрядный информационный выход буферного регистра 13 является k разрядным информационным выходом 17 устройства, прямой выход триггера 12 является выходом запроса обмена устройства 18.

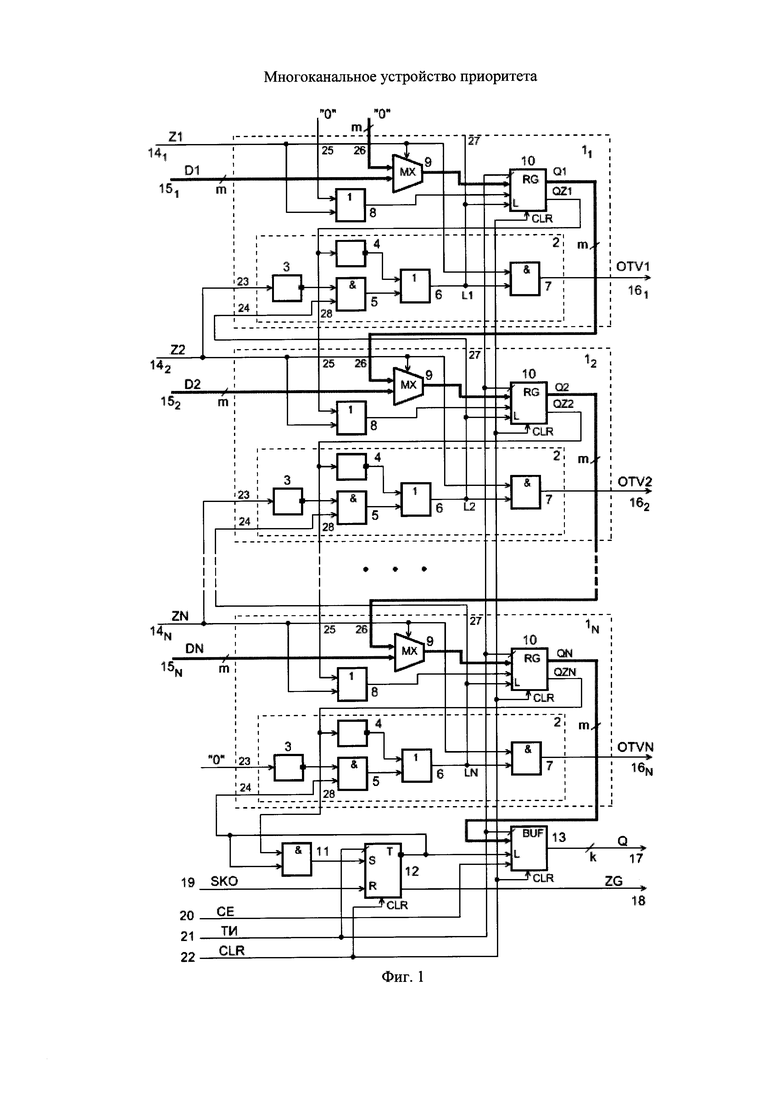

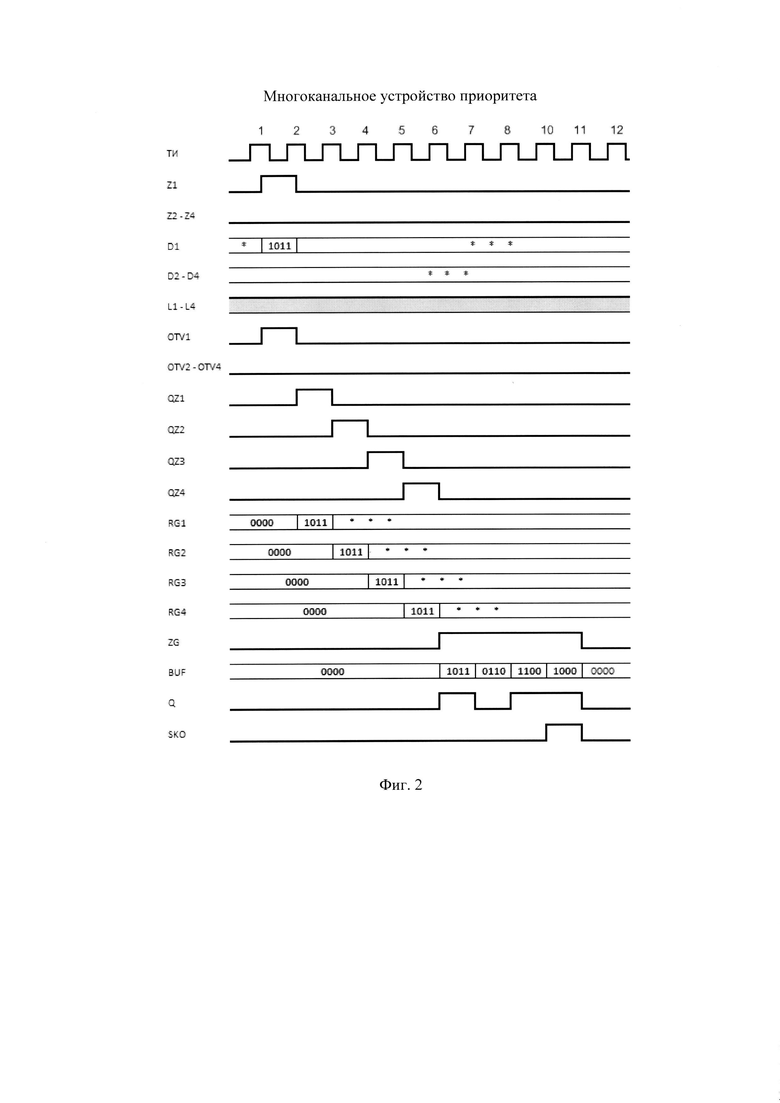

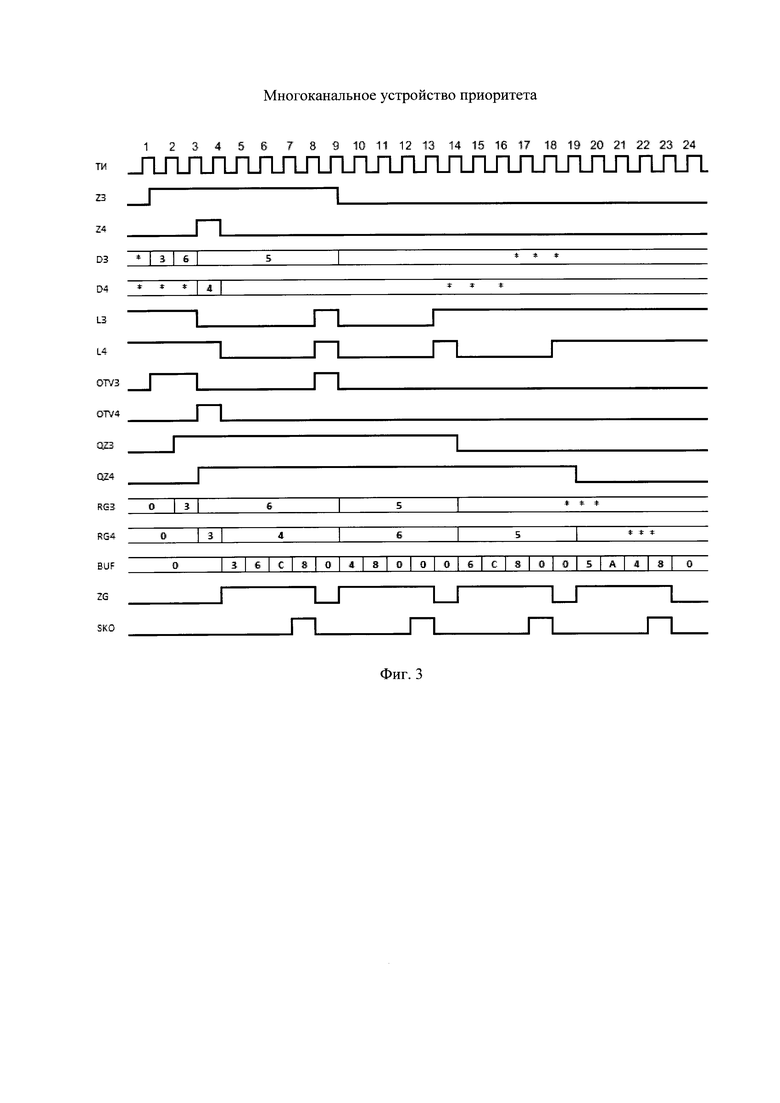

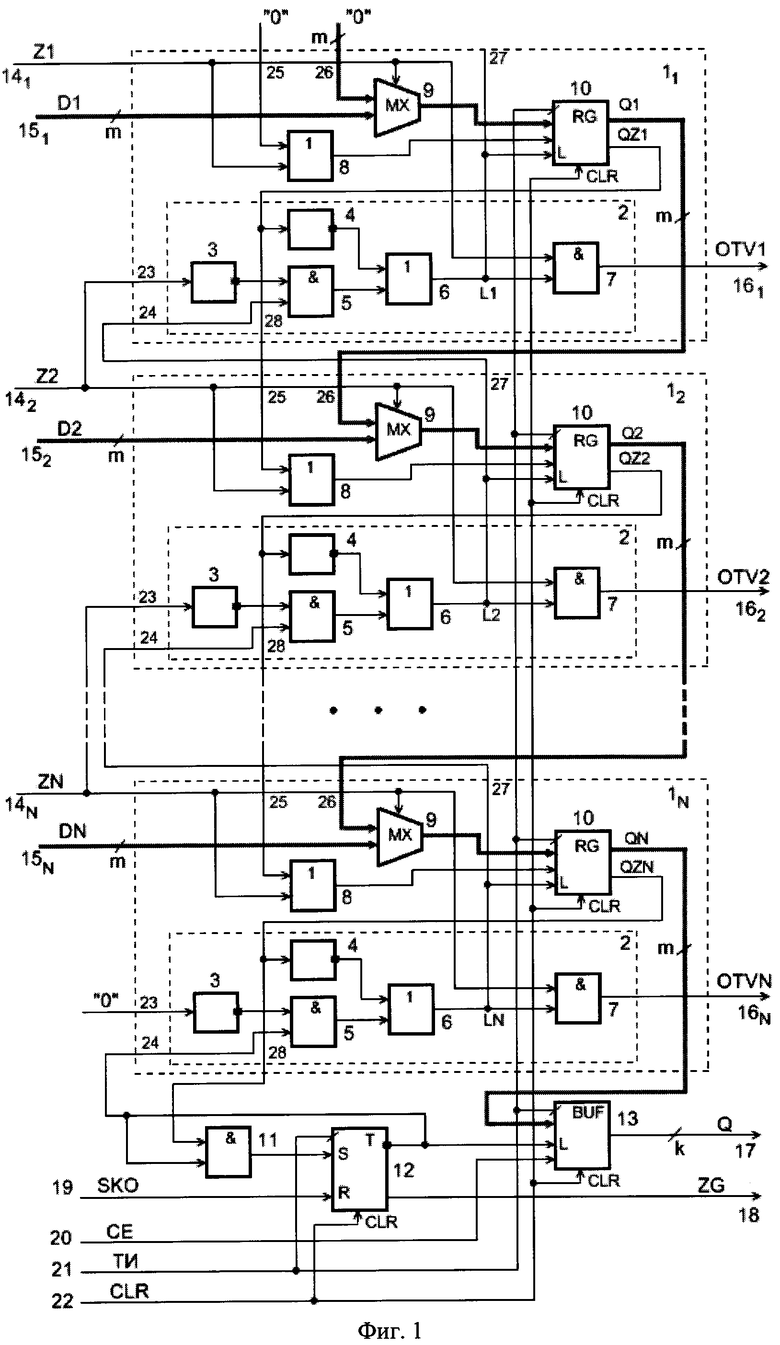

На фиг. 1 представлена схема предлагаемого многоканального устройства приоритета. На фиг. 2 приведена временная диаграмма работы устройства при запросе одного канала. На фиг. 3 приведена временная диаграмма при запросе от нескольких каналов.

На фиг. 1 введены следующие обозначения:

11, 12, …, 1N - каналы устройства,

2 - узел анализа приоритета,

3 - первый элемент НЕ узла анализа приоритета,

4 - второй элемент НЕ узла анализа приоритета,

5 - второй элемент И узла анализа приоритета,

6 - элемент ИЛИ узла анализа приоритета,

7 - первый элемент И узла анализа приоритета,

8 - элемент ИЛИ канала,

9 - двухвходовые мультиплексоры по m разрядов,

10 - (m+1) разрядный регистр RG,

11 - элемент И устройства,

12 - синхронный RS-триггер с установкой в нулевое состояние,

13 - m разрядный буферный регистр BUF,

141, 142, 14N - входы запроса каналов Z1, Z2, …, ZN,

151, 152, …, 15N - m разрядные информационные входы каналов D1, D2, …, DN,

161, 162, …, 16N - выходы ответа каналов OTV1, OTV2, OTVN,

17 - k разрядный информационный выход Q,

18 - выход запроса обмена устройства ZG,

19 - вход сигнала окончания обмена SKO,

20 - вход разрешения работы СЕ,

21 - тактовый вход устройства ТИ,

22 - вход начальной установки CLR,

23 - вход запроса от следующего канала,

24 - вход разрешения от следующего канала,

25 - вход передачи запроса от предыдущего канала QZ,

26 - m разрядный информационный вход от предыдущего канала,

27 - выход разрешения канала,

28 - выход передачи запроса канала QZ.

Вход сброса устройства 22 соединен с соответствующими входами регистров 10, триггера 12 и буферного регистра 13. Тактовый вход 21 соединен с входами синхронизации первыми входами регистров 10, триггера 12 и буферного регистра 13.

В каждом канале 11, 12, …, 1N вход запроса канала 14 соединен с первым входом первого элемента И 7, со вторым входом элемента ИЛИ 8 и адресным входом двухвходовых мультиплексоров 9. Информационные m разрядные входы каналов 15 соединены со второй группой входов соответствующих двухвходовых мультиплексоров 9, первые группы входов которых являются m разрядными информационными входами от предыдущего канала 26, а выходы двухвходовых мультиплексоров 9 соединены с первой группой m разрядных информационных входов соответствующих регистров 10. Информационный (m+1)-й вход регистра 10 соединен с выходом элемента ИЛИ 8 канала, первый вход которого является входом передачи запроса от предыдущего канала 25.

В каждом узле анализа приоритета 2 вход первого элемента НЕ 3 является входом запроса от следующего канала 23, а выход первого элемента НЕ 3 соединен с первым входом второго элемента И 5, второй вход которого является входом разрешения от следующего канала 24, а выход второго элемента И 5 соединен со вторым входом элемента ИЛИ 6, первый вход которого соединен с выходом второго элемента НЕ 4, вход которого соединен с (m+1)-м информационным выходом регистра 10, который является выходом передачи запроса канала 28. Выход элемента ИЛИ 6 соединен со вторым входом первого элемента И 7, с входом загрузки регистра канала 10 и является выходом разрешения канала 27, выход первого элемента И 7 является выходом ответа 16 соответствующего канала 1.

В первом канале 11 вход передачи запроса от предыдущего канала 25 и m разрядный информационный вход от предыдущего канала 26 соединены с логическим нулем.

В каждом канале 12, …, 1N, кроме первого канала 11, вход передачи запроса от предыдущего канала 25 соединен с выходом передачи запроса канала 28, соответствующего предыдущего канала 11, 12, …, 1N-1, a m разрядный информационный вход от предыдущего канала 26 соединен с m разрядным информационным выходом регистра 10, соответствующего предыдущего канала 11, 12, …, 1N-1.

В каждом канале 11, 12, …, 1N-1, кроме последнего канала 1N, вход запроса от следующего канала 23 соединен с входом запроса 14, соответствующего последующего канала 12, …, 1N, а вход разрешения от следующего канала 24 соединен с выходом разрешения канала 27, соответствующего последующего канала 12, …, 1N. Вход запроса от следующего канала 23 последнего канала 1N соединен с логическим нулем.

Выход передачи запроса канала 28 последнего канала 1N соединен с первым входом элемента И 11 устройства, выход которого соединен с S-входом синхронной установки в единицу триггера 12, R-вход синхронной установки в нулевое состояние триггера 12 соединен с внешним входом окончания обмена 19. Инверсный выход триггера 12 соединен с входом разрешения от следующего канала 24 последнего канала 1N, вторым входом элемента И 11 устройства и входом загрузки буферного регистра 13. Вход разрешения работы буферного регистра 13 соединен с внешним входом разрешения работы 20.

Группа из m информационных входов буферного регистра 13 соединена с m разрядным информационным выходом регистра 10 последнего канала 1N. Информационный k разрядный выход буферного регистра 13 является k разрядным информационным выходом 17 устройства. Прямой выход триггера 12 является выходом запроса обмена устройства 18.

Принцип работы устройства состоит в следующем.

На входы каналов 11, 12, …, 1N поступают запросы 14 и m разрядные информационные данные на обмен 15. Запросы имеют свои приоритеты, жестко связанные с номером канала. В предлагаемом устройстве высший приоритет присвоен старшему последнему каналу 1N.

Регистры каналов 10 содержат (m+1) разряд. При этом m разрядов предназначены для временного (буферного) хранения данных от канала, по которому поступил запрос, или от канала с более низким приоритетом, а (m+1)-й разряд регистра обеспечивает хранение сигнала запроса QZ. Запись в регистр 10 проводится при единичном сигнале на входе загрузки L.

Единичный сигнал на входе загрузки Li регистра 10i (i=1, 2, …, N-1) формируется, если на выходе запроса (m+1)-м разряде текущего регистра 10i установлен нулевой сигнал, или если на выходе (m+1)-го разряда установлен единичный сигнал, но отсутствует сигнал запроса 14i+1 от последующего канала 1i+1 или установлен нулевой сигнал на входе загрузки L(i+1) последующего регистра 10i+1.

При записи в регистр 10i канала 1i двухвходовые мультиплексоры 9i передают либо данные с информационных входов 26 предыдущего канала, при нулевом сигнале на адресном входе, или входные данные 15i при единичном сигнале запроса 14i. Если данные 15i с входов канала 1i записаны в регистр 10i, то на выходе ответа канала 16i формируется единичный сигнал ответа OTVi=1. При этом данные еще не переданы к общему блоку, но каналу разрешается формирование следующих данных.

Таким образом, проводится прием данных из текущего канала или сдвиг данных от каналов с более низким приоритетом в сторону каналов с высшим приоритетом. Приведенный режим обмена одновременно работает по всем каналам, следовательно, при обслуживании одной заявки проводится подготовка к обслуживанию следующих заявок.

Данные в буферный регистр 13 записываются при нулевом состоянии триггера 12. Сигнал запроса передачи данных QZN с последнего канала 1N поступает на S-вход триггера 12, прямой выход которого является сигналом ZG запроса обмена устройства 18. При установленном единичном сигнале ZG=1 на выходе 18 проводится синхронная передача m разрядных данных из буферного регистра 13 по к разрядов на выход 17 по тактовым сигналам 21. По окончании передачи данных на входе 19 формируется единичный сигнал окончания обмена SKO=1, по которому триггер 12 устанавливается в нулевое состояние и разрешается загрузка следующих данных из регистра 10 последнего канала 1N.

Регистры 10, триггер 12 и буферный регистр 13 срабатывают по фронту 0/1 тактовых сигналов ТИ с входа 21. Сигналы запросов 141, 142, …, 14N и сигналы ответов 161, 162, …, 16N каналов также формируются по фронту 0/1 тактовых сигналов ТИ с входа 21.

Предлагаемое многоканальное устройство приоритета работает следующим образом.

Тактовые импульсы ТИ с входа 21 постоянно поступают на входы синхронизации регистров 10, триггера 12 и буферного регистра 13, режимы работы которых задаются сигналами на соответствующих входах управления.

При подаче единичного сигнала CLR=1 на вход сброса устройства 22 в нулевое состояние устанавливаются регистры 10, триггер 12 и буферный регистр 13.

Работа устройства начинается после установки единичного сигнала СЕ=1 на входе разрешения работы устройства 20. Далее по фронту 0/1 тактовых сигналов ТИ срабатывают регистры 10, триггер 12 и буферный регистр 13.

На временной диаграмме на фиг. 2 приведена работа предлагаемого устройства для четырех каналов (n=4), четырехразрядных данных (m=4) и передаче данных по одноразрядной шине (k=1) и запросе по первому каналу Z1=1 (данные на входах и в регистрах приведены в двоичном коде).

По фронту 0/1 первого тактового импульса ТИ формируются и поступают в устройство единичный запрос Z1=1 по входу 141 первого канала 11 и данные D1=1011. Так как в устройстве нет других запросов и не обслуженных запросов, то разрешается загрузка (единичные сигналы на входах загрузки L1-L4=1) в регистры 10 всех каналов. Одновременно на выходе ответа 161 первого канала 11 будет выработан единичный сигнал OTV1=1.

По фронту 0/1 второго тактового сигнала ТИ данные D1=1011 будут записаны в регистр 101 и сформируется нулевой сигнал ответа OTV1=0. Одновременно в (m+1)-й (пятый) разряд регистра 101 будет записан единичный сигнал запроса QZ1=1 на обмен от первого канала. По данному сигналу на следующем третьем такте ТИ данные из регистра 101 будут переданы в регистр 102, а в (m+1)-й (пятый) разряд регистра 102 будет записан единичный сигнал запроса QZ2=1 на обмен от второго канала. Аналогично проводится сдвиг на следующих трех тактах 4-6 ТИ и передача данных между регистрами 103, 104 и буферным регистром 13.

По фронту 0/1 шестого тактового сигнала ТИ также в единичное состояние переключится триггер 12, и на выходе запроса обмена устройства 18 установится единичный сигнал ZG=1. По этому сигналу начинается обмен данных с буферным регистром 13 по одноразрядной шине 17 и сдвиг данных в буферном регистре 13.

По окончании обмена (на фиг. 2 после фронта десятого тактового сигнала ТИ) на вход 19 поступает единичный сигнал окончания обмена SKO=1, по которому на следующем одиннадцатом такте ТИ триггер 12 устанавливается в нулевое состояние и формируется нулевой сигнал запроса обмена ZG=0 на выходе 18 устройства.

На временной диаграмме на фиг. 3 приведена работа предлагаемого устройства для четырех каналов (n=4), четырехразрядных данных (m=4) и передаче данных по одноразрядной шине (k=1) и запросах по третьему и четвертому каналам (данные на входах и в регистрах приведены в шестнадцатеричном коде).

По фронту первого тактового импульса ТИ в устройство поступают единичный запрос Z3=1 по входу 143 третьего канала 13 и данные D3=316(00112). Так как разрешена загрузка L3=1 в регистр 103, то формируется единичный сигнал ответа OTV3=1 на выходе 163.

По фронту 0/1 второго тактового сигнала ТИ данные D3=316 будут записаны в регистр 103, а в (m+1)-й (пятый) разряд регистра 103 третьего канала 13 будет записан единичный сигнал запроса QZ3=1 на обмен от третьего канала 13. Одновременно по единичному сигналу ответа OTV3=1 на вход 143 поступает новый сигнал запроса Z3=1 и новые данные D3=616, а также вновь будет установлен единичный сигнал ответа OTV3=1 на выход 163, так как разрешена загрузка L3=1 в регистр 103.

По фронту 0/1 третьего тактового сигнала ТИ данные D3=616 будут записаны в регистр 103, а в (m+1)-м (пятом) разряде регистра 103 будет сохранен единичный сигнал запроса QZ3=1 на обмен от третьего канала 13. Одновременно данные RG3=316 из регистра 103, будут записаны в регистр 104 RG4=316 и в (m+1)-й (пятый) разряд регистра 104 будет записан единичный сигнал запроса QZ4=1 на обмен от четвертого канала 14. Кроме того, в третий канал 13 поступает сигнал следующего запроса Z3=1 и новые данные D3=516, в четвертый канал поступает сигнал запроса Z4=1 и данные D4=416, а также формируется единичный сигнал ответа OTV4=1 на выходе 164 четвертого канала 14. При этом формируется нулевой сигнал разрешения записи L3=0 в регистр 103 и нулевой сигнал ответа OTV3=0 на выходе 163 третьего канала 13, так как данные D3=516 не могут быть приняты в регистр 103 третьего канала 13.

По фронту 0/1 четвертого тактового сигнала ТИ данные D4=416 будут записаны в регистр 104, а в (m+1)-м (пятом) разряде регистра 104 будет сохранен единичный сигнал запроса QZ4=1 на обмен от четвертого канала 14. Одновременно данные RG4=316 будут записаны в буферный регистр 13, а по единичному сигналу QZ4=1 через элемент И 11 триггер 12 установится в единичное состояние и выработается единичный сигнал ZG=1 на выходе запроса обмена устройства 18.

Далее на тактах 5-8 проводится обмен и сдвиг в буферном регистре 13. При этом запись в регистры 103 и 104 не проводится, так как нулевые сигналы установлены на входах разрешения загрузки L3=0 и L4=0.

По фронту 0/1 седьмого такта ТИ формируется единичный сигнал окончания обмена SKO=1, по которому на следующем восьмом такте ТИ триггер 12 устанавливается в нулевое состояние и формируется нулевой сигнал запроса обмена ZG=0 на выходе 18 устройства. По фронту 0/1 восьмого такта ТИ формируются сигналы разрешения записи L3=1 и L4=1 в регистры 103 и 104 и соответственно единичный сигнал OTV3=1.

По девятому тактовому сигналу D3=516 записываются регистр 103, предыдущие данные RG3=616 из регистра 103, будут записаны в регистр 104 RG4=616, данные RG4=416 будут записаны в буферный регистр 13, а по единичному сигналу QZ4=1 через элемент И 11 триггер 12 установится в единичное состояние и выработается единичный сигнал ZG=1 на выходе запроса обмена устройства 18. Одновременно нулевые сигналы будут установлены на входах разрешения загрузки L3=0 и L4=0 в регистры 103 и 104.

Далее на тактах 10-13 проводится обмен и сдвиг в буферном регистре 13. При этом запись в регистры 103 и 104 не проводится, так как нулевые сигналы установлены на входах разрешения загрузки L3=0 и L4=0.

По двенадцатому тактовому импульсу формируется единичный сигнал окончания обмена SKO=1, который поступает на вход 19 и R-вход установки в нулевое состояние триггера 12.

По тринадцатому тактовому импульсу ТИ триггер 12 устанавливается в нулевое состояние, и формируются сигналы разрешения записи L3=1 и L4=1 в регистры 103 и 104, по которым на следующем четырнадцатом такте проводится запись в регистр 104 данных RG4=516 и данных RG4=616 в буферный регистр 13, формирование нулевого сигнала L4=0 и установка нулевого сигнала QZ3=0 на (m+1)-м (пятом) разряде регистра 103. Так как на входе разрешения регистра 103 третьего канала 13 присутствует единичный сигнал L3=1, то в данный регистр возможен прием новых данных D3 по сигналу запроса третьего канала Z3=1 или данных из регистров 10 каналов с меньшим приоритетом по входам 26.

Далее на тактах 15-18 аналогично проводится обмен данных и сдвиг в буферном регистре 13. Одновременно на восемнадцатом такте ТИ устанавливается единичный сигнал L4=1 разрешения записи в регистр 104, по которому на следующих тактах проводится запись данных из регистра 103 в регистр 104, а также запись в регистр 103 третьего канала 13, так как установлен единичный сигнал L3=1 на входе записи.

На девятнадцатом такте ТИ проводится запись данных из RG4=516 в буферный регистр 13 и обмен данными на следующих тактах 19-23. Одновременно устанавливается нулевой сигнал QZ4=0 на (m+1)-м (пятом) разряде регистра 104, который указывает на отсутствие следующих запросов на обслуживание.

На тактах 20-23 ТИ проводится обмен и сдвиг в буферном регистре 13. На двадцать третьем такте по единичному сигналу SKO=1 триггер 12 устанавливается в нулевое состояние.

Таким образом, в предлагаемом устройстве организовано совмещение обработки текущего запроса, одновременный параллельный поиск следующих запросов по всем каналам и формирование сигналов ответа в каналы, а также продвижение запросов, за счет сдвига между регистрами, в сторону каналов с более высоким приоритетом.

Вышеизложенные сведения позволяют сделать вывод, что предлагаемое многоканальное устройство приоритета обладает регулярностью узлов и связей, практически однородной структурой, при этом упрощается конструкция и, следовательно, устройство соответствует заявляемому техническому результату - сокращение аппаратных затрат, увеличение быстродействия, повышение надежности, расширение функциональных возможностей в части совмещения обслуживания запроса и поиска следующих запросов.

Изобретение относится к области вычислительной техники и может быть использовано для арбитража в системах обработки информации при организации передачи данных от абонентов к устройству общего пользования. Техническим результатом изобретения является повышение надежности и быстродействия устройства путем совмещения обслуживания запроса и поиска следующих запросов. Устройство содержит N каналов 11, 12, …, 1N, N запросных входов 141, 142, …, 14N, N выходов ответа канала 161, 162, …, 16N, элемент И 11 устройства, синхронный RS-триггер 12, m разрядный буферный регистр 13, k разрядный информационный выход 17, выход запроса обмена устройства 18, вход окончания обмена 19, вход разрешения работы 20, тактовый вход 21, вход начальной установки 22, при этом каждый канал 11, 12, …, 1N содержит элемент ИЛИ 8, двухвходовые мультиплексоры по m разрядов 9, (m+1) разрядный регистр 10 и узел анализа приоритета 2, причем каждый узел анализа приоритета 2 содержит первый элемент НЕ 3, второй элемент НЕ 4, второй элемент И 5, элемент ИЛИ 6, первый элемент И 7, элемент ИЛИ 6. 3 ил.

Многоканальное устройство приоритета, содержащее N каналов 11, 12, …, 1N, Ν запросных входов 141, 142, …, 14N, N выходов ответа канала 161, 162, …, 16N, тактовый вход 21, при этом каждый канал 11, 12, …, 1N содержит элемент ИЛИ 8 и узел анализа приоритета 2, причем каждый узел анализа приоритета 2 содержит первый элемент И 7, элемент ИЛИ 6, первый элемент НЕ 3, информационный выход канала 16 и запросный вход канала 14, который соединен с первым входом первого элемента И 7, отличающееся тем, что в него дополнительно введены элемент И 11 устройства, синхронный RS-триггер 12, m разрядный буферный регистр 13, k разрядный информационный выход 17, выход запроса обмена устройства 18, вход окончания обмена 19, вход разрешения работы 20, вход начальной установки 22, кроме того, в каждом канале 11, 12, …, 1N введены двухвходовые мультиплексоры по m разрядов 9, (m+1) разрядный регистр 10, соответствующие m разрядные информационные входы каналов 151, 152, …, 15N, вход запроса от следующего канала 23, вход разрешения от следующего канала 24, вход передачи запроса от предыдущего канала 25, m разрядный информационный вход от предыдущего канала 26, выход разрешения канала 27, выход передачи запроса канала 28, а в каждый узел анализа приоритета 2 дополнительно введены второй элемент НЕ 4, второй элемент И 5, причем вход сброса устройства 22 соединен с соответствующими входами регистров 10, триггера 12 и буферного регистра 13, тактовый вход 21 соединен с входами синхронизации первыми входами регистров 10, триггера 12 и буферного регистра 13, в каждом канале 11, 12, …, 1N вход запроса канала 14 соединен со вторым входом элемента ИЛИ 8 и адресным входом двухвходовых мультиплексоров 9, m разрядные информационные входы каналов 15 соединены со второй группой входов соответствующих двухвходовых мультиплексоров 9, первые группы входов которых являются m разрядными информационными входами от предыдущего канала 26, а выходы двухвходовых мультиплексоров 9 соединены с первой группой m разрядных информационных входов соответствующих регистров 10, (m+1)-й информационный вход регистра 10 соединен с выходом элемента ИЛИ 8 канала, первый вход которого является входом передачи запроса от предыдущего канала 25, в каждом узле анализа приоритета 2 вход первого элемента НЕ 3 является входом запроса от следующего канала 23, а выход первого элемента НЕ 3 соединен с первым входом второго элемента И 5, второй вход которого является входом разрешения от следующего канала 24, а выход второго элемента И 5 соединен со вторым входом элемента ИЛИ 6, первый вход которого соединен с выходом второго элемента НЕ 4, вход которого соединен с (m+1)-м информационным выходом регистра 10, который является выходом передачи запроса канала 28, выход элемента ИЛИ 6 соединен со вторым входом первого элемента И 7, с входом загрузки регистра канала 10 и является выходом разрешения канала 27, выход первого элемента И 7 является выходом ответа 16 соответствующего канала 1, в первом канале 11 вход передачи запроса от предыдущего канала 25 и m разрядный информационный вход от предыдущего канала 26 соединены с логическим нулем, в каждом канале 12, …, 1N, кроме первого канала 11, вход передачи запроса от предыдущего канала 25 соединен с выходом передачи запроса канала 28, соответствующего предыдущего канала 11, 12, …, 1N-1, а m разрядный информационный вход от предыдущего канала 26 соединен с m разрядным информационным выходом регистра 10, соответствующего предыдущего канала 11, 12, …, 1N-1, в каждом канале 11, 12, …, 1N-1, кроме последнего канала 1N, вход запроса от следующего канала 23 соединен с входом запроса 14, соответствующего последующего канала 12, …, 1N, а вход разрешения от следующего канала 24 соединен с выходом разрешения канала 27, соответствующего последующего канала 12, …, 1N, вход запроса от следующего канала 23 последнего канала 1N соединен с логическим нулем, выход передачи запроса канала 28 последнего канала 1N соединен с первым входом элемента И 11 устройства, выход которого соединен с S-входом синхронной установки в единицу триггера 12, R-вход синхронной установки в нулевое состояние триггера 12 соединен с внешним входом окончания обмена 19, инверсный выход триггера 12 соединен с входом разрешения от следующего канала 24 последнего канала 1N, вторым входом элемента И 11 устройства и входом загрузки буферного регистра 13, вход разрешения работы которого соединен с внешним входом разрешения работы 20, группа из m информационных входов буферного регистра 13 соединена с m разрядным информационным выходом регистра 10 последнего канала 1N, k разрядный информационный выход буферного регистра 13 является k разрядным информационным выходом 17 устройства, прямой выход триггера 12 является выходом запроса обмена устройства 18.

| US 4318185, 02.03.1982 | |||

| DE 2846686 B1, 27.09.1979 | |||

| УСТРОЙСТВО ДЛЯ ПОСТРОЕНИЯ ПРОГРАММИРУЕМЫХ ЦИФРОВЫХ МИКРОПРОЦЕССОРНЫХ СИСТЕМ | 2003 |

|

RU2254603C1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2007 |

|

RU2364920C2 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 1992 |

|

RU2108618C1 |

| Многоканальное устройство приоритета | 1983 |

|

SU1119014A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2002 |

|

RU2231111C2 |

Авторы

Даты

2016-07-10—Публикация

2015-04-10—Подача