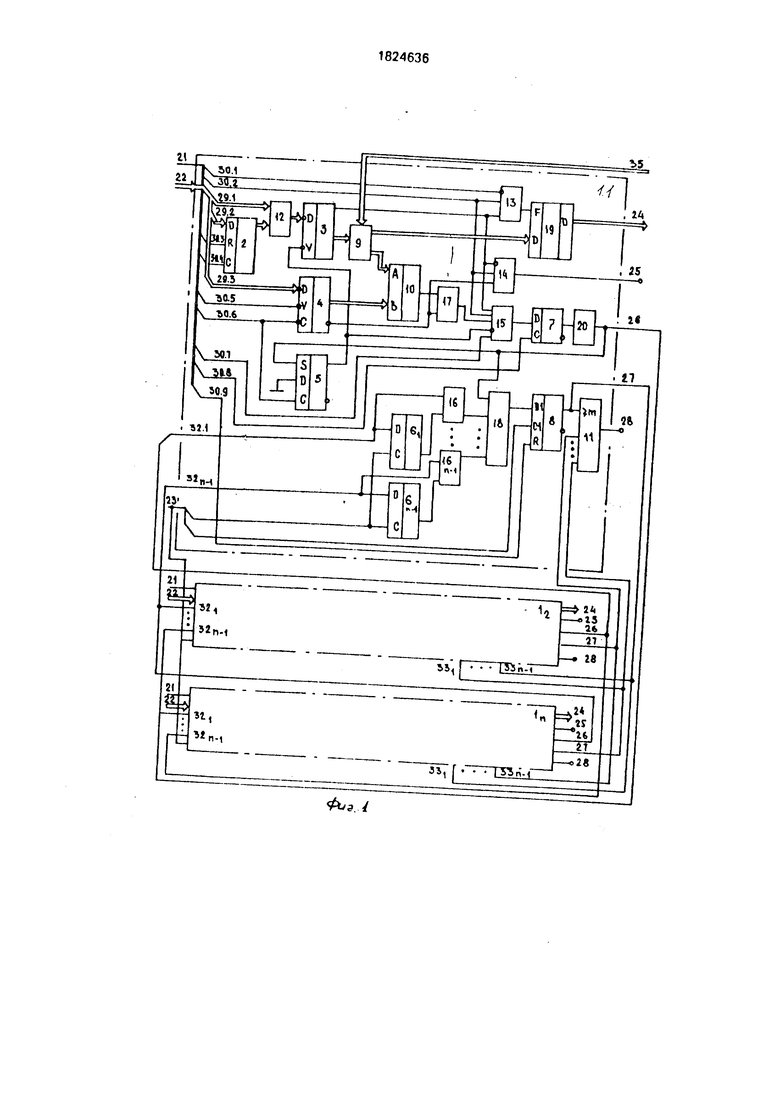

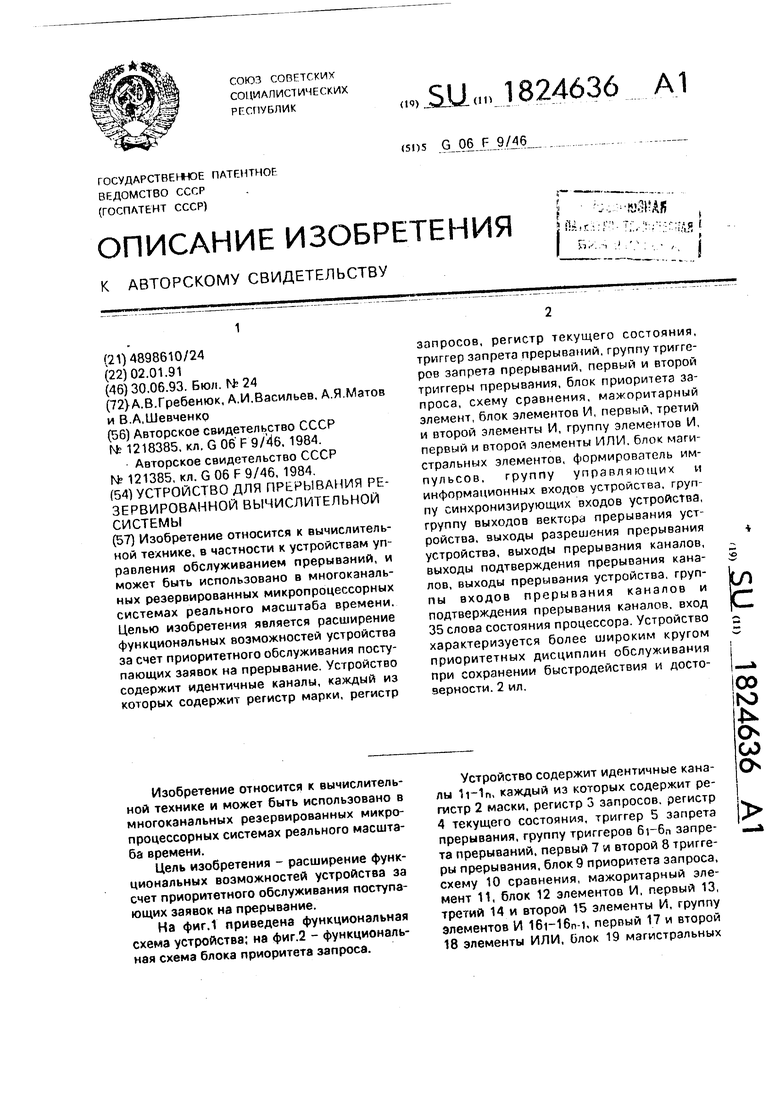

элементов, формирователь 20 импульсов, групповые управляющие 21 и информационные 22 входы устройства, групповой синхронизирующий вход 23 устройства, групповые выходы 24 вектора прерывания устройства, выходы 25 разрешения прерывания устройства, выходы 26 прерывания каналов, выходы 27 подтверждения прерывания каналов, выходы 28 прерывания устройства, входы первой 29.1, второй 29.2 и третьей 29.3 групп разрядов группового информационного входа 22 устройства, входы первого - девятого 30.1-30.9 разрядов группового управляющего входа 21 устройства, входы первого 31.1 и второго 31.2 разрядов группового синхронизирующего входа 23 устройства, группы входов 32i-32n-i прерывания каналов, группы входов 331-ЗЗп-1 подтверждения прерывания каналов, вход 35 слова состояния процессора.

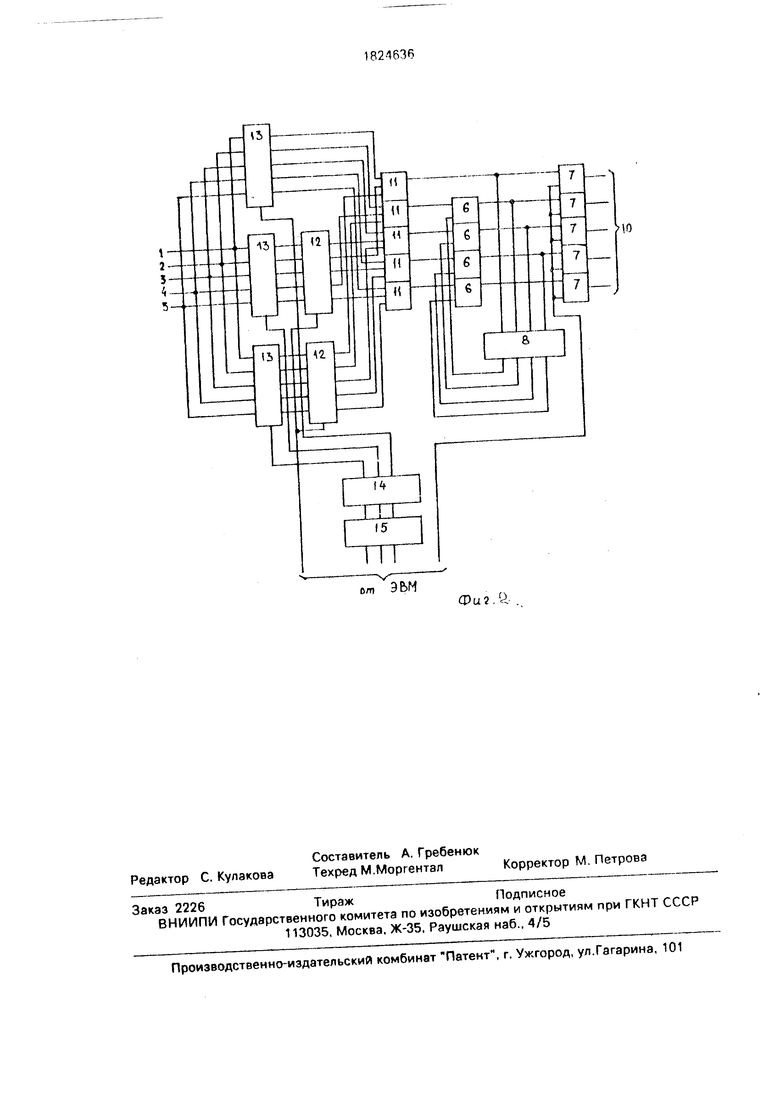

Схема блока приоритета запроса содержит запросные входы 1-5, группу элементов И 6. группу элементов И 7, узел 8 анализа запросов, опросный вход, группу выходов устройства 10, блок элементов ИЛИ 11, блоки приоритета 12, блоки элементов ЗАПРЕТ

13,дешифратор 14, регистр приоритета 15, синхрорход.

Элементы блока соединены следующим образом. Входы 1-5 соединены с соответствующими входами блоков 13 элементов ЗАПРЕТ. Выходы первого блока элементов ЗАПРЕТ подключены к первым входам блока 11 элементов ИЛИ, а выходы второго и третьего блоков (нумерация - сверху вниз) элементов ЗАПРЕТ - к соответствующим входам блоков 12 приоритета, первый из которых предназначен для реализации приоритета с циклической, а второй - приоритета с динамической дисциплиной обслуживания. Входы регистра 15 приоритета подключены к управляющим выходам ЭВМ, а его выходы - к входам дешифратора

14,выходы которого соединены с запрещающими входами блоков 13 элементса ЗАПРЕТ. Выходы блока 11 элементов ИЛИ подключены: первый - к входу первого элемента И группы 7, остальные - к входам соответствующих элементов И группы 6. синхровход подключен к синхровходу второго блока 12 приоритета, остальные элементы соединены, как показано в описании авт.св. СССР № 1070553.

Линейная дисциплина приоритетного обслуживания реализована в той части устройства, которая известна по авт.св. СССР № 1070553, циклическая и динамическая дисциплины реализованы на программируемых логических матрицах типа К 556 РТ 1.

Работа этой схемы блока приоритета достаточно проста, ясна из прототипа и не требует дополнительных пояснений.

Элементы устройства обьединены следующим образом: входы первого и второго разрядов 30.1 и 30.2 группового управляющего входа 21 устройства соединены с первым и вторым входами первого элемента И, выход которого подключен к F-входу блока

19 магистральных элементов, выход которого является групповым выходом 24 вектора прерывания устройства, а входы третьего и четвертого разрядов 30.3 и 30.4 группового управляющего входа 1 устройства соедипены с R- и С-входами регистра 2 маски, выход которого подключен к вторым входам блока 12 элементов И, первые входы которого соединены с входами первой группы разрядов 29.1 группового информэционнбго входа устройства 22, а выходы - с D-вхо- дэми регистра 3 запросов, V-вход которого подключен к прямому выходу триггера 5 запрета прерываний, а выходы; 3.1 - к третьим входам первого, второго и третьего элементов И 13, 15, 14; 3.2 - к входу блока 9 приоритета запроса, выходы которого соединены с D-входами блока 19 магистральных элементов и А-еходом схемы 10 сравнения, В-вход которой подключен к выходу регистра 4 текущего состояния, D-вхо- ды которого соединены с третьей группой разрядов 29.3 группового информационного входа 22 устройства, а V- и С-входы - с входами 5 и 6 разрядов 30,5 и 30.6 группового управляющего входа 21 устройства соответственно, вход 7 разряда 30.7 группового управляющего входа 21 устройства подключен к четвертому входу второго элемента И 15, второй вход которого соединен с выходом первого элемента ИЛИ 17. а выход - с D-входом первого триггера 7 прерываний, прямой выход которого под ключей к входу формирователя 20 импульсов, выход которого соединен с S-входом

триггера 5 запрета прерываний, первым входом второго элемента ИЛИ 18, является входом 32 прерывания каналов и выходом 26 прерывания каналов, второй вход третьего 14 и первый вход второго 15 элементов

и соединены с вторым разрядом 30.2 труп нового управляющего входа 21 устройства, выход третьего элемента И 14 является выходом 25 разрешения прерывания устр ойст- ва, а третий вход элемента И 15 подключен

к прямому выходу триггера 5 запрета прерываний, инверсный выход регистра 4 текущего состояния соединен с вторым входом первого элемента ИЛИ 17 и с первым входом третьего элемента И 14, восьмой разряд

30.8 группового управляющего-вход; 21 устройства подключен к С-входу первого триггера 7 прерывания, а девятый разряд 30.9 группового управляющего входа 21 соединен с R-входом второго триггера 8 прерываний, входы первого 31.1 разряда группового синхронизирующего входа 23 подключены к синхровходам группы триггеров запрета прерываний, которые устанавливаются по сигналам прерываний каналов по входам 32i-32n-i, а второй разряд 31.2 группового синхронизирующего входа 23 соеди- нены с входом С1 второго триггера 8 прерываний, единичный выход которого подключен к первому входу мажоритарного элемента 11 и соответствующему входу группы подтверждения прерывании каналов, выход мажоритарного элемента 11 является выходом 28 прерывания устройства, а входы мажоритарного элемента 11 со второго до n-й являются соответственно входами группы подтверждения прерывания каналов ЗЗг-ЗЗп-1 и соединены с выходами соответствующих триггеров 8 каналов, инверсные выходы триггеров группы 6 запрета прерываний соединены с первыми входами элементов И группы 16, вторые входы которых подключены к группе входов 32 прерывания каналов, а выходы - к соответствующим входам второю элемента ИЛИ 18, выход которого соединен с входом D1 второго триггера 8 прерывания, вход второй группы 29.2 разрядов группового информационного входа устройства подключен к О-входу регистра 2 маски, синх- ровход триггера 5 запрета прерываний соединен с синхровходом регистра 4 текущего состояния, а D-вход триггера 5 запрета прерываний соединен с корпусом.

В исходном состоянии все элементы памяти установлены в нулевое состояние (входы начальной установки не представлены).

Для приведения устройства в рабочее состояние на входы 30.2 и 30.5 групповых управляющих входов 21 устройства подаются единичные сигналы. Кроме того, с входом 29.3 групповых информационных входов устройства в регистры 4 запросов всех каналов 1i (,п) записывается код текущего состояния программы (в начале нулевой код), выполняемой системой, по синхроимпульсу с входа 30.6. По этому же синхроимпульсу осуществляется установка в нулевое состояние триггера 5 запрета прерываний. При этом нулевой сигнал с выхода триггера 5 разрешает запись запросов на прерывания в регистр 3.

Регистр 2 масок устанавливается в нулевое состояние по сигналу с входа 30.3. По этому же сигналу осуществляется установка в исходное состояние микропроцессора

(класса INTEL 8080 или К580ВМ80, К580ВМ80) многоканальной мажоритарно- резервированной системы.

После выполнения указанных операций устройство готово к работе.

На группов.ые входы 22 устройства поступают информационные сигналы, прома- жоритированные по всем п каналам резервированной системы. Запись кода ма0 ски прерываний в регистр 2 осуществляется с входа 29.2 по сигналу с входа 30.4, который соответствует сигналу Выдача микропроцессорной системы на базе К580ВМ80. Код маски с выходов регистра 2 посту5 пает на входы блока 12 элементов И, через которые осуществляется фильтрация сигналов запросов на прерывания, поступающих с входов 29.1 запросов. При этом любой незамаскированный сигнал запроса посту0 пает на D-входы регистра 3 запросов.

Если в регистре 3 сигналы запросов отсутствуют, то блок 9 приоритета запроса закрывает блок 19 магистральных элементов, запрещает выработку сигнала подтвер5 ждения прерывания через элемент ИЛИ 17 и разрешает выработку сигнала разрешения прерывания на выходе элемента И 14.

При поступлении сигналов запросов прерывания с выходов блока 12 элементов

0 И происходит их запоминание в регистре 3. Однако запрос после этого с выходов 29.1 не снимается, так как регистр 3 выполнен на триггерах типа защелка, и запоминание информации в регистре 3 произойдет толь5 ко после установки триггера 5 в единицу.

Информация с выхода 3.1 регистра 3 поступает на входы блока 9 приоритета запроса, который в соответствии с заданной по входу 35 процессора дисциплиной обслу0 живаиия (в порядке поступления, циклическая, динамическая) /2/ выбирает сигнал прерывания старшего приоритета. Сигналом с выхода 3.2 регистра 3, формируемым при наличии хотя бы одного запроса в реги5 стре, открывается элемент И 13, выходной сигнал которого открывает блок 19 магистральных элементов и разрешает передачу через него на выход 24 канала кода прерывания системы. Кроме того, разрешается

0 срабатывание элемента И 15 и запрещается выдача сигнала разрешения с выхода элемента И 14 на выход 25 устройства.

При работе блока 9 приоритета запроса в циклической дисциплине или в порядке

5 поступлений его выходной код выдается также на входы А схемы 1C, где осуществляется его сравнение с кодом текущей программы, записанным в регистр 4. Если код с входа А больше кода с входа В схемы сравнения 10, то с ее выхода выдается сиг

нал, который через .элемент ИЛИ 1 / и открытый элемент И 15 поступает на D-вход триггера 7. В противном случае (динамическая дисциплина) процессор сам выбирает запрос нужного уровня приоритета и переписывает его по сигналу микропроцессор готов, поступающему с входа 35, через открытый блок магистральных усилителей 19. Во всех остальных случаях (дисциплины в порядке поступления, обратная) на выходе схемы 10 сигнал отсутствует. Тогда сигнал подтверждения прерывания может быть вы- ряботам только в том случае, если в четвертый разряд регистра 4 по входу 30.5 будет записан нуль, гак как инверсный выход этого разряда через элемент ИЛИ 17 функцио- на.и.ни лкпиплпентон выходу схемы 10.

При наличии сигнала на выходе схемы 10 с поступлением разрешающего сигнала с входа 30.7 и синхроимпульса с входа 30.8 осуществляется запись единицы в триггер 7. Сигнал с единичного выхода триггера 7 че- ряз элемент 20 поступает на вход триггера 5 который устанавливается в единицу. При ком разрешает прием новых сигналов запросов в регистр 3 и подготавливается триг- i ер 7 к сбросу в нулевое состояние. Поэтому с приходом очередного импульса с входа 30.8 происходит установка триггера 7 в нулевое состояние Таким образом, длительность существования сигнала на выходе триг герч 7 определяется периодом следования импуппсов с входа 30.8.

Формирователь 20 формирует единич ныи импульс на выходе 26 после установки i jivirrpps 7 в единичное состояние,

Длч топ чтобы исключить возможности двойного прерывания по одному и тому же запросу, а также прерывания по запросам младшНх приоритетов относительно обрабатываемого, необходимо после обработки сигнала прерывания, формируемого с выходов 28 каналов, код программы обработки запроса записать в регистр 4 состояния аналогично описанному.

Если а этом нет необходимости, то в регистр 4 записывается нулевой код по сигналу с входа 30.6. В результате этого снова устанавливается в нуль триггер 5 и осуществляется подготовка устройства к приему очередного запроса на прерывание.

После формирования сигналов прерывания на выходах 26 каналов они поступают на соответствующие входы 32i-32n-i каждого из остальных каналов,

В каждом канале сигналы прерываний от остальных каналов поступают на D-входы соответствующих триггеров и на первые входы соответствующих элементов И 16i- 16n 1. При отсутствии отказов каналов

сигна.,1 с входов 32i 32n-i поступают в но синхроимпульса, предназначенного для выявления ложной выдачи сигнала прерывания, с входа 31.1. Поэтому 6i-6n 1

сигналами с нулевых выходов открывают элементы И 16i 16n-i- Таким образом, выходной сиг нал канала с выхода формирова теля 20 или остальных канэлоа с выходов элементов И 16|-)6л 1 через элемент ИЛИ

18 поступают на D-вход триггера 8 I lo сигналу синхроимпульса опроса прерывания с входа 31.2 происходи установка триггера 8 в единичное состояние, Сигнал с единичного выхода триггера 8 чррез выход J7 канала

поступает на соответствующие входы группы входов ЗЗт-ЗЗп 1 из осглльны каналов и далее - на входы мажоритарного элемента 11. Мажоритарный элемент I срабатывает при наличии в большинстве каналов сигналов прерывания и выдает на выход 28 устройства сигнал прерывания н соответствующий канат системы.

В случае возникновения отказа, связанного с зависанием каналов, сигнал прпры

вания от такого канала обнлружипается и момемт подачи синхроимпульса с входа 31,1, по которому соответствующий триггер из группы триггеров Pi -6lt i устанавливается в единицу и блокирует прохождение это

m сигнала через соответствующий элемент И группы члсментон И 16i 1Gn 1

Ф о р N: у л а из и f- р с i о н и i Упрои „тг;,) длч пре ывзии р з рвиросанной вычислительной систем,, содержа щее п ,ачалое (где п числе л;, тросов), каждый из которых включает d ( .« регистр мягки, регистр запросов, регистр состоятся, триггер запрета прерчвония

два триггера прерывэ-гир, схому срлннения, Ъпак 0/JOMCHTOB И, три элемента И, ,вл оле- мента ИЛИ. блок мат истральннхэлеменгоп формирователь импульсов, группу тригге ров запрета прерываний, мажоритарный

элемент, группу элементов И, причем в каж дом канале пярвые группы управляющих и информационных входов устройства соеди йены с группами одноименных входоп кэма лоп, первый разрешающий вход, первые

входы приведения п рабочее состояние, ход сброса, второй разрешающий в«од и второй вход установки з О группы управляющих входов канала соединены с группой инверсных входов первого элемента И, первым прямым входом первою элемента И, зходом сброса регистра маски, входом спи- хрочизчции регистра маски, входом разрс шения регистра текущего состояния, входами синхронизации регистра состояния и триггера Зоппетз прлры энии

первым входом второго .nw-in- И . чхо дом синхронизации первого ч пг-рг. чрс-- рыванип соответственно пепчлп., З праг и третьи подгруппы разрядов группа информационных входов к)нэлн г.оодмнятп о ответствен но с первой группой входов блока элементов И, группой информациончь1 ; входов регчсгрз текущего состояния, группа выходом которого соединима с лерчол группой входов схемы сравнения, групп- выходов регистра маски соединена с второй группой входов блока элементов -.А. аыход;, которого соединены с группой информационных .ходов регистра запросов, выход первою элемента И соединен с входом разрешения б л о к а магистральных элементов, инверсный выход регистра текущего состояния соединен с мерными входами перпого элемента ИЛИ и третьего элемента И, информационный вход триггера запрета прерываний соединен с шиной нулевого потенциала устройства, единичный выход триггера запрета прерываний соединен с входом разрешения регистра запросе и инверсным входом второго элемента И, выход схемы сравнения соединен с вторым входом первого элемента ИЛИ, ПУУ-Д которою соединен С ВТОРЫМ ВХОДОМ Г), ::лп; :0( Т9

И, первый вход приведения a pafio -.. состояние группы управляющих входор канала соединен с вторым прямым входом тг.етьего элемента И и третьим прямым входом второго элемента И, выход регистра запросов соединен с вторым прямым аходом пепвого элемента И. инверсным входом третьего элемента И и четвертым прямым входом второго элемента И, выход которого соединен с информационным входом первой.: фиггера прерывания, прямой, выход которого через формирователь импульсов соединен с инверсным единичным входом триггера запрета прерываний, инверсные выходы триггеров запрета прерываний группы соединены с первыми входами соответствующих элементов И группы, группа входов прерываний канала соединена с информационными входами три1геров запре та прерываний группы и вторыми входами

. l/i . .. . P;.:MV vi . -jinrre- ;/оP. .p.npv.;; пр1-р-- --Я( и; .i Cf:e; -ni i U i

i. Г. «ОГ: М (:;. ЧО РРГ р- Д;5 .pynnij C .IH.spOtly-.(.1. v.тро -стза чхо/i f ionni4; разряда h rpYi;;;i- r. .y/. устройства соединен cci- .:г. 0.ходом второго триггера прорывами . ФО Ма11ИО М- ЫЙ И МуЛСРОЙ УГЛЗНОПОЧ -ni г. ходы которого гл -дияены соотпстг.теенно с выходом второго элемен0 та v- 3x0,40м подтверждения прерываний группы у1ФЯ1;пяющих г Аодог канала, элеменгоп Л группн соединены с нхоляг :и второго элемента И.ПИ, иыход пто- г.ого фиггерз прерывания соединен с перВ озим входом магистральчсго элемента, остальные пходы которого сойдинены с со- ответсгоующими входами группы входов подтверждения прерывания канала, выход формирователя импульсов соед инон с соот0 ве гствующим входом гзторого элемента ИЛИ. группа выходов блока мчгисгрлльных элементов и выход третьего элемента И яп- япюгся соответстпенно группой пмходов вектора прерып&нмя и выходом разрешения

5 пргрывзния устройства, выход магистрального элемента Б ка:-: ,цом канале является выходом прерыпанич yciПОЙСТРЗ, выход Фор .иповзтепя импульсов риляется выходом прарыьяния кснлла, выход второго

0 триперр п :ерыгс ;и .й является выходом под 1г ер хденир ппгрывания канала, вихо- дь: прерывания и подтверждения каждого канпла соединены с cooiнетсгвующими входами одноименных групп входов каждого из

5 остальных канэлпр, отличающееся тем, что, г, целью рзсил1рения функциональных возможностей устройства за счет приоритетного обслуживания поступающих заявок ип прерыпэние, устройство содер0 ;;сит блок iTpv pnreTa запросов, первая и вторая группы информационных входов которого соединены с группой выходов регистра з-чпросоп и группой входов состояния слова устройства, группа выходов блока

5 приоритета запросов соединена с второй группой входов схемы сравнения и группой информационных входов блока магистральных элементов

Фиг. О..

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для прерывания резервированной вычислительной системы | 1984 |

|

SU1218385A1 |

| Устройство прерываний микропроцессорной системы | 1988 |

|

SU1621030A1 |

| Устройство приоритета | 1989 |

|

SU1633404A1 |

| Устройство для формирования сигнала прерывания | 1987 |

|

SU1432522A1 |

| Устройство формирования сигнала прерывания и обмена | 1985 |

|

SU1269133A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для сопряжения к абонентов с М вычислительными машинами | 1987 |

|

SU1411758A1 |

| Устройство для отладки программно-аппаратных комплексов | 1990 |

|

SU1795464A1 |

| Устройство для обслуживания запросов | 1982 |

|

SU1109753A1 |

| Устройство обмена информацией | 1987 |

|

SU1532941A1 |

Изобретение относится к вычислительной технике, в частности к устройствам управления обслуживанием прерываний, и может быть использовано в многоканальных резервированных микропроцессорных системах реального масштаба времени. Целью изобретения является расширение функциональных возможностей устройства за счет приоритетного обслуживания поступающих заявок на прерывание. Устройство содержит идентичные каналы, каждый из которых содержит регистр марки, регистр Изобретение относится к вычислительной технике и может быть использовано в многоканальных резервированных микропроцессорных системах реального масштаба времени. Цель изобретения - расширение функциональных возможностей устройства за счет приоритетного обслуживания поступающих заявок на прерывание. На фиг.1 приведена функциональная схема устройства; на фиг.2 - функциональная схема блока приоритета запроса. запросов, регистр текущего состояния, триггер запрета прерываний, группу триггеров запрета прерываний, первый и второй триггеры прерывания, блок приоритета запроса, схему сравнения, мажоритарный элемент, блок элементов И, первый, третий и второй элементы И, группу элементов И, первый и второй элементы ИЛИ. блок магистральных элементов, формирователь импульсов, группу управляющих и информационных входов устройства, группу синхронизирующих входов устройства, группу выходов вектора прерывания устройства, выходы разрешения прерывания устройства, выходы прерывания каналов, выходы подтверждения прерывания каналов, выходы прерывания устройства, группы входов прерывания каналов и подтверждения прерывания каналов, вход 35 слова состояния процессора. Устройство характеризуется более широким кругом приоритетных дисциплин обслуживания при сохранении быстродействия и достоверности. 2 ил. Устройство содержит идентичные каналы 1i-1n, каждый из которых содержит регистр 2 маски, регистр 3 запросов, регистр 4 текущего состояния, триггер 5 запрета прерывания, группу триггеров 6i-6n запрета прерываний, первый 7 и второй 8 триггеры прерывания,блок 9 приоритета запроса, схему 10 сравнения, мажоритарный элемент 11, блок 12 элементов И, первый 13, третий 14 и второй 15 элементы И, группу элементов И 16i-16n-i, первый 17 и второй 18 элементы ИЛИ, блок 19 магистральных (Л С 00 N5 4 О СО ON

| Устройство для прерывания резервированной вычислительной системы | 1984 |

|

SU1218385A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1993-06-30—Публикация

1991-01-02—Подача