которого соединены соответственно с первым входом блока синхронизации, управляю, шим входом регистра адреса, и управляющим входом первого мультиплексора, выход кот.орого соединен с входом регистра информации, выход которого соединен с информационными входами регистра адреса и блока оперативной памяти, адресный вход которого соединен с выходом регистра адреса и адресным входом блока сопряжения с полупроводниковым блоком постоянной памяти, информационный выход которого соединен с третьим информационным входом первого мультиплексора, вход записи блока сопряжения соединен с выходом программируемого генератора, управляющей вход которого соединен с выходом блока сравнения, входы которого соединены соответственно с выходами второго и tpeTbero мультиплексоров разрядов, управляющие входы KOTopbij( соединены с выходо.м регистра разрядов информации, управляющие выходы блока синхронизации соединены соответственно с управляющими входами блока управления внещним носителем информации, блока оперативной памяти и блока сопряжения с полупроводниковым блоком постоян ной памяти, тактовые входы-выходы блока синхронизации соединены соответственно с тактовыми входами-выходами регистра адреса, регистра разрядов, блока сравнения и программируемого генератора.

Кроме того, входы второго и третьего мультиплексоров разрядов информации, подключены к информационному выходу блока оперативной памяти, блок синхронизации

. содержит генератор, счетчик и распределитель импульсов, а в качестве блока внешних носителей информации используются фотосчитыватель с перфолент или перфокарт 4}. Основным недостатком этого устройства является низкое быстродействие, так как все операции проводятся последовательно и отсутствуют средства совмещения контроля блоков памяти, подбора информации к дефектным блокам памяти и т.д. из-за недостаточной функциональной гибкости устройства, следствием чего является его малая надежность..

Цель изобретения - увеличение быстродействия и надежности устройства для записи информации в полупроводниковые блоки памяти, что ведет к повыщению производительности и экономии общественного труда..

Поставленная цель достигается тем, что

в устройство введены четвертый и пятый мультиплексоры, первые информационные входы которых соединены с выходом блока оперативной памяти, информационный вход которого соединен со вторыми информационч ными входами четвертого и пятого, мультиплексоров, третий информационный вход пятого мультиплексора соединен с информационным выходом блока сопрпжения, управу1яющие входы четвертого и пятого мультиплексоров соединены с соответствующими выходами блока синхронизации, выход четвертого мультиплексора соединен с информационным входом второго мультиплексора и с входом задания порога блока сопряжения, -выход пятого мультиплексора соединен с информационным входом третьего мультиплексора, выход программируемого генератора соединен с входом записи блока оперативной памяти, а соответствующие выходы и входы блока сопряжения подключены к соответствующим выходам и входам устройства. Кроме того, блок сопряжения содержит адресный формирователь, формирователь импульсов записи и амплитудный дискриминатор, одни выходы и входы которых являются соответствующими выходами и входами блока сопряжения, другие входы амплитудного дискриминатора подключены соответственно к входу задания порога и ко второму управляющему входу блока сопряжения, а выход амплитудного дискриминатора является информационным выходом блока сопряжения, информационный вход адресного формирователя является адресным входом блока сопряжения, управля-ющий вход ,

s адресного формирователя является первым управляющим входом блока сопряжения и соединен с одним из входов формирователя импульсов записи, другой вход которого является входом записи блока сопряжения. Такое построение устройства позволяет

й без значительного усложнения устройства повысить его быстродействие и надежность .за счет совмещения операций записи, контроля и подбора информации путем подключения соответствующих блоков через четвертый и пятый мультиплексоры к полупроводниковому блоку постоянной памяти, тип которого может быть любым, поскольку он размещается в узле фиксации сменного блока сопряжения.

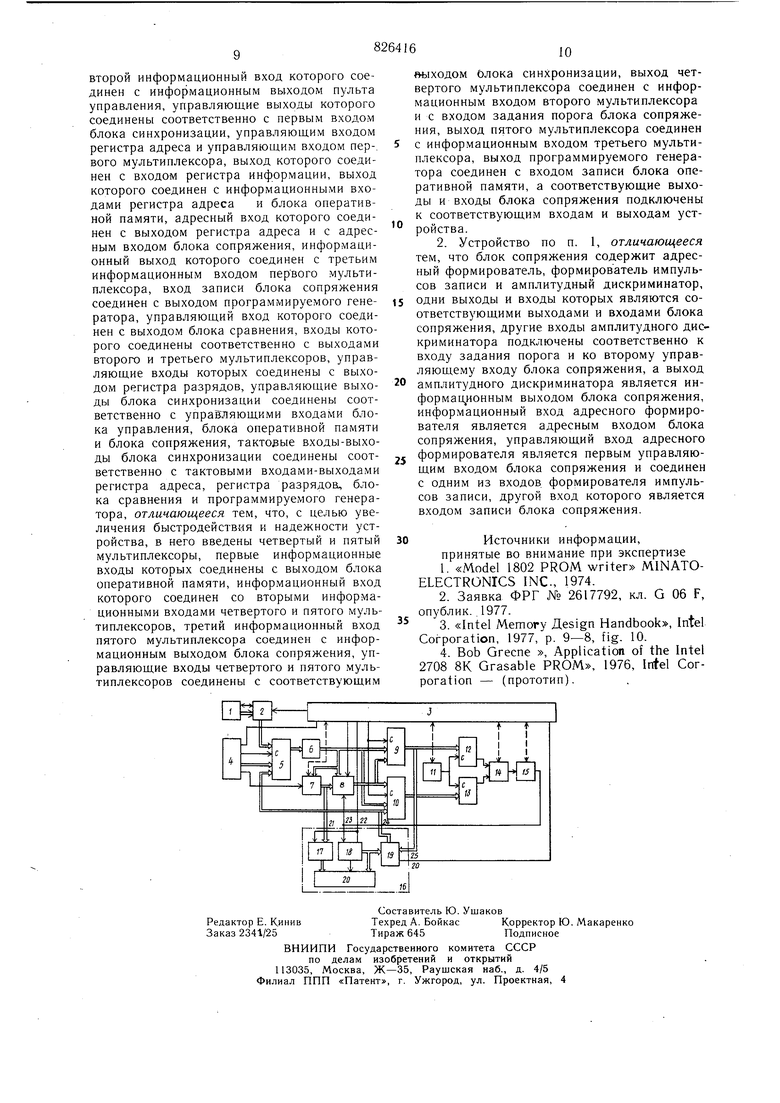

0 На чертеже представлена функциональная схема устройства.

Устройство содержит блок Г внешних . носителей, блок 2 управления, блоком влеш.них носителей, блок 3 синхронизации, пульт , 4 управления, первый мультиплексор 5, ре-: гистр 6 информации, регистр 7 адреса, блок 8

оперативной памяти (ОЗУ), четвертый 9 и пятый 10 мультиплексоры, регистр 11 разрядов, второй 12 и третий 13 мультиплексоры, блок 14 сравнения, программируемый

0 генератор 15 и блок 16 сопряжения, который в свою очередь состоит из адресного формирователя 17, формирователя 18 импульсов записи, амплитудного дискриминатора 19 н узла фиксации 20 положения блока постоянной памяти микросхемы ППЗУ.

5 Информационные шйнь показаны на чергеже двойными линиями, управляющие шины - одинарными, а тактовые шины - пунктирными.

В блоке сопряжения 16 основные входы и выходы обозначены цифрами; адресный вход 21,.первый управляющий вход 22, вход 23 записи,- информационный выход 24, вход 25 задания порога и второй управляющий вход 26. Соответствующие выходы и входы блока 16 сопряжения, идущие через узел фиксации 20 к ППЗУ, являются выходами и входами всего устройства.

Выполнение блока сопряжения 1б в виде конструктивно-законченного узла удобно и позволяет заменять эти блоки 16 при программировании различных типов блоков постоянной памяти, так как каждый тип требует своей временной диаграммы и электрических сигналов в соответствии с требованиями технических условий. Таким образом, электрическая, схема блока 16 для каждого типа будет разной, хотя функциональная схема остается прежней.

Устройство может выполнять операции входного контроля, при котором проверяется отсутствие дефектов в нез.апрограммнрованных микросхемах ППЗУ или информационное содержимое ранее запрограммированных микросхем ППЗУ; ввода информации, при котором исходная информация, . подлежащая записи в -микросхему ППЗУ, может вводиться в блок оперативной памяти 8 с перфоленты, смагнитной ленты, ЭВМ, эталонной микросхемы ППЗУ, устанавливаемой в узел фиксации 20, с распечатки или другого документа клавиатурой пульта управления 4; программирования - запись информации в микросхему ППЗУ; входного контроля, при котором проверяется информация микросхемы ППЗУ на соответствие исходной информации.

Кроме того, в устройстве предусмотрен ряд других режимов, в том числе самоконтроля, непрерывного воздействия импульсами записи на плохо программируемые микросхемы, анализа процесса программирования, подбора информации к дефектным микросхемам ППЗУ или подбора микросхем ППЗУ к требуемой информации, выключение алгоритма программирования, запись инфрр мации в. инверсном коде, нахождения нужного файла в рулоне перфоленты и т.д.

Устройство работает следующим образом..

С помощью пульта 4 управления выбираются операции, которые необходимо выполнить над микросхемой ППЗУ, выбирается источник исходной информации,- устанавливаются все регистры прибора в исходное состояние, в узел 20 фиксации устанавливается микросхема для контроля записи в нее информации, запускается программируемый генератор 15 и, если необходима операция входного контроля, то блок синхронизации 3 вырабатывает управляющие сигналы, по которым блок 14 сравнения и мультиплексоры 9 и 10 устанавливаются в режим входного контроля, при этом на адресные

входы микросхемы, установленной в узел 20, фиксации через адресный формирователь 17 и регистра 7 адреса подается код адреса проверяемого слова. В режиме входного контроля исходное состояние регистра 6 информации соответствует состоянию незапрограммирова«ной микросхемы. Информация из регистра 6 информации через мультиплексор 9 поступает на входы, мультиплексора 12 и на входы задания информации амплитудного дискриминатора 19, где сравнивается с информацией микросхемы ППЗУ, хранящейся в ней по данному адресу.

С выхода амплитудного дискриминатора 19 информация через мультиплексор 10 поступает на информационные входы мульти15 плексора 13. Мультиплексоры 12 и 13, управляемые регистром 11, выдают поочередно информацию соответствующих разрядов мультиплексоров 9 и 10 на входы блока сравнения 14. Если амплитудные значения сигналов с выходов проверяемой микросхемы ППЗУ отличаются от значений предусмотренных ТУ на незапрограммированную микросхему, то блок сравнения 14 выдает управляющий сигнал в блок синлронизации 3, по которому управляемый генератор 5 15 останавливается и индицируется адрес, информация микросхемы ППЗУ по этому адресу и сигнал брака входного контроля. Если амплитудные значения сигналов с выходов проверяемой микросхемы ППЗУ соответствуют значениям,предусмотрениым ТУ 0 на незапрограммированную микросхему, то блок сравнения 14 выдает сигнал на генератор 15, по которому последний, работ;ая в режиме контроля, выдает импульсы на блоксинхронизации 3 для управления ре: гистром разрядов 11 и регистром адреса 7. Проконтролировав последний разряд последнего слова, блок синхронизации 3 останавливает генератор 15 и индицируетконец работы прибора, если другие операции не были ранее выбраны на пульте управления 4. Если выбрана операция ввода и контроля информации с внешнего носителя, например с перфоленты, то блок управления внешним носителем 2 включает фотосчитывающее устройство блока внещних носителей I и после обработки кодов служебной инфор5 мации выдает информацию через мультиплексор 5 в регистр информации 6, вырабатывает сигнал пуска генератора 15 и останова фотосчитывающего устройства блока 2. С регистра 6 информация поступает на информационные входы блока оперативной па мяти 8 и через мультиплексор 9 на мультиплексор 12. Информация, хранимая блоком оперативной памяти 8 через мультиплексор 10 поступает на мультиплексор 13. Информация с мультиплексоров 12 и 13 поразряд-но сравнивается в блоке 14 сравнения и прн ее неравенстве по управляющему сигналу из блока сравнения 14, управляемый генератор 15 вырабатывает сигнал записи, по которому в блок 8 оперативной памяти записывается входная информация, поступающая с регистра 6 информации. После контроля последнего разряда вводимого слова, генератор 15 выдает сигнал, по которому блок 3 синхронизации устанавливает следующий адрес в регистре .7 адреса через блок 2 управления, включает фотосчитывающее устройство и останавливает генератор 15. Блок 1 внешних носителей считывает информацию с перфоленты через блок 2 и мультиплексор 5, вводит ее в регистр 6 информации. Блок 2 останавливает фотосчитывающее ycTpoffCTBO и,через блок 3 синхронизации запускает генератор 15. Далее процесс повторяется как описано выше, пока не будет закончен и проконтролирован ввод информации последнего слова. В случае ошибки при вводе информации блок 14 сравнения и блок 2 управления выдают в блок 3 синхронизаци сигналы сбоя, устройство останавливается, индицируется: адрес, вводимая и введенная информация и вид сбоя. После ввода информации устройство либо останавливается, либо переходит к выполнению следующей операции программирования. При программировании информация, считанная из блока 8 оперативной на.мяти через мультиплексор 9 поступает на мультиплексор 12, а информация, считанная из микросхемы ППЗУ, установленной в узел 20, через амплитудный дискриминатор 19 и мультиплексор 10 поступает на мультиплексор 13. Далее, как и при выполнении предыдущих операций, информация с мультиплексоров 12 и 13 поразрядно сравнивается блоком 14 сравнения и в случае несовпадения информации, при которой из микросхемы ППЗУ блок (20 считывается сигнал, соответствующий незапрограммированному биту, а из ОЗУ блок( сигнал, соответствующий запрограммированному биту, генератор 15 по управляющему сигналу с блока 14 сравнения выдает импульс записи, по которому формирователь 18 программирования формирует импульсы напряжения и тока с амплитудными и временными параметрами, соответствующими нормам ТУ на программируемую микросхему. После воздействия импульсами записи предусмотренным способом программирования, если соотношение сигналов с ОЗУ и с ППЗУ не изменилось, адресный формирователь 17 во время действия импульсов записи, если это необходимо, формирует адресные входные сигналы, соответствующие требованиям ТУ на программируемую микросхему. По окончании импульсов записи адресный формирователь 17 формирует стандартные логические сигналы, необходимые для считывания из микросхемы ППЗУ информации выбранного слова. Если по выбранному разряду из микросхемы ППЗУ (узел 20 считывается сигнал, соответствующий запрограммированной ячейке, а из ОЗУ(блок 8 считывается сигнал, соответствующий исходному сигналу незапрограммированной микросхемы, то блок 14 сравнения выдает сигнал останова и индицируется адрес, информация ОЗУ, информация микросхемы ППЗУ и сигнал невозможности программирования. .В случае совпадения информации, поступающей на входы блока 14 сравнения, генератор 15 выдает сигнал в блок 3 синхронизации, по которому к блоку 14 сравнения подключаются следующие разряды микросхемы ППЗУ (блок 20) и ОЗУ (блок 8) и т.д. После контроля и программирования последнего слова блок 3 синхронизации останавливает программу и индицирует сигнал окончания выполнения всех операций в том случае, если выбранные на пульте 4 управления операции выполнены. Если выбрана операция выходного контроля, т.е. контроля правильности программирования по установленным уровням дискриминации выходных напряжении микросхемы ППЗУ, то как и при выполнении операции программирования, информация из ОЗУ (блок 8) через мультиплексоры 9 и 12 поступает на один вход блока 14 сравнения, а информация, считываемая с микросхемы ППЗУ (блок 20), через мультиплексоры 10 и 13 на другой вход блока 14 сравнения. При выполнении операции выходного контроля устройство работает так же как и при программировании, за исключением случая, когда из ОЗУ (блок 8) считывается сигнал, соответствующий запрограммированному биту, а из микросхемы ППЗУ (блок 20) считывается сигнал, соответствующий незапрограммированному биту. В этом случае генератор 15 выдает сигнал брака, по которому блок синхронизации 3 останавливает программу и индицирует адрес, информацию ППЗУ и ОЗУ и причину останова. Если информационное содержимое ОЗУ и микросхемы ППЗУ совпадает по всем словам, то после контроля последнего разряда последнего слова программа останавливается и индицируется сигнал окончания выполнения всех операций. Таким образом, предлагаемое устройство позволяет увеличить быстродействие устройства в 2 раза и повысить надежность записи информации и всего устройства за счет совмещения операций без усложнения конструкций. Формула изобретения 1. Устройство для записи информации в полупроводниковые блоки постоянной памяти, содержащее блок управления, входывыходы которого являются входами-выходами устройства, информационный выход блока управления соединен с первым информационным входом первого мультиплексора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для записи информации в полупроводниковые блоки постоянной памяти | 1987 |

|

SU1444882A2 |

| Устройство для записи информации в полупроводниковые блоки памяти | 1978 |

|

SU765872A1 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММИРОВАНИЯ МИКРОСХЕМ ПОСТОЯННОЙ ПАМЯТИ | 1989 |

|

RU2047920C1 |

| ПРОГРАММАТОР | 1991 |

|

RU2078381C1 |

| Устройство для программирования микросхем постоянной памяти | 1982 |

|

SU1134964A1 |

| Устройство для программирования постоянных запоминающих устройств | 1989 |

|

SU1635207A1 |

| Устройство для программирования микросхем постоянной памяти | 1985 |

|

SU1285535A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММИРОВАНИЯ МИКРОСХЕМ ПОСТОЯННОЙ ПАМЯТИ | 1990 |

|

RU2047918C1 |

| Устройство для записи и контроля программируемой постоянной памяти | 1986 |

|

SU1376121A2 |

Авторы

Даты

1981-04-30—Публикация

1979-06-01—Подача