контроля соединены с соответствующими входами усилителя-передатчика, выходы которого соединены с входами первой группы блока синхронизации и входами усилителя-приемника, управ ляющий вход усилителя-передатчика 1 134964 соединен с управляющим выходом блока синхронизации, входы-выходы первой, второй и третьей групп которого являются управляющими входами-выходами первой, второй и третьей групп устройства соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программатор | 1986 |

|

SU1439677A1 |

| Устройство для программирования микросхем памяти | 1981 |

|

SU1005183A1 |

| Устройство для записи и контроля программируемой постоянной памяти | 1985 |

|

SU1297118A1 |

| Устройство для программирования микросхем постоянной памяти | 1987 |

|

SU1425779A1 |

| Программатор | 1987 |

|

SU1541669A1 |

| Устройство для записи и контроля программируемой постоянной памяти | 1986 |

|

SU1376121A2 |

| Устройство для программирования блоков постоянной памяти | 1986 |

|

SU1437922A1 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Устройство для программирования микросхем памяти | 1986 |

|

SU1381592A1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММИРОВАНИЯ МИКРОСХЕМ ПОСТОЯННОЙ ПАМЯТИ | 1989 |

|

RU2047920C1 |

УСТРОЙСТВО ДЛЯ ПРОГРАММИ- РОВАНИЯ МИКРОСХЕМ ПОСТОЯННОЙ ПАМЯТИ, содержащее первый, второй и третий формирователи импульсов, входы первых групп которых соединены с информационными шинами, входы вторых групп соединены с управляющими шинами, выходы первого, второго и третьего формирователей импульсов соединены соответственно с входами первого, второго и третьего усилителей мощности, выходы первого и второго усилителей мощности являются соответственно первым и вторым управляющими выходами устройства, выход третьего усилителя мощности соединен с входом питания блока ключей, выходы которого соединены с входами первой группы блока контроля и являются числовыми выходами устройства, входы второй группы блока контроля соединены с выходат ми первого регистра и входами первой группы блока ключей, входы третьей группы блока контроля соединены с источником опорных напряжений, информационные входы первого, второго и третьего регистров соединены с информационными шинами, а 5шравляющие входы - с управляющими шинами, выходы второго регистра соединены с входами второй группы блока ключей, выходы третьего регистра являются адресными выходами устройства, отличающееся тем, что, с целью расширения области применения устройства за счет увеличения класса программируемых микросхем, оно содержит первый, второй и третий формирователи фронтов импульсов, четвертый и пятый регистры, блок сравнения, блок синхронизации, усилитель-передатчик, усили(Л тель-приемник и цифро-аналогов преобразователь, информационные вхо ды четвертого и пятого регистров и § выходы усилителя-приемника соединены с информационньо4И шинами, выходы четвертого регистра соединены с информационньши и управляющими входами формирователей фронтов импульсо сов, выходы которых соединены с вхо4i)k дами соответствующих усилителей мощ;о а ности, выходы третьего формирователя импульсов соединены с входами 4 третьей группы блока ключей, управляющие входы четвертого и пятого регистров и выходы блока синхронизации соединены с управляющими шинами, выходы пятого регистра соединены с входами цифро-аналогового пре образователя, выход которого соединен с п рвым входом блока сравнения, BToposi. третий и четвертый входы которого соединены с выходами соответствующих усилителей мощности, выходы блока сравнения и выходы блока

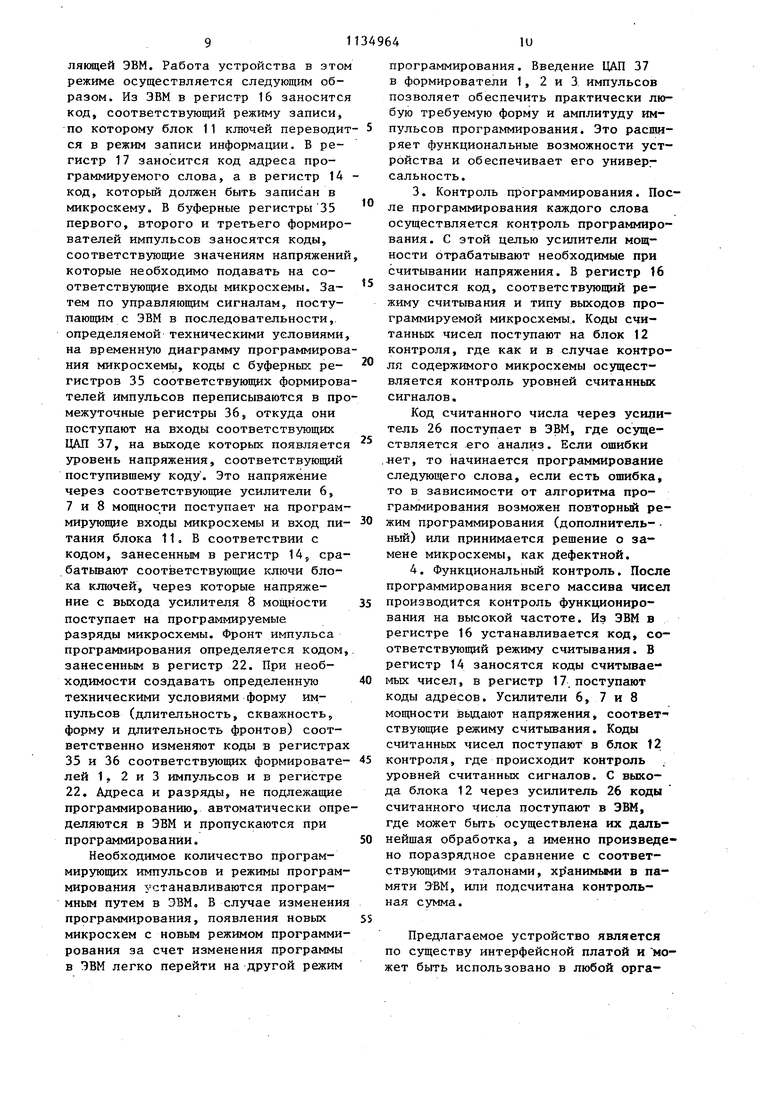

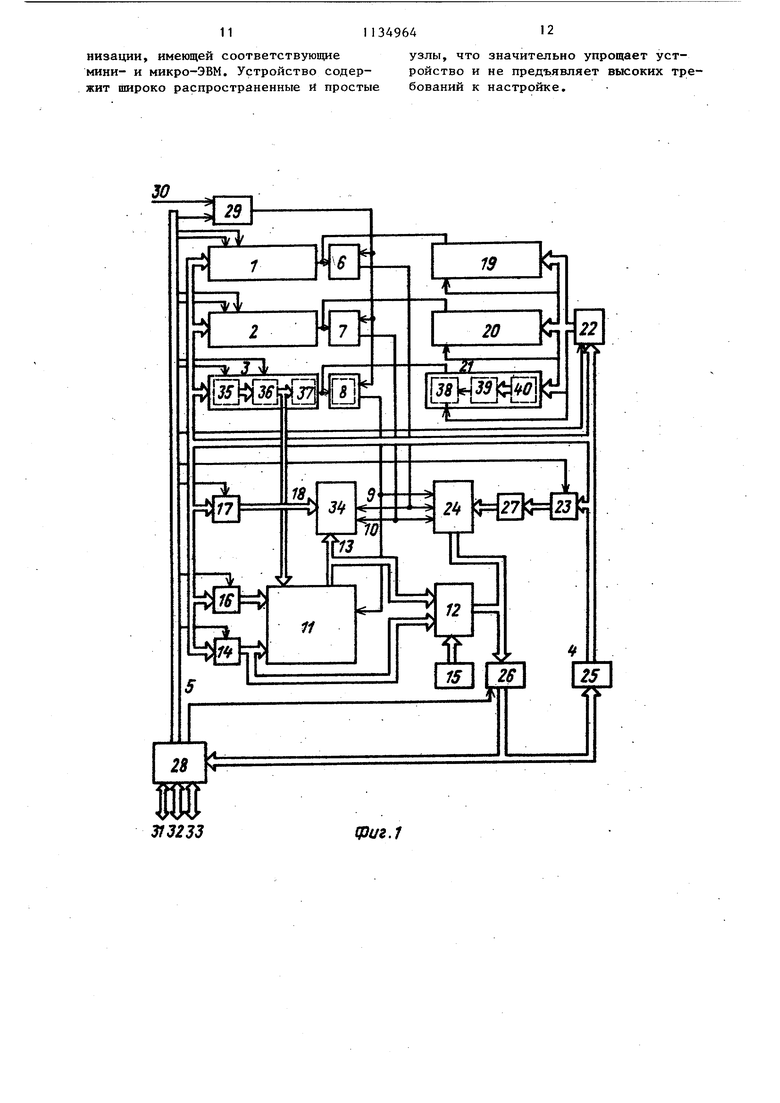

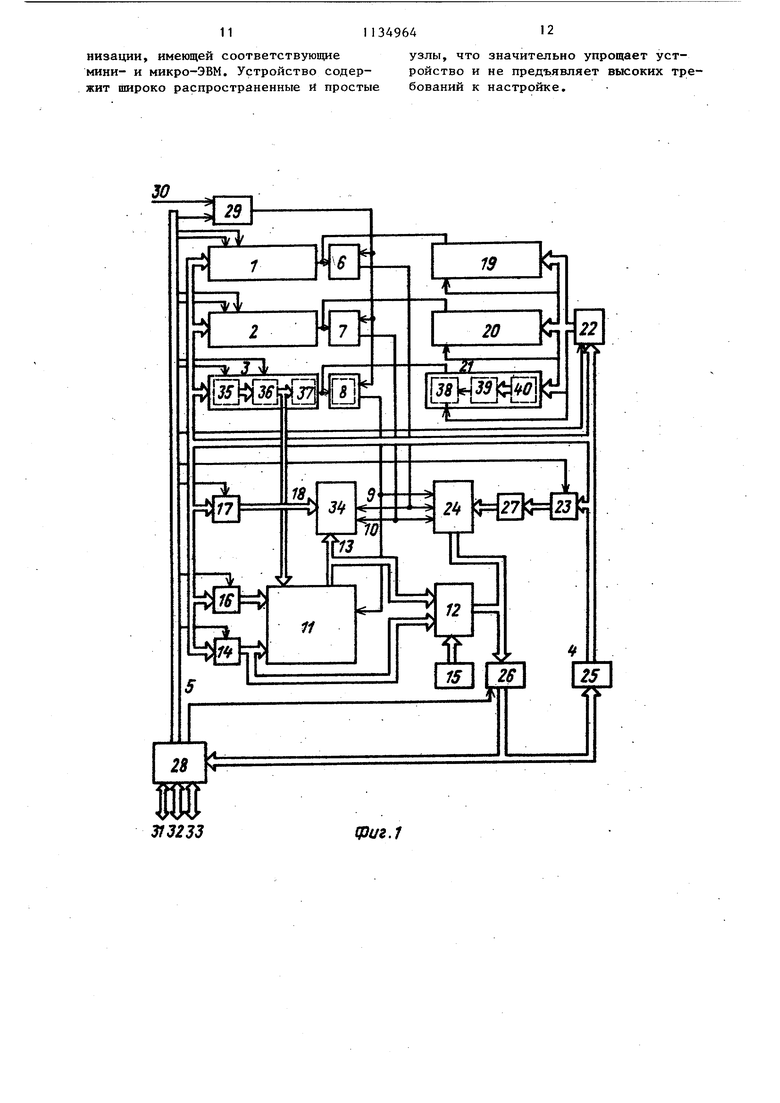

Изобретение относится к вычислительной технике, а именно к управляемым ЭВМ устройствам программиров ния, и может быть использовано при программировании микросхем постоян ной памяти. Известно устройство для программ рования микросхем постоянной памяти, представляющее собой программирующую плату, соединяемую через буферные регистры с контроллером, содержащее блок управления, блок пита ния, коммутатор питания, вспомогательные схемы tj. Данное устройство отличается про стотой, но характеризуется низкой производительностью, невозможностью вырабатьгеать последовательности импульсов различной формы, что необхо димо для повышения Достоверности за писи при переходе с программирования микросхем одного типа на другие Наиболее близким по технической сущности и схемному решению к предлагаемому является устройство.для программирования микросхем постоянной памяти, состоящее из программного устройства управления, блока сопряжения с внешними устройствами для ввода-вывода информации, программирующей платы 2J . Однако известное устройство характеризуется излишней сложностью, которая связана с наличием автономных программного устройства управле ния и блока сопряжения. В большинств случаев эти блоки могут быть заменены на серийно вьтускаемые мини-,и микро-ЭВМ, например серии Электроника, имеющие периферийное оборудование и надлезкащее математическое обеспечение, В подобных случаях удобно иметь лишь оконечное устройство для программирования микросхем - программирующую плату, содержащую необходимые аппаратные средства для формирования импульсов программирования. Однако в известном устройстве программирующая плата не только конструктивно, но и функционально не может быть вьделена так, чтобы ее легко можно быпо бы подключить к ЭВМ, Кроме .того, отсутствие в нем возможностей изменения длительности фронтов программируюпщх импульсов, которые различны для различных типов программируемых микросхем, значительно снижает область применения такого устройства. Цель изобретения - расширение области применения устройства за счет у величения класса программируемых микросхем. Поставленная цель достигается тем, что устройство для программирования микросхем постоянной памяти, содержащее первый, второй и третий формирователи импульсов, входы, первых групп которых соединены с информационными шинами, входы вторых групп соединены с управляющими шинами, выходы первого, второго и третьего формирователей импульсов соединены соответственно с входами первого, второго и третьего усилителей мощности, выходы первого и второго усилителей мощности являются соответственно первым и вторым управляющими вькодами устройства, выход третьего усилителя мощности соединен с входом питания блока ключей, выходы которого соединены с входами первой группы блока контроля и являются числовыми ВЫХО-. дами устройства, входы второй группы блока контроля соединены с выходами первого регистра и. входами первой группы блока ключей, входы третьей группы блока контроля соединены с не точником опорных напряжений информационные входы первого, второго и третьего регистров соединены с информационными планами, а управляющие входы - с управляющими шинами, выходы второго регистра соединены с входами второй группы блока ключей,выходы третьего регистра являются адресными выходами устройства, содержит первый, второй и третий формирователи фронтов импульсов, четвертый и пятый регистры, блок сравн ния, блок синхронизации, усилительпередатчик, усилитель-приемник и ци ро-аналоговый преобразователь, инфо мационные входы четвертого и пятого регистров и выходы усилителя-приемника соединены с информационными шинами, выходы четвертого регистра соединены с информационными и управ лякицими- входами формирователей фрон тов импульсов, выходы которых соеди нены с входами соответствующмх усилителей мощности, выходы третьего формирователя импульсов соединены с входами третьей группы блока ключей, управлякицие входы четвертого и пятого регистров и выходы блока синхронизации соединены с управляющими шинами, выходы пятого регистра соединены с входами цифро-аналогово го преобразователя, выход которого соединен с первым входом блока срав нения, второй, третий и четвертый входы которого соединены с выходами соответствующих усилителей мощности, выходы блока сравнения и выходы блока контроля соединены с соответствующим входами усилителя-передат чика, выходы которого соединены с входами первой группы блока синхронизации и входами усилителя-приемника, управляющий вход усилителя-пе редатчика соединен с управля ощим выходон блока синхронизации, входывыходы первой, второй и третьей гру которого являются управляющими входами-выходами первой, второй и третьей групп устройства соответственно. На фиг.1 представлена блок-схема предлагаемого устройстваJ на фиг.2функциональная схема блока синхрони зации при подкдяочении устройства к СМ AJ на фиг.З - функциональная схема блока синхронизации, которая может быть использована при к микро-ЭВМ Электрониподключениика-60. Устройство (фиг,1) содержит первый 1, второй 2 и третий 3 формирователи импульсов, информационные шины 4, управляющие шины 5, первый 6, второй 7 и третий 8 усилители мощности, первый 9 и второй 10 управляющие выходы устройства, блок 11 ключей, блок 12 контроля, числовые выходы 13 устройства, первый регистр 14, источник 15 опорных напряжений, второй 16 и третий 17 регистры, адресные выходы 18 устройства, первый 19, второй 20 и третий 21 формирова . тели фронтов импульсов,.четвертый 22 и пятый 23 регистры, блок 24 сравнения, усилитель-приемник 25 и передатчик 26, цифро-аналоговый преобразователь 27, блок 28 синхронизации, преобразователь 29 напряжения,,вьгоод 30 питания устройства, управляющие , входы-выходы первой 31, второй 32 и третьей 33 групп устройства, разъем 34 для установки программируемых микросхем, буферный регистр 35, промежуточный регистр 36, цифро-аналоговый преобразователь 37, блок 38 ключей, блок 39 конденсаторов, блок 40 коммутаторов. Блок 28 (фиг.2) содержит дешифратор 41, инверторы 42, 43 и 44,блок 45 элементов И, злемент И 46, злемент 47 задержки и усилитель 48. Шины 31, 32 и 33 подключаются к шинам данных, адреса и управления ЭВМ соответственно. Блок работает следующим образом. В режиме записи по шине 33 управения поступают сигналы и и запрещают работу злемента И 46 и разрешают работу злементов И блока 45. Адрес соответствующего регистра устройства поступает по шине 32 и с помощью дешифратора 41 преобразуется в унитарный код, который поступает на блок И 45 элементов. После оступления сигналй СхЗ обеспечивается вьщача соответствующего управяющего сигнала в шину 5 управления. тот же сигнал после прохождения ерез злемент 47 задержки и шинный ормирователь 48 поступает на вход отовнсч ги ЭВМ СхИ. Данные по шине 1 поступают через усилитель-приемик 25 на входы регистров и запиываются в тот регистр, который строируется сигналом с шины 5. В режиме считывания по шине упра ления поступают сигналы , которые закрывают блок 45 элементов И и разрешают работу элемента И 46о Сигнал с.этого элемента откры вает усилитель-передатчик 26, и информация поступает по шине 31 в ЭВ Функциональная схема блока синхронизации (фиг„3) может быть испол зована при подключении к микро-ЭВМ Электроника-60 « Блок 28 содержит схему 49 выбора внешнего устройства элемент И 50,, триггер 51, регистр 5 дешифратор 53, элементы И 54, 55, 56 и 57, дешифратор 58, элемент ИЛИ 59s элемент И 60, элемент 61 задержки, усилитель 62. Микро-ЭВМ имеет совмещеннуто муль типлексную шину адреса и данных 31 и шины 33 управления По ишне 33 управления поступают сигналы ВУН, СИАН, СИПН, БАЙТ, ВВОД Н, ВЫВОД Н, СБРОС Н, которые позволяют организо вать направление передачи и синхронизацию пересыпок в системе. Блок работает следующим образом. Операция обмена с устройством программирования начинается с въщ& чи адреса по шине 31 и сигнала ВУН. Старшие разряды кода адреса поступают на схему 49, где фиксируются и через элемент И 50 записываются фронтом сигнала СИАН, Одковремекно младшие разряды адреса фиксируются тем же сигналом в регистре 52. Таким образом, в триггере 51 фиксируется признак обращения к устройству пpoгpajs{миpoвaния, а в регистре 52 адрес регистра, к которому происходит обращение. Младшие разряды адреса поступают на дешифраторы 53 и 58, управление которыми осуществляется с помощью элементов И 54 57. Это позволяет обеспечить побайт ный или послойный обмен данными в зависимости от сигнала БАЙТ и младшего разряда адреса. Разрешение работы элементов И 56 и 57, а следовательно и дешифраторов 53 и 58 осу ществляется сигналом, поступающим с триггера 51. Выходы дешифратора образуют шину 5 управления устройства программирования и сигнал счит вания, идущий к блоку 26. Организация асинхронного обмена между микро ЭВМ и устройством программирования осуществляется сигналами ВЫВОД Н, ВВОД И, и СИПН посредством элементов ИЛИ 59, И 60, элемента 61 задержки и усилителя 62, как и при использовании ЭВМ СМ-4. Установка в исходное состояние блока сопряжения осуществляется сигналом СБРОС Н, путем обнуления триггера 51. Устройство работает следующим образом. Подготовительный режим. В этом режиме выбранную миниили микро-ЭВМ через разъемные соединения соединяют с устройством программирования микросхем. При этом информационные, адресные и управляющие шины выбранной мини- или микроЭВМ соединяют соответственно с управляюнщми входами первой 31, второй 32; третьей 33 групп устройства про граммирования. На вход 30 питания подают необходимое напряжение питания. После того как Устройство программирования состыковано с ЭВМ и поданы питаюш 1е напряжения можно переходить к следующему режиму. Режим настройки. В этом режиме осуществляется калибровка амплитуд програ11мирующих и fflyльcoв, вырабатьшаемых формирователями 1, 2 и 3 импульсов, и устанавливаются фронты программирующих импульсов в соответствии с требова- . ниями технических условий на программируемый тип микросхемы. Калибровка амплитуд программирующих га пульсов осуществляется следующим образом. В схему введен прецизионный цифроаналоговый преобразователь (ЦАП) 27 (например, 572 ПА 1) и блок 24 сравнения. Поскольку для каждого типа программируемых микросхем известны требуемые параметры импульсов, то в регистр 23 записывается двоичный код, соответствующий величине требуемого напряжения на выходе. На выходе ЦАП 27 устанавливается с заданной точностью требуемое напряжение. Затем последовательно подают возрас- или убывающие коды в буферный 35 и далее в промежуточный 36 регистры формирователей 1, 2 и 3 импульсов. Эти коды поступают на соответствующий ЦАП формирователей импульсов. На его выходе будет изменяться напряжение. Выходные напряжения с соответствующих ЦАП через усилители 6 (7,8) мощности поступают на входы блока 24 сравнения, которьй определяет момент сравнения напряжеНИИ с выхода формирователя импульсов с точным значением, поступающим с ЦАП 27. Код, соответствующий требуемому напряжению на выходе формирователя 6 (7, 8) импульсов, записывается в память поправок, которая выделяется в.памяти ЭВМ. Таким образом, для всех требуемых значений выходного напряжения (в тех случаях, когда оно ступенчатое) и для всех трех каналов последовательно определяют коды, которые в процессе работы поступают в регистры 35 формирователей 1, 2 и 3 импульсов. Такая организация позволяет упростить ЦАП 37 формирователей импульсов, добиться его высокого быстродействия и практически исключить его настройку в процессе изготовления.

Установка необходимых длительноетей фронтов программирующих импульсов заключается в занесении в регист 22 кода, который определяет-длительность фронта программирующих импульсов для выбранного типа микросхемы. Код с регистра 22 обеспечивает подключение нужных емкостных блоков 39 через коммутаторы 40 и ключи 38 по входам усилителей 6 (7,8) мощности что приводит к увеличению длительности фронтов сигналов, снимаемых с усилителей 6, 7 и 8.

Основной режим.

Работа в этом режиме состоит из следующих этапов, которые начинаются после занесения в ручном или автоматическом режиме с внешних устройст информации, подлежащей программированию в память ЭВМ.

Контроль содержимого микросхемы ос тцествляется следующим образом.

По кодам, поступающим на управляющие входы 31, 32 и 33 устройства от ЭВМ, на выходах формирователей импул сов устанавливаются напряжения, соответствующие режиму считывания информации из микросхемы. В регистр 14 заносится код, соответствующий исходному содержимому микросхемы, в регистр 16 - код, соответствукнций режиму считывания информации и типу выхода программируемой микросхемы (открытый коллектор или три состояния) . По кодам, поступающим с регистров 14 и 16, блок 11 ключей переводится в режим считывания и подключает через соответствующие ключи необ|Ходимые нагрузочные резисторы к выходам микросхем. В регистр 17 адреса последовательно заносятся коды адресов считываемых слов. Сигналы, .считываемые из микросхемы, поступают на входы первой группы блока 12 контроля, где происходит сравнение уровней считываемых сигналов с опорными, поступающими от источника 15 опорных напряжений. Величина опорного напряжения низкая (соответствующая стандартному значению уровня Лог. О) или высокая (соответствующая стандартному значению уровня Лог. 1) задается соответствующими разрядами регистра 14, которые поступают на входы второй группы блока 12 контроля. В блоке 12 происходи сравнение уровней считанных сигналов с опорными. На выходе блока 12 появляется код, ощибочные разряды которого принимают инверсное значение по отношению к коду, записываемому в регистр 14. Проверенные коды считываемых чисел через усилитель 26 поступают вЭВМ, где осуществляется их дальнейшая обработка в соответствии с описанным алгоритмом. После контроля микросхемы начинается процесс программирования.

Необходимое количество программирующих импульсов и режимы программирования устанавливаются программным путем в ЭВМ, В случае изменения программирования, появления новых микросхем с новым режимом программирования за счет изменения программы в ЭВМ легко перейти на другой режим

программирования. Введение ЦАП 37 в формирователи 1, 2 и 3. импульсов позволяет обеспечить практически любую требуемую форму и амплитуду импульсов программирования. Это расширяет функциональные возможности устройства и обеспечивает его универгсальность.

Код считанного числа через усилитель 26 поступает в ЭВМ, где осуществляется его анализ. Если ошибки .«ет, то начинается программирование следзпощего слова, если есть ошибка, то в зависимости от алгоритма программирования возможен повторный режим программирования (дополнитель- ный) или принимается решение о замене микросхемы, как дефектной.

Предлагаемое устройство является по существу интерфейсной платой и может быть использовано в любой организации, имеющей соответствующие мини- и микро-ЭВМ. Устройство содержит пшроко распространенные И простые узлы, что значительно упрощает устройство и не предъявляет высоких требований к настройке.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 4156926, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для программирования микросхем памяти | 1981 |

|

SU1005183A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-01-15—Публикация

1982-05-26—Подача