Изобретение относится к автоматике и вычислительной технике, в частности к устройствам записи двоичной информации в программируемые микросхемы постоянной памяти и логические матрицы, и может найти применение в радиотехнике и телеметрии.

Цель изобретения - повышение области применения устройства за счет увеличения класса программируемых микросхем.

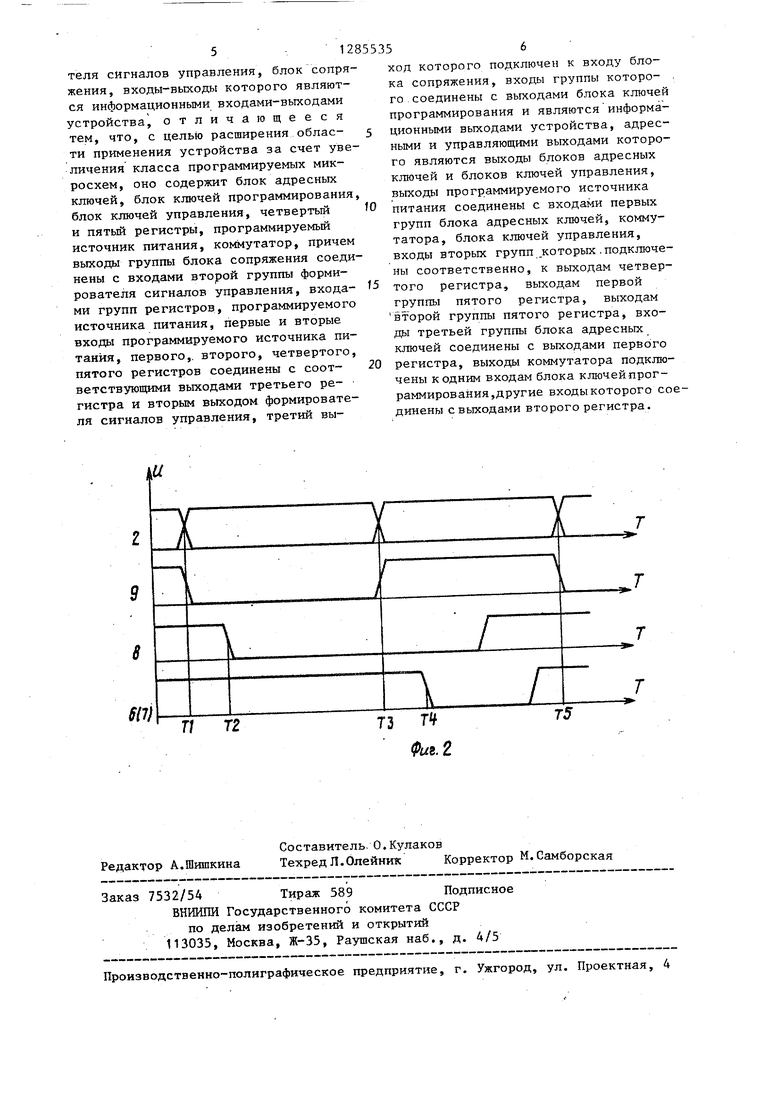

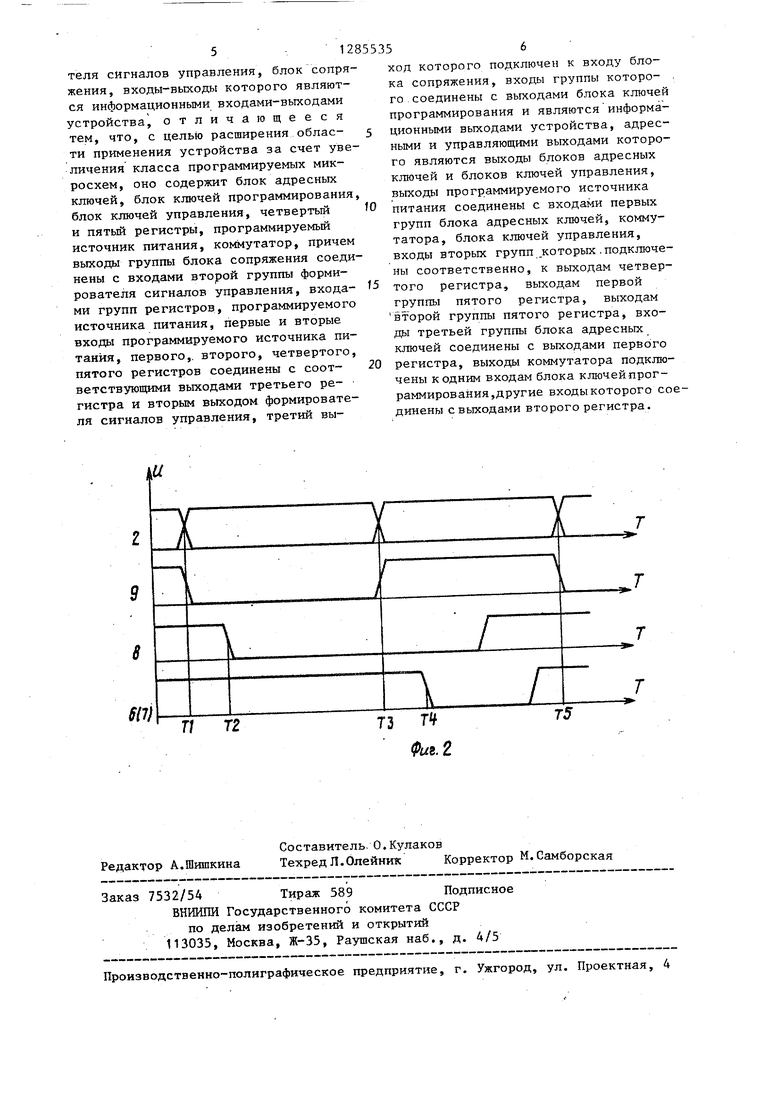

На фиг. 1 изображена функциональная схема устройства для программирования; на фиг. 2 - временные диаграммы сигналов на входах устройства в течение одного цикла управления (все сигналы имеют активный низкий уровень).

Устройство для программирования содержит блок 1 сопряжения , информационные входы-выходы 2, группу входов 3 блока сопряжения, формирователь 4 сигналов управления, состоящий из согласующего четырехканаль- ного приемника 5 сигналов, входы 6-9 которого являются управляющими входами устройства, селектора-дешифратора 10, регистра 11, блока схем 12 совпадения, выходы 13-15 формирователя сигналов управления, третий регистр 16, программируемый источник 17 питания с выходами 18, четвертый 19, первый 20, пятый 21 и второй 22 регистры, коммутатор 23, блок 24 адресных ключей, блок 25 ключей упраления, блок 26 ключей программироваНИН, выходы 27-29.

Управление работой устройства для программирования осуществляется с помощью устройства (не показано), вырабатывающего и читающего 17-разрядный двоичный код и четыре импульсных управляющих сигнала. Все сигналы долны быть синхронизированы между собой В частности, таким управляющим устройством может служить микро-ЭВМ, по отношению к которой и рассматривается работа устройства для программирования. В этом случае в качест не сигнала синхронизации используются сигналы с вькодов схем 12 совпадения, которые через схему ИЛИ вводятся в ЭВМ (не показано).

Устройство для программирования работает следующим образом.

На вход 2 блока 1 информации в момент времени TJ (фиг. 2) поступает

10

15

20

25

30

35

40

45

50

55

из устройства управлвЕШя 16-разрядный двоичный кед, старший байт которого с выхода приемопередатчика поступает на вход сел12ктора-де111ифратора 10 и содержит код признака обращения к данному устройству, а младший байт поступает на вход регистра стробирова- ния и содержит код выбора регистра, в который в дальнейшем должна быть записана информация.

Одновременно на вход 9 приемника 5 импульсных сигналов поступает сигнал обращения к данному устройству, который затем подается на вход селектора-дешифратора 10. При наличии этого сигнала и совпадении кода признака обращения с требуемым для данного устройства на выходе селектора-дешифратора 10 вырабатывается сигнал, поступающий на информационный вход регистра 11.

В момент времени Т2 на вход 8 приемника 5 импульсных сигналов при- , ходит сигнал записи адресной части цикла управления. Отрицательным фрон;

ТОМ этого сигнала производится запись в регистр 11 состояния выхода селектора-дешифратора 10, в результате чего с выхода регистра 11 на входы схем 12 совпадения поступает сигнал разрешения формирования управляющих сигналов на выходах 13 и 14 формирователя 4, В этот же момент сиг- налом с выхода 15 формирователя 4 сигналов управления производится запись младшего байта в регистр 16, с выходов которого вьщаются сигналы разрешения записи в один или два регистра 19 и 22 и источник 17.

В момент времени ТЗ на шины 2 блока 1 приходит информация, подлежащая записи в упомянутые регистры, а в момент времени Т4 на вход 6 приемника 5 подается сигнал записи этой информации, который через одну из схем 12 совпадения поступает на выход 14 формирователя 4. Этот сигнал производит запись информации в соответствующие регистры. В момент времени Т5 заканчивается один цикл управления. К этому моменту снимаются все управляющие сигналы, а на информационных выводах 2 появляется информация следующего цикла.

Таким образом, цикл управления .состоит из двух частей: адресной (Т1 - ТЗ), во время которой производится подготовка записи информа312

ции, н числовой (ТЗ - Т5), ког да производится запись информации в регистры. При этом в регистры 21 и 22 запись может производиться как раздельно за два цикла управления с задержкой (если необходимо) между циклами, так и одновременно за один цикл управления: в регистр 21 - старший байт, а регистр 22 - младший.

Контроль содержимого МС памяти производится за два цикла управления За первый цикл производится запись адреса контролируемого слова в регистр 20 адреса, а за второй цикл производится считывание этого слова. При этом вместо сигнала 6 в момент Т4 на вход устройства поступает сигнал 7 (фиг. 1), который через вторую схему 12 совпадения поступает на выход 13 формирователя 4 и управляет прохождением информации от входов 3 .на выводы 2 блока 1 сопряжения.

Цикл программирования МС памяти состоит из операций предварительного (входного) контроля, записи информа- ции в ячейки памяти и выходного контроля результатов записи. В начале цикла в регистр источника 17 заносится код, устанавливающий на выходах 18 блока набор высокостабильных нап- ряжений, необходимых для подачи на вьгооды МС памяти при контроле и записи информации. Во втором цикле управления в регистр 19 заносится код выбора напряжения, которое в дальнейшем подается на адресные входы (например, для ПЗУ 5В, для ПЛМ 5 и 10В

В третьем цикле управления с помощью регистра 20 и блока 24 ключей адреса устанавливается адрес контре- лируемой ячейки. Затем с помощью регистра 21 и блока 25 ключей на выходах 29 устанавливается электрический режим контроля. В следующем цикле управления производится считьша- ние информации из МС памяти по установленному адресу. Затем производится поочередная установка всех адресов МС памяти и считьшание информации по каждому адресу. Результаты входного контроля вьшодятся, например, на видеотерминал и по ним принимается решение о дальнейшем использовании МС памяти.

Операция записи информации начинается также с последовательной уста- нойки адреса ячейки на выводах. 28 и электрического режима питания на

j

-5 0

О 5

0 О

5

выводах 24 с гюмощью соответствующих регистров и ключей аналогично операции контроля. Если в соответствии с тербованиями руководства по программированию необходимо устанавливать режим на одном из .вьтаодол.. - задержкой относительно другого, то запись соответствующих кодов в регистр 21 производится в разных циклах управления. Одновременно этот же регистр 21 управляет ком гутатором 23, который переключает необходимую пару напряжений на входы блока 26 ключей программирования (например, для ПЗУ одно из напряжений равно нулю, а для ПЛМ 556РТ1 требуется четыре пары: Ои5, Ои 17, 5и 10, 5и 17 В).- И, наконец, в очередном цикле управления регистр 22 открьшает один или несколько разрядных ключей программирования, устанавливая на выходах 27 необходимый уровень напряжения. Снятие режима записи производится в последовательности, определенной руководством по программированию, путем записи в соответствующие разряды регистров обратного логического уровня. Таким образом, последовательно занося определенный код в соответствующие регистры, можно сформировать импульсы программи- . рования любой длительности и скважности и с любым времменым соотношением между ними в соответствии с требованиями руководства по программированию.

Контроль МС после записи информации (выходной контроль) осуществляется аналогично входному контролю с той разницей, что содержимое МС памяти проверяется при крайних допустимых значениях напряжений, обеспечивающих режим контроля, для чего в регистр источника 17 предварительно заносится соответствующий код. Устройство позволяет производить конт-- роль на любом этапе записи информации.

Формула изобретения

Устройство для программирования микросхем постоянной памяти, содержащее формирователь сигналов управления, входы первой группы которого являются управлякяцими входами устройства, первый регистр, второй регистр, третий регистр, вход которого подключен к первому выходу формирователя сигналов управления, блок сопряжения, входы-выходы которого являются информационными входами-выходами устройства, отличающееся тем, что, с целью расширения области применения устройства за счет увеличения класса программируемых микросхем, оно содержит блок адресных ключей, блок ключей программирования блок ключей управления, четвертьш и пятый регистры, программируемый источник питания, коммутатор, причем выходы группы блока сопряжения соединены с входами второй группы формирователя сигналов управления, входами групп регистров, программируемого источника питания, первые и вторые входы программируемого источника питания, первого,, второго, четвертого, пятого регистров соединены с соответствующими выходами третьего регистра и вторым выходом формирователя сигналов управления, третий выт

П Г2

Составитель. О.Кулаков Редактор А.Шишкина Техред Л.Олейник Корректор М.Самборская

Заказ 7532/54 Тираж 589 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

5

0

ход которого подключен к входу блока сопряжения, входы группы которо- , го соединены с выходами блока ключей программирования и являются информационными выходами устройства, адресными и управляющими выходами которого являются выходы блоков адресных ключей и блоков ключей управления, выходы программируемого источника питания соединены с входами первых групп блока адресных ключей, коммутатора, блока ключей управления, входы вторых групп .которых.подключены соответственно, к выходам четвертого регистра, выходам первой группы пятого регистра, выходам второй группы пятого регистра, вхо- Pfei третьей группы блока адресных ключей соединены с выходами первого регистра, выходы коммутатора подключены к одним входам блока ключей программирования,другие входы которого соединены с выходами второго регистра.

ТЗ Т Фм.2

75

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПРОГРАММИРОВАНИЯ МИКРОСХЕМ ПОСТОЯННОЙ ПАМЯТИ | 1989 |

|

RU2047920C1 |

| УСТРОЙСТВО ДЛЯ ПРОГРАММИРОВАНИЯ МИКРОСХЕМ ПОСТОЯННОЙ ПАМЯТИ | 1990 |

|

RU2047918C1 |

| Устройство для контроля записи информации в программируемые блоки памяти | 1983 |

|

SU1104589A1 |

| Устройство для записи и контроля программируемой постоянной памяти | 1985 |

|

SU1297118A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для программирования постоянных запоминающих устройств | 1989 |

|

SU1635207A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1993 |

|

RU2079876C1 |

| Устройство для записи и контроля программируемой постоянной памяти | 1986 |

|

SU1376121A2 |

| СИСТЕМА ДЛЯ ОБРАБОТКИ КОМПОНЕНТ ПРОГРАММ И СХЕМА УПРАВЛЕНИЯ ПАМЯТЬЮ ДЛЯ ТРАНСПОРТНОГО ПРОЦЕССОРА | 1995 |

|

RU2145728C1 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

Изобретение относится к вычислительной технике и автоматике, в частности к устройствам записи двоичной информации в программируемые микросхемы постоянной памяти, и может найти применение в радиотехнике и телеметрии. Целью изобретения является расширение области применения устройства за счет увеличения класса программируемых микросхем памяти. Устройство содержит формирователь 4 сигналов управления, блок 1 сопряжения, регистры 16, 19,- 20, 21, 22, программируемый источник питания 17, блок-24 адресных ключей,блок 25 ключей управления, блок 26 ключей программирования, коммутатор 23. Расширение области применения устройства осуществляется за счет возможности пррграммирования логических матриц. 2 ил. i W ю 00 ел ел 00 ел

| Устройство для программирования микросхем постоянной памяти | 1982 |

|

SU1134964A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для программирования микросхем памяти | 1981 |

|

SU1005183A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1987-01-23—Публикация

1985-04-16—Подача