к выходам которого подключены входы сумматора, введены счетный триггер, формирователь последовательности кратных частот и регистр памяти, управляющие входы которого подключены к выходам формирователя и отводам линии задержки, вход которой соединен с выходом счетного триггера, вход счетного триггера подключен к выходу генератора эталонной частоты и к первому входу формирователя последовательности кратиых частот, второй вход которого соедииен с одним из отводов линии задержки, выходы регистра иодключены к входам кодопреобразователя, а стробирующий вход регистра памяти соединен со входом записи сумматора, прн этом формирователь носледовательиости кратных частот выполнен в виде счетчика в рефлексном коде, содержащего два элемента ИЛИ, двухразрядный кольцевой счетчик и синхронный счетчик, счетные входы которых объединены, инверсный выход первого и прямой выход второго разрядов кольцевого счетчика подключены через первый элемент ИЛР1 к первому унравляюн;ему входу сннхронного счетчика, второй управляющий вход которого через второй элсмеит Р1ЛИ соединен с нрямым выходом первого н инверсным выходом второго разрядов кольцевого счетчика.

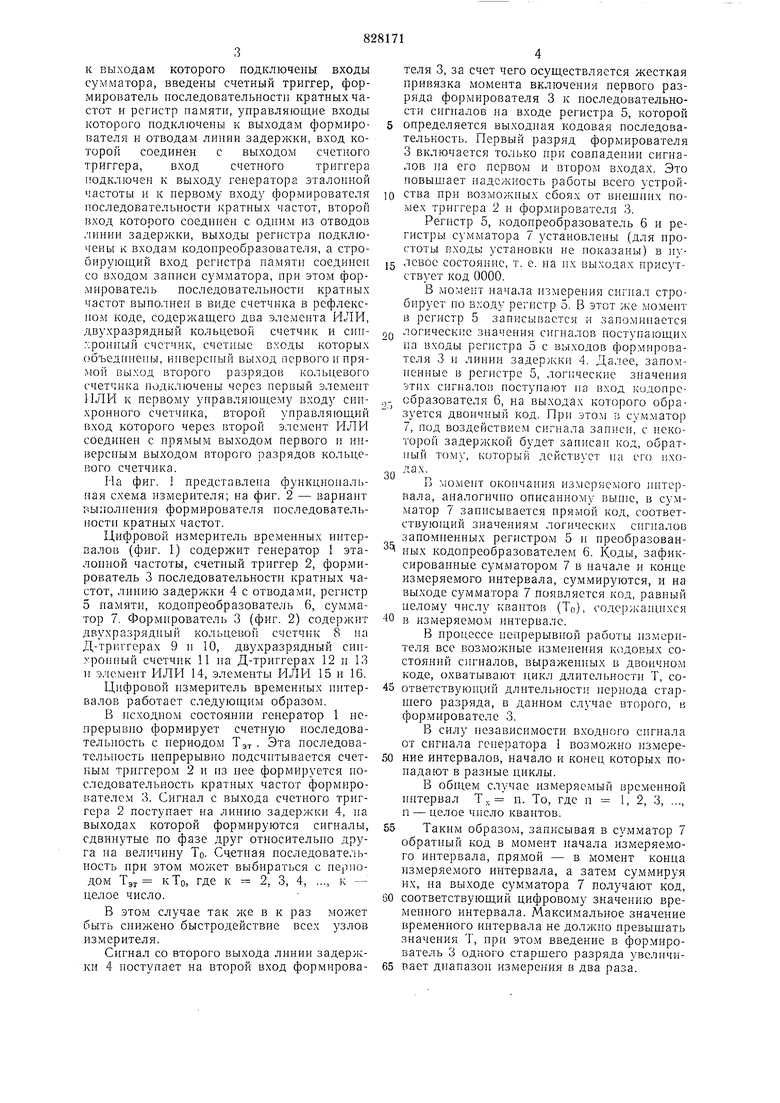

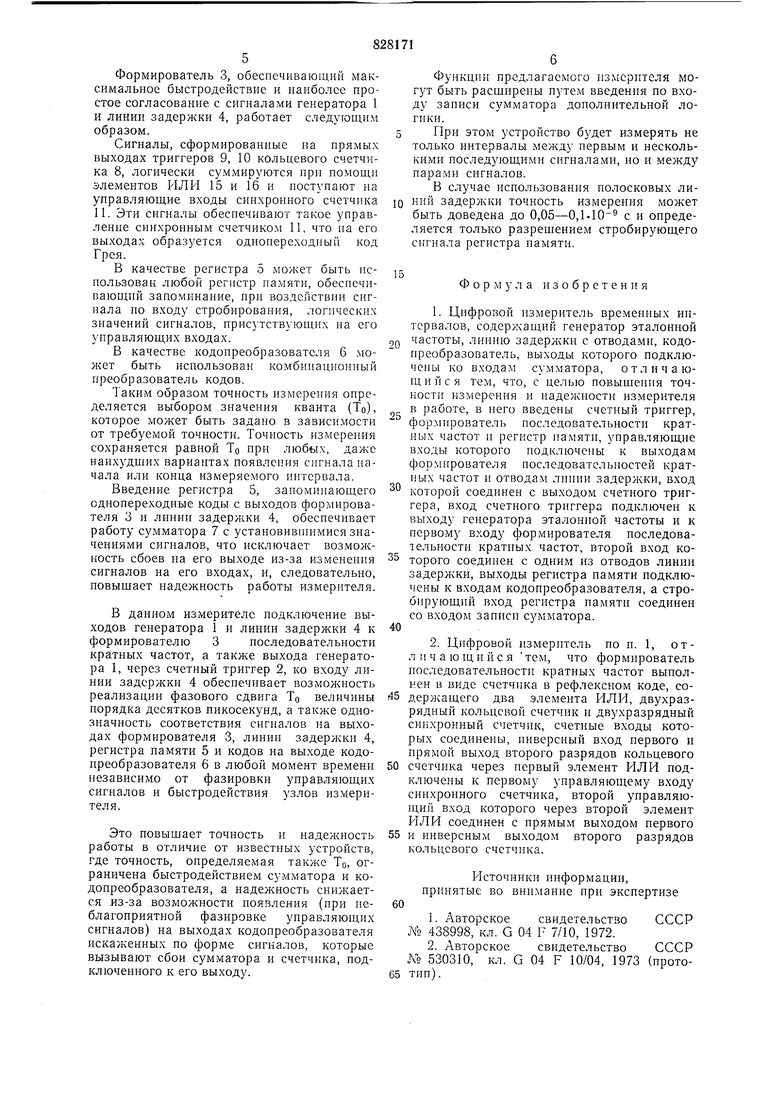

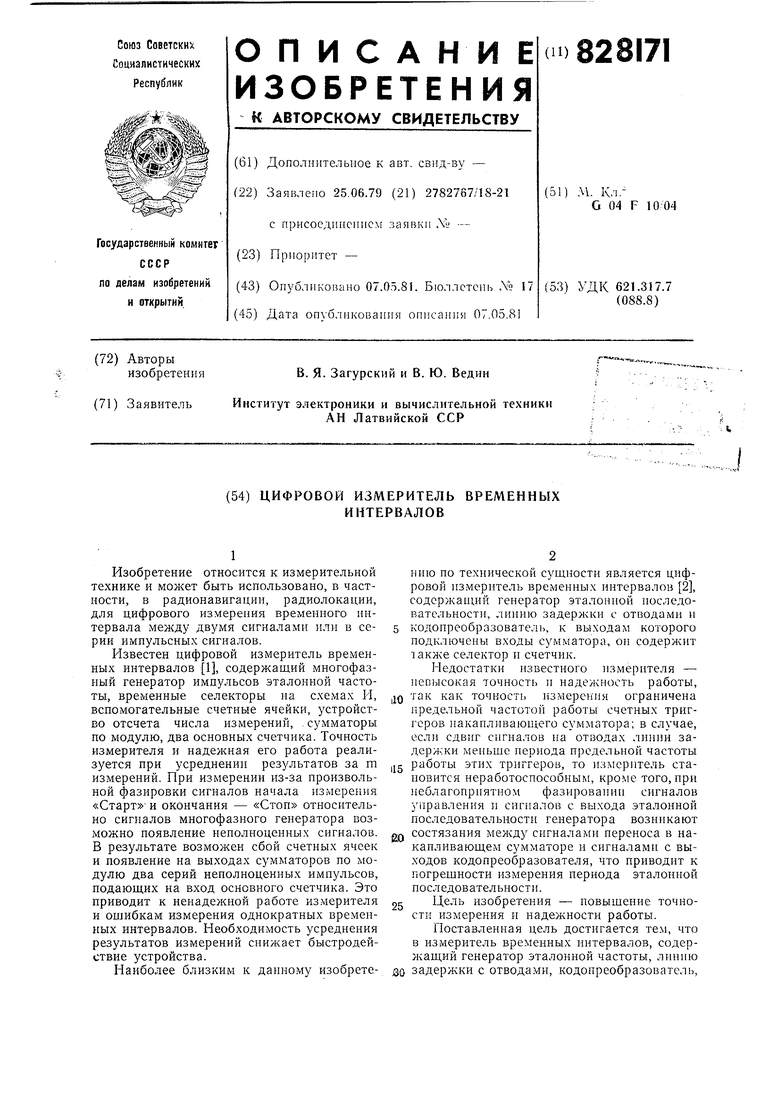

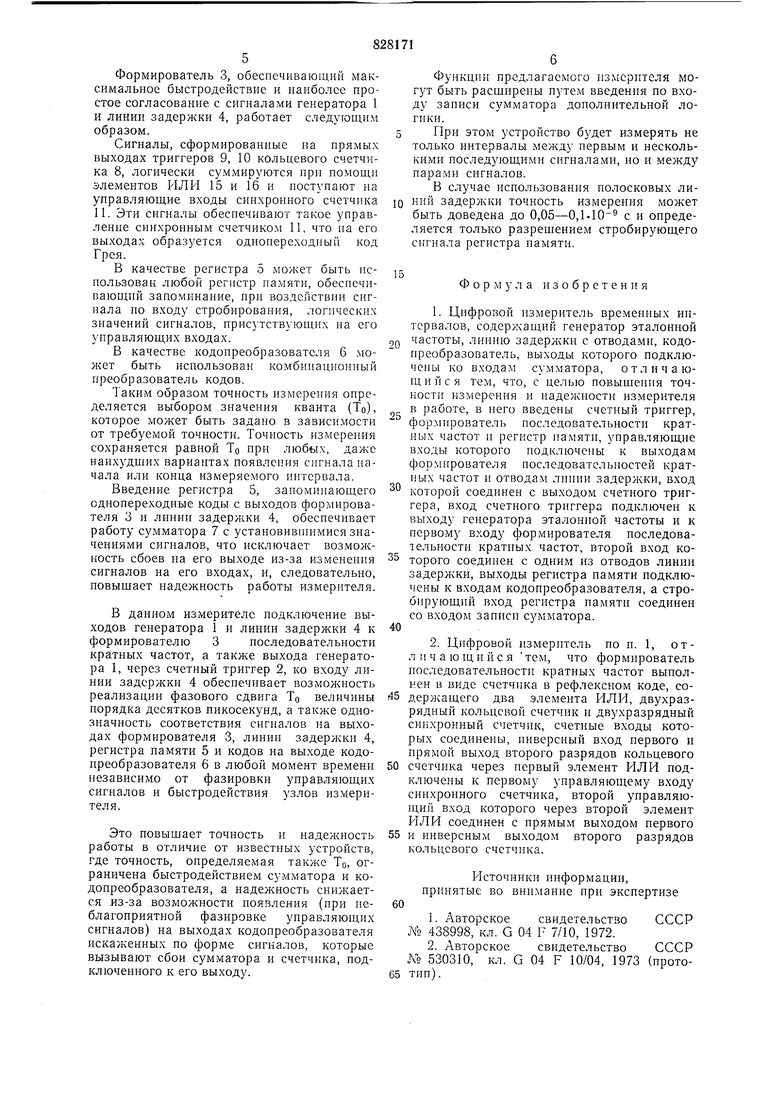

Иа фиг. 1 представлена функциональная схема измерителя; на фиг. 2 - вариант выполнения формирователя иоследовательности кратных частот.

Цифровой измеритель временных интервалов (фиг. 1) содержит генератор 1 эталонной частоты, счетный трнггер 2, формирователь 3 последовательности кратных частот, лииию задержки 4 с отводами, регистр 5 памяти, кодопреобразователь 6, сумматор 7. Формирователь 3 (фиг. 2) содержит двухразрядный кольцевой счетчик 8 на Д-триггерах 9 н 10, двухразрядный сиихроиный счетчик 11 иа Д-триггерах 12 н 13 и элемент ИЛИ 14, элементы 15 и 16.

Цифровой измеритель временных нитервалов работает следуюн им образом.

В исходном состоянии генератор 1 непрерывно формирует счетную последовательность с нериодом Тэт . Эта последовательность непрерывно подсчитывается счетным трнггером 2 и из нее формируется носледовательность кратных частот формирователем 3. Сигнал с выхода счетного триггера 2 поступает на линию задержки 4, на выходах которой формируются сигналы, сдвинутые по фазе друг относительно друга на величину То. Сч;етная последовательноеть нри этом может выбираться с нернодом Тэт к TO, где к 2, 3, 4, ..., к - целое число.

В этом случае так же в к раз дюжет быть еиижено быстродействие веех узлов измерителя.

Сигнал со второго выхода линии задержки 4 поступает на второй вход формирователя 3, за счет чего осуществляется жесткая привязка момента включения нервого разряда формирователя 3 к иоследовательности сигналов на входе регистра 5, которой

онределяетея выходиая кодовая последовательность. Иервый разряд формирователя 3 включается только при совпадении сигналов иа его первом и втором входах. Это новыщает надежность работы всего устройства при возможпых сбоях от внешннх помех триггера 2 и формирователя 3.

Регистр 5, кодопреобразователь 6 и регистры сумматора 7 устаиовлеиы (для простоты входы установки не ноказаны) в нулевое еостоянне, т. е. на их выходах присутствует код 0000.

В момент начала измереиия сигнал стробнрует по входу регистр 5. В этот же момент в регистр 5 записывается и запоминается

Q логические значения сигналов ностунающнх на входы регистра о с выходов формирователя 3 и линии задержки 4. Далее, запомненные в регистре 5, логические значения этпх снгналов поступают па вход кодопреобразователя 6, на выходах которого образуетея двоичный код. Прн этом и сумматор 7, под воздействием сигнала запнсн, с некоторой задержкой будет записан код, обратный тому, который действует па его иходах.

В момент окончания измеряемого интервала, аналогично ониеанному вынш, в сумматор 7 заиисываетея нрямой код, соответствующий значениям логических сигналов запомнеииых регистром 5 и иреобразован пых кодопреобразователем 6. Коды, зафиксированные еумматором 7 в начале и конце измеряемого интервала, суммируются, и на выходе сумматора 7 появляется код, равный нелому числу квантов (То), содержани1хся

в измеряемом ннтервале.

В нроцессе непрерывной работы нзмерителя все возможные изменения кодовых состояннй С1Н-налов, выраженных в двоичном коде, охватывают цикл длительности Т, со5 ответствуюп,ий длительиостн периода старHiero разряда, в данном случае второго, в формирователе 3.

В силу независимости входиого сигнала от сигнала генератора 1 возможно нзмере0 ние интервалов, начало и конец которых нопадают в разные циклы.

В общем случае измеряемый времеиной интервал Т,; п. То, где п 1, 2, 3, ..., п - целое число квантов.

5 Таким образом, записывая в сумматор 7 обратиый код в момент начала измеряемого ннтервала, нрямой - в момент конца измеряемого интервала, а затем суммируя их, на выходе сумматора 7 получают код,

0 соответствующий цифровому значению временного интервала. Максимальное значение временного интервала не должно нревыщать значения Т, прн этом введение в формирователь 3 одного старшего разряда увеличивает диапазон измерения в два раза.

Формирователь 3, обеспечивающий максимальное быстродействие и иаиболсе простое согласоваиие с сигналами генератора 1 и линии задержки 4, работает следующим образом.

Сигналы, сформированные на прямых выходах триггеров 9, 10 кольцевого счетчика 8, логически суммируются нри помощи элементов ИЛИ 15 и 16 и ноступа от на управляющие входы синхронного счетчика П. Эти сигналы обеспечивают такое управление синхронным счетчиком II, что на его выходах образуется однопереходный код Грея.

В качестве регистра 5 может быть иснользован любой регистр памяти, обеснечиваюидий запоминание, нри воздействии сигнала но входу стробирования, логических значений сигналов, нрисутствующнх на его управляющих входах.

В качестве кодопреобразователя 6 может быть иснользован комбинационный преобразователь кодов.

Таким образом точность измерения определяется выбором значения кванта (То), которое может быть задано в зависимости от требуемой точности. Точность измерения сохраняется равной TO при любых, даже наихудших вариантах появления сигнала пачала или конца измеряемого иитервала.

Введенне регистра 5, запоминающего однопереходные коды с выходов формирователя 3 и линии задержки 4, обеснечивает работу сумматора 7 с установнвп1имися значениями сигналов, что исключает возмолхность сбоев на его выходе из-за изменения сигналов на его входах, и, следовательно, повышает надежность работы измерителя.

В данном измерителе подключение выходов генератора 1 и линии задержки 4 к формирователю 3 последовательности кратных частот, а также выхода генератора 1, через счетный триггер 2, ко входу линии задержки 4 обеснечивает возможность реализации фазового сдвига То величины норядка десятков пикосекунд, а также однозначность соответствия сигналов на выходах формирователя 3, линии задержки 4, регистра памяти 5 и кодов на выходе кодопреобразователя б в любой момент времени независимо от фазировки управляющих сигналов и быстродействия узлов измерителя.

Это повышает точность и надежность работы в отличие от известных устройств, где точность, определяемая также TO, ограничена быстродействием сумматора и кодопреобразователя, а надежность снижается из-за возможности ноявления (нри неблагоприятной фазировке управляющих сигналов) на выходах кодопреобразователя искаженных по форме сигналов, которые вызывают сбои сумматора и счетчика, подключенного к его выходу.

Функции предлагаемого измерителя могут быть расширены путем введения по входу записи сумматора дополнительной логики.

Ири этом устройство будет измерять не только интервалы .между первым и несколькими последующими сигналами, но и между парами сигналов.

В случае использования нолосковых лиНИИ задержки точность измерения может быть доведена до 0,05--0,1-10 с и определяется только разрешением стробирующего сигнала регистра памяти.

Формула изобретения

1.Цифровой из.меритель временных интервалов, содержащий генератор эталонной

частоты, лииию задержки с отводами, кодопреобразователь, выходы которого подключепы ко входам сумматора, отличающийся тем, что, с целью повышения точности измерения н надежности измерителя в работе, в иего введены счетный триггер,

формирователь последовательности кратных частот и регистр памяти, управляющие входы которого подключепы к выходам формирователя последовательностей кратных частот и отводам лппии задержки, вход которой соединен с выходом счетного триггера, вход счетного триггера подключен к выходу генератора эталонной частоты и к первому входу формирователя последовательности кратных частот, второй вход которого соединен с одним из отводов линии задержки, выходы регистра памяти подключены к входам кодопреобразователя, а стробирующий вход регистра памяти соединен со входом записи сумматора.

2.Цифровой измеритель но п. 1, отл п ч а ю щ и и с я тем, что формирователь последовательности кратных частот выполнен в виде счетчика в рефлексном коде, содержащего два элемента ИЛИ, двухразрядный кольцевой счетчик ц двухразрядный синхронный счетчик, счетные входы которых соединены, инверсный вход первого и прямой выход второго разрядов кольцевого

0 счетчика через первый элемент ИЛИ подключены к первому управляющему входу синхронного счетчика, второй управляющий вход которого через второй элемент ИЛИ соединен е прямым выходом первого

5 и инверсным выходом второго разрядов кольцевого счетчика.

Источинки информации, принятые во внимание при экспертизе

60

1.Авторское свидетельство

СССР № 438998, кл. G 04 F 7/10, 1972.

2.Авторское свидетельство СССР N° 530310, кл. G 04 F 10/04, 1973 (нрото65 тип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой измеритель частоты заполнения радиоимпульсов | 1982 |

|

SU1161892A1 |

| Цифровой измеритель временных характеристик электрического сигнала | 1985 |

|

SU1291897A1 |

| Цифровой генератор | 1986 |

|

SU1347164A1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| Устройство передачи и приема дискретной информации | 1979 |

|

SU902296A1 |

| Устройство для динамической индикацииВРЕМЕНи СуТОК и КАлЕНдАРя | 1978 |

|

SU805244A2 |

| Измерительный двухфазный генератор | 1987 |

|

SU1442931A1 |

| Цифровой измеритель частоты | 1983 |

|

SU1290190A1 |

| Измеритель временных интервалов | 1983 |

|

SU1155990A1 |

| Преобразователь код-временной интервал | 1979 |

|

SU822348A1 |

г

Авторы

Даты

1981-05-07—Публикация

1979-06-25—Подача