1

Изобретение относится к области импульсной техники и может быть использовано в автоматизированных системах контроля и управления, а также для анализаторов и синтезаторов сигналов в радиофизике, океанологии, системах связи.

Целью изобретения является повышение быстродействия за счет введения новой процедуры формирования кодов с уменьшением времени между микрокомандами останова.

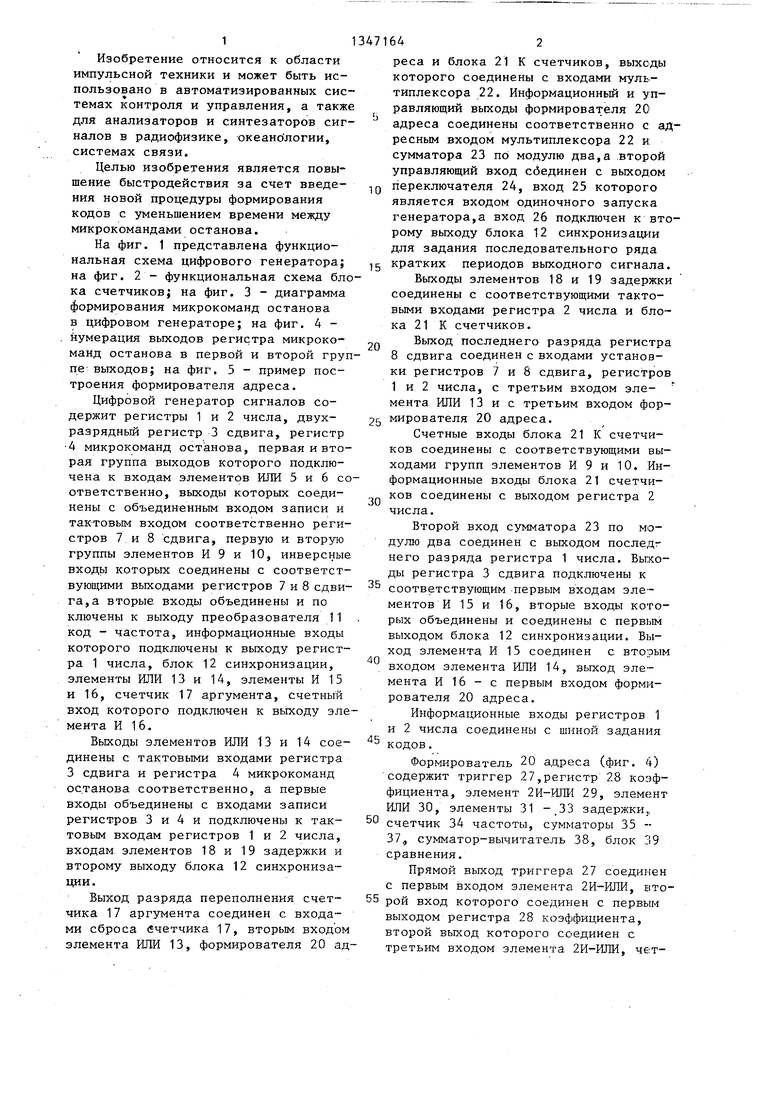

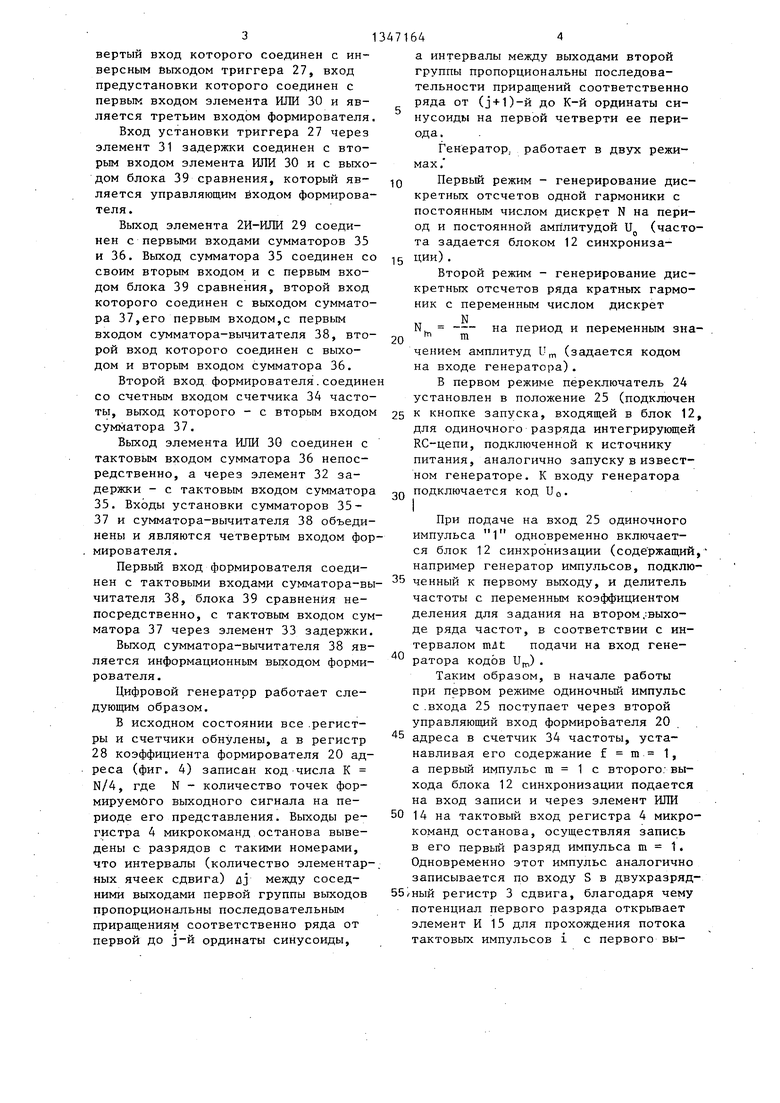

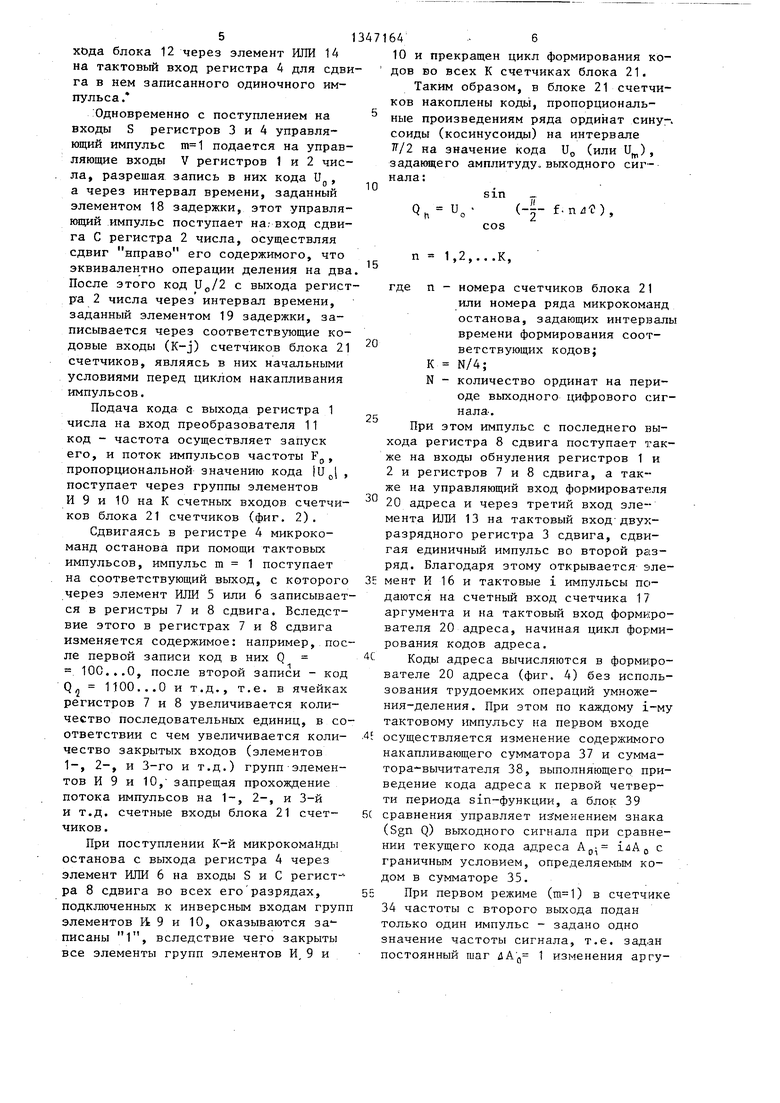

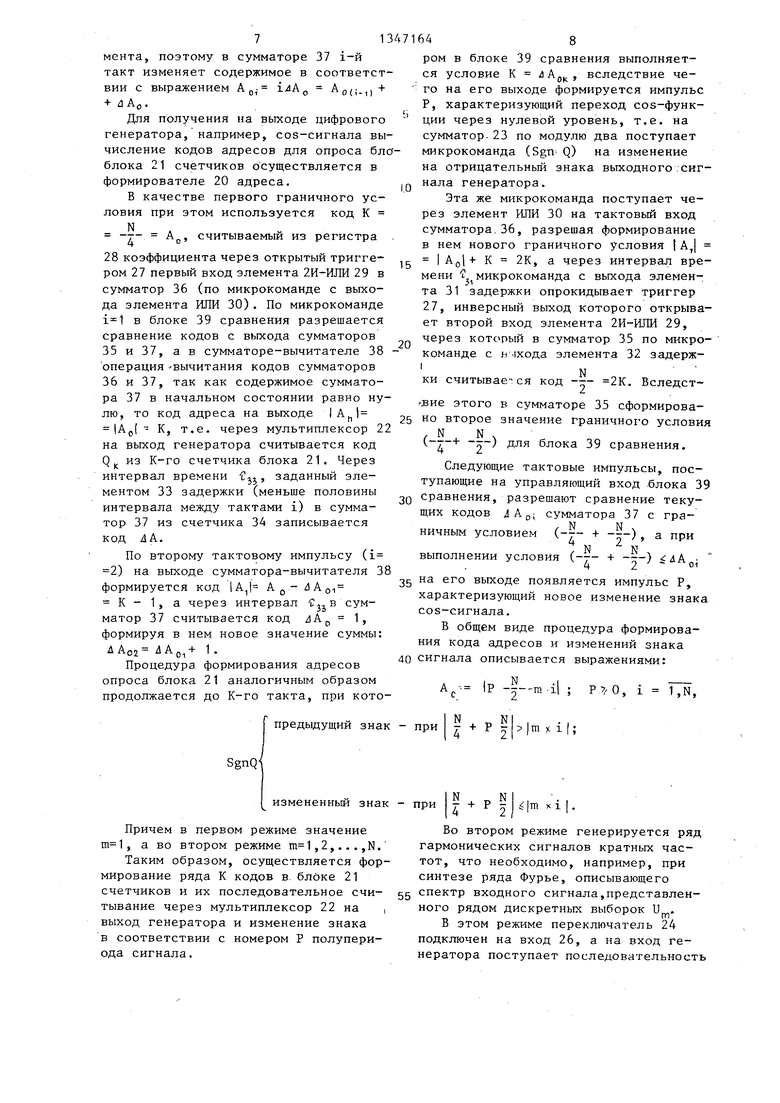

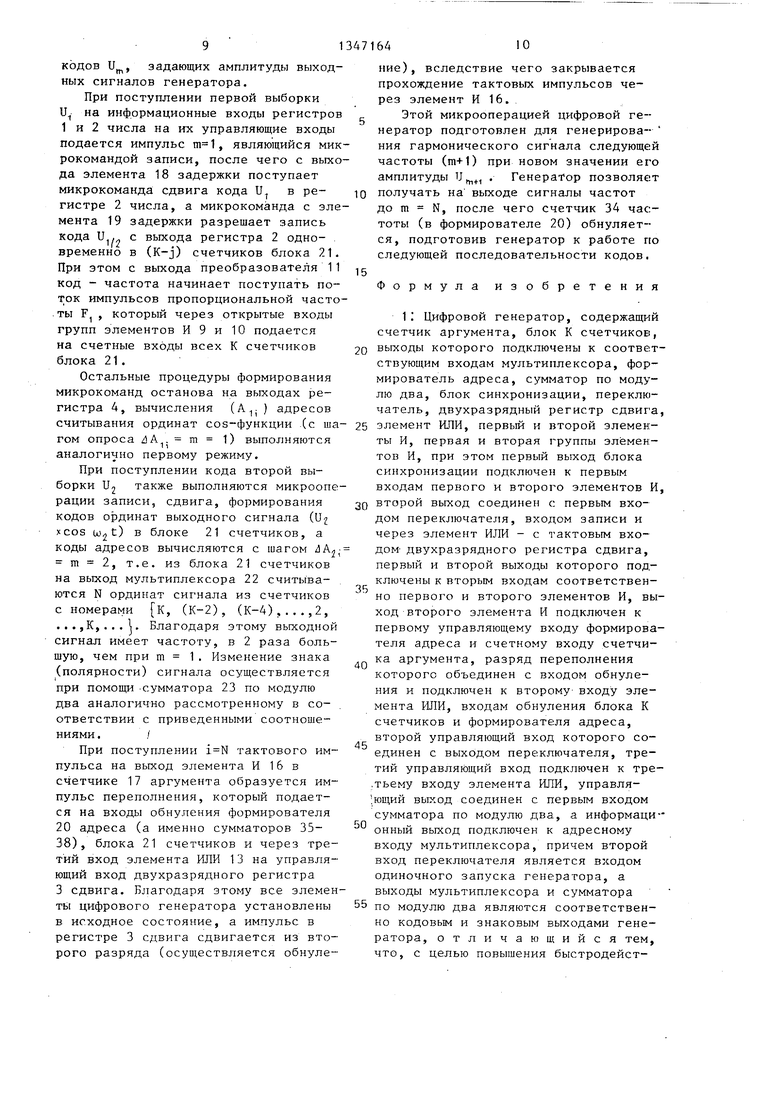

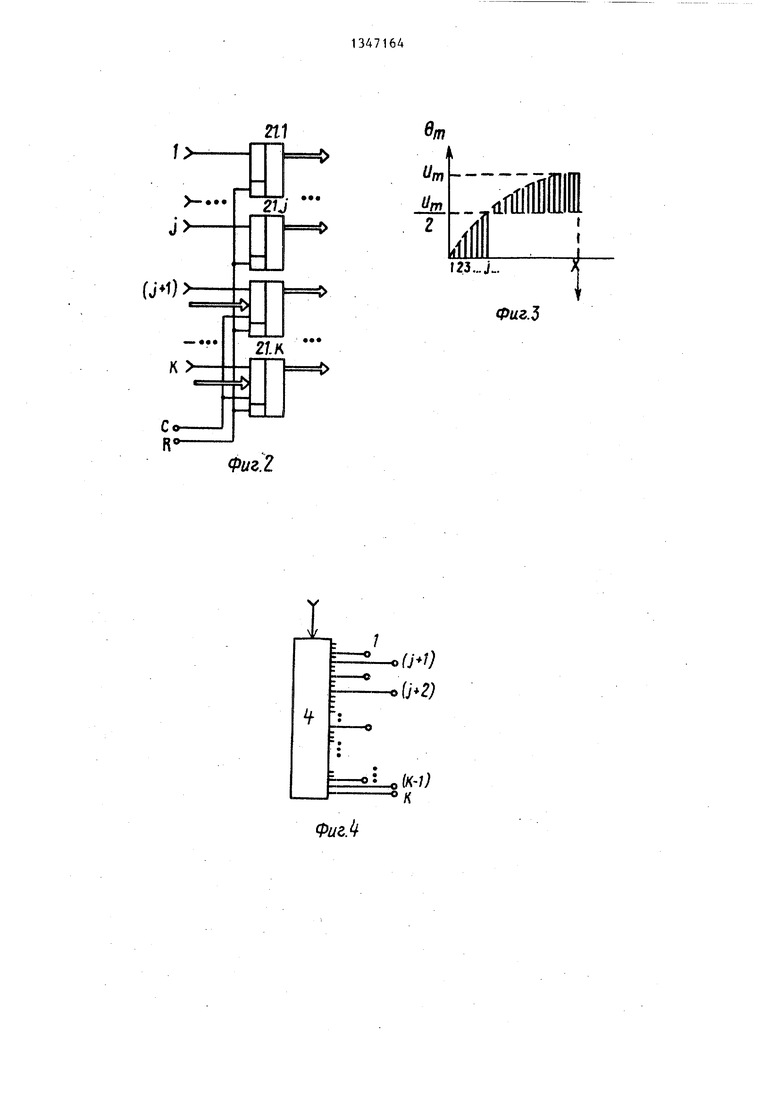

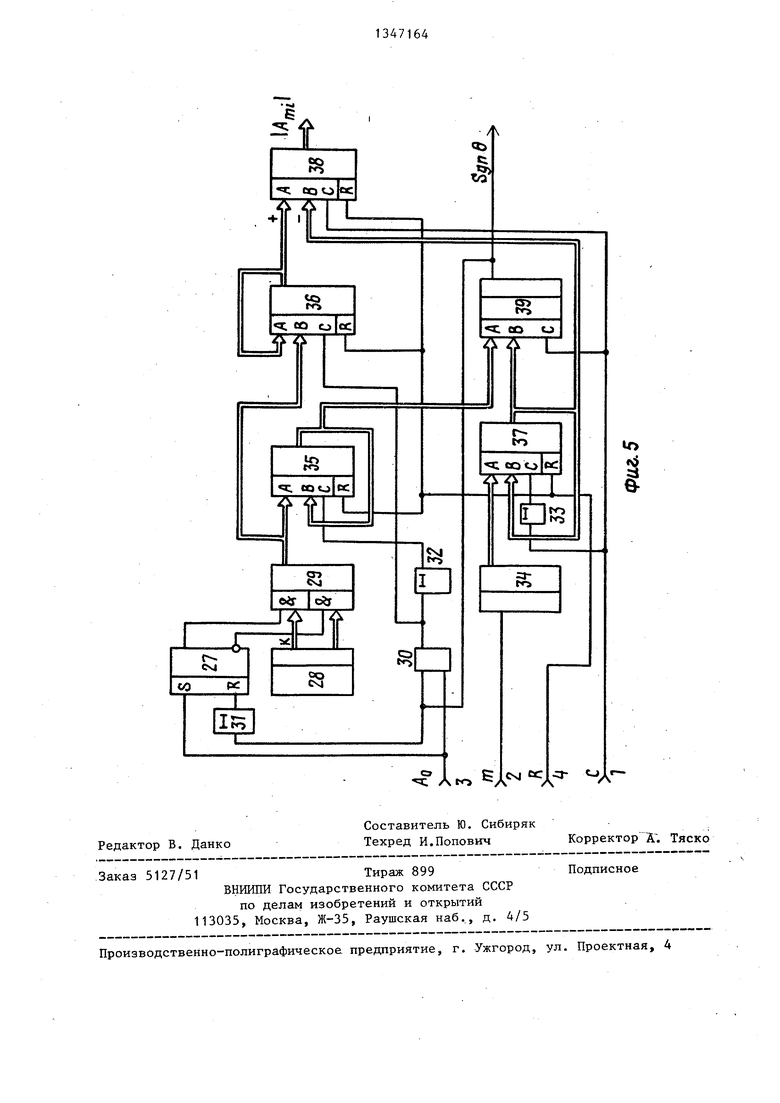

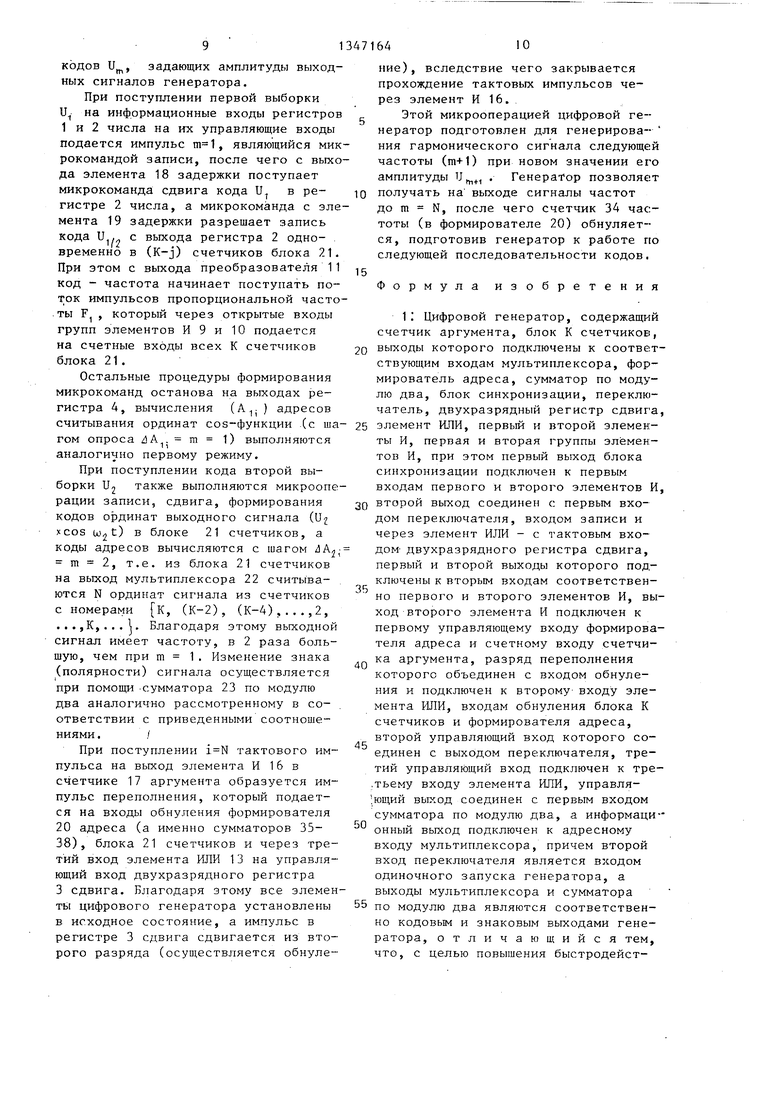

На фиг. 1 представлена функциональная схема цифрового генератора; на фиг. 2 - функциональная схема бло ка счетчиков; на фиг. 3 - диаграмма формирования микрокоманд останова в цифровом генераторе; на фиг. 4 - нумерация выходов регистра микрокоманд останова в первой и второй группе выходов; на фиг, 5 - пример построения формирователя адреса.

Цифровой генератор сигналов содержит регистры 1 и 2 числа, двухразрядный регистр 3 сдвига, регистр 4 микрокоманд останова, первая и вторая группа выходов которого подключена к входам элементов ИГШ 5 и 6 соответственно, выходы которых соединены с объединенным входом записи и тактовым входом соответственно регистров 7 и 8 сдвига, первую и вторую группы элементов И 9 и 10, инверсные входы которых соединены с соответствующими выходами регистров 7 и 8 сдвига, а вторые входы объединены и по ключены к выходу преобразователя 11 код - частота, информационные входы которого подключены к выходу регистра 1 числа, блок 12 синхронизации, элементы ИЛИ 13 и 14, элементы И 15 и 16, счетчик 17 аргумента, счетный вход которого подключен к выходу элемента И 16.

Выходы элементов ИЛИ 13 и 14 соединены с тактовыми входами регистра 3 сдвига и регистра 4 микрокоманд останова соответственно, а первые входы объединены с входами записи регистров 3 и 4 и подключены к тактовым входам регистров 1 и 2 числа, входам элементов 18 и 19 задержки и второму выходу блока 12 синхронизации.

Выход разряда переполнения счетчика 17 аргумента соединен с входами сброса счетчика 17, вторым входом элемента ИЛИ 13, формирователя 20 ад20

471642

реса и блока 21 К счетчиков, выходы которого соединены с входами мультиплексора 22. Информационньй и управляющий выходы формирователя 20 адреса соединены соответственно с адресным входом мультиплексора 22 и; сумматора 23 по модулю два,а .второй управляющий вход сбединен с выходом д переключателя 24, вход 25 которого является входом одиночного запуска генератора,а вход 26 подключен к второму вьгходу блока 12 синхронизации для задания последовательного ряда 5 кратких периодов выходного сигнала.

Выходы элементов 18 и 19 задержки соединены с соответствующими тактовыми входами регистра 2 числа и блока 21 К счетчиков.

Выход последнего разряда регистра 8 сдвига соединен с входами установки регистров 7 и 8 сдвига, регистров 1 и 2 числа, с третьим входом элемента ИЛИ 13 и с третьим входом фор- 25 мирователя 20 адреса.

Счетные входы блока 21 К счетчиков соединены с соответствующими выходами групп элементов И 9 и 10. Информационные входы блока 21 счетчиков соединены с выходом регистра 2 числа.

Второй вход сумматора 23 по модулю два соединен с выходом последг него разряда регистра 1 числа. Вьгко- ды регистра 3 сдвига подключены к соответствующим первым входам элементов И 15 и 16, вторые входы которых объединены и соединены с первь М выходом блока 12 синхронизации. Выход элемента И 15 соединен с вторым входом элемента ИЛИ 14, выход элемента И 16 - с первым входом формирователя 20 адреса.

Информационные входы регистров 1 и 2 числа соединены с шиной задания кодов.

Формирователь 20 адреса (фиг. 4) содержит триггер 27,регистр 28 коэффициента, элемент 2И-Ш1И 29, элемент ИЛИ 30, элементы 31 -.33 задержки., счетчик 34 частоты, сумматоры 35 - 37, сумматор-в.ычитатель 38, блок 39 сравнения.

Прямой выход триггера 27 соединен с первым входом элемента 2И-ИЛИ, вто- 55 рой вход которого соединен с первым выходом регистра 28 коэффициента, второй выход которого соединен с третьим входом элемента 2И-ИЛИ, чет30

35

40

45

50

вертый вход которого соединен с инверсным выходом триггера 27, вход предустановки которого соединен с первым входом элемента ИЛИ 30 и является третьим входом формирователя

Вход установки триггера 27 через элемент 31 задержки соединен с вторым входом элемента ИЛИ 30 и с выходом блока 39 сравнения, который является управляющим входом формирователя.

Выход элемента 2И-ИЛИ 29 соединен с первыми входами сумматоров 35 и 36. Выход сумматора 35 соединен со своим вторым входом и с первым входом блока 39 сравнения, второй вход которого соединен с выходом сумматора 37,его первым входом,с первым входом сумматора-вычитателя 38, второй вход которого соединен с выходом и вторым входом сумматора 36.

Второй вход формирователя.соедине со счетным входом счетчика 34 частоты, выход которого - с вторым входом сумматора 37.

Выход элемента ИЛИ 30 соединен с тактовым входом сумматора 36 непосредственно, а через элемент 32 задержки - с тактовым входом сумматора 35. Входы установки сумматоров 35- 37 и сумматора-вычитателя 38 объединены и являются четвертым входом формирователя.

Первьш вход формирователя соединен с тактовыми входами сумматора-вычитателя 38, блока 39 сравнения непосредственно, с тактовым входом сумматора 37 через элемент 33 задержки.

Выход сумматора-вычитателя 38 является информационнь1м выходом формирователя.

Цифровой генератор работает следующим образом.

В исходном состоянии все .регистры и счетчики обнулены, а в регистр 28 коэффициента формирователя 20 адреса (фиг. 4) записан код числа К N/4, где N - количество точек формируемого выходного сигнала на периоде его представления. Выходы регистра 4 микрокоманд останова выведены с разрядов с такими номерами, что интервалы (количество элементарных ячеек сдвига) dj между соседними выходами первой группы выходов пропорциональны последовательным приращениям соответственно ряда от первой до j-й ординаты синусоиды.

а интервалы между выходами второй группы пропорциональны последовательности приращений соответственно ряда от (+1)-й до К-й ординаты синусоиды на первой четверти ее периода.

Генератор, работает в двух режимах .

Первый режим - генерирование дискретных отсчетов одной гармоники с постоянным числом дискрет N на период и постоянной амплитудой U (частота задается 15 Ции).

блоком 12 синхрониза

Второй режим - генерирование дискретных отсчетов ряда кратных гармоник с переменным числом дискрет

N --- т

на период и переменным значением амплитуд и„ (задается кодом на входе генератора).

В первом режиме переключатель 24 установлен в положение 25 (подключен к кнопке запуска, входящей в блок 12, для одиночного разряда интегрирующей RC-цепи, подключенной к источнику

30

ном генераторе. К входу подключается код UQ.

генератора

При подаче на вход 25 одиночного импульса 1 одновременно включается блок 12 синхронизации (содержащий, например генератор импульсов, подключенный к первому выходу, и делитель частоты с переменным коэфф ициентом еления для задания на втором выходе ряда частот, в соответствии с интервалом mAt подачи на вход генератора кодов и,) .

Таким образом, в начале работы при первом режиме одиночный импульс с .входа 25 поступает через второй управляющий вход формирователя 20 адреса в счетчик 34 частоты, устанавливая его содержание f m 1, а первый импульс m 1 с второго; выхода блока 12 синхронизации подается на вход записи и через элемент ИЖ 14 на тактовый вход регистра 4 микров его первьм разряд импульса m 1. Одновременно этот импульс аналогично записывается по входу S в двухразряд- 55шый регистр 3 сдвига, благодаря чему потенциал первого разряда открьшает элемент И 15 для прохождения потока тактовых импульсов i с первого вы5

хода блока 12 через элемент ИЛИ 14 на тактовый вход регистра 4 для сдвига в нем записанного одиночного импульса.

Одновременно с поступлением на входы S регистров 3 и 4 управляющий импульс подается на управляющие входы V регистров 1 и 2 числа, разрешая запись в них кода U, а через интервал времени, заданный элементом 18 задержки, этот управляющий импульс поступает на;вход сдвига С регистра 2 числа, осуществляя сдвиг вправо его содержимого, что

эквивалентно операции деления на два После этого код Uo/2 с выхода регистра 2 числа через интервал времени, заданный элементом 19 задержки, записывается через соответствующие кодовые входы (K-J) счетчиков блока 21 счетчиков, являясь в них начальными условиями перед циклом накапливания импульсов.

Подача кода с выхода регистра 1 числа на вход преобразователя 11 код - частота осуществляет запуск его, и поток импульсов частоты F, пропорциональной значению кода |Uj,| , поступает через группы элементов И 9 и 10 на К счетных входов счетчи- ков блока 21 счетчиков (фиг. 2).

Сдвигаясь в регистре 4 микрокоманд останова при помощи тактовых импульсов, импульс m 1 поступает на соответствующий выход, с которого через элемент ИЛИ 5 или 6 записывается в регистры 7 и 8 сдвига. Вследствие этого в регистрах 7 и 8 сдвига изменяется содержимое: например, после первой записи код в них Q 100...О, после второй записи - код Q,, 1100...О и т.д., т.е. в ячейках регистров 7 и 8 увеличивается количество последовательных единиц, в соответствии с чем увеличивается коли- чество закрытых входов (элементов 1-, 2-, и 3-го и т.д.) групп-элементов И 9 и 10, запрещая прохождение потока импульсов на 1-, 2-, и 3-й и т.д. счетные входы блока 21 счет- чиков.

При поступлении К-й микрокоманды останова с выхода регистра 4 через элемент ИЛИ 6 на входы S и С регистра 8 сдвига во всех его разрядах, подключенных к инверсным входам груп элементов № 9 и 10, оказываются записаны 1

вследствие чего закрыты

все элементы групп элементов И, 9 и

64; 6

10 и прекращен цикл формирования кодов во всех К счетчиках блока 21.

Таким образом, в блоке 21 счетчиков накоплены кодьг, пропорциональные произведениям ряда ординат синусоиды (косинусоиды) на интервгше 7Г/2 на значение кода UQ (или U) , задающего амплитуду, выходного сигнала:

sin

/I

( f. ).

cos

п

1,/,...К,

5

Е С

5

где п - номера счетчиков блока 21

или номера ряда микрокоманд останова, задающих интервалы времени формирования соответствующих кодов; К N/4;

N - количество ординат на периоде выходного цифрового сигнала-.

При этом импульс с последнего выхода регистра 8 сдвига поступает также на входы обнуления регистров 1 и 2 и регистров 7 и 8 сдвига, а также на управляющий вход формироват€шя 20 адреса и через третий вход элемента ШМ 13 на тактовый вход двук- разрядного регистра 3 сдвига, сдвигая единичный импульс во второй разряд. Благодаря этому открывается- элемент И 16 и тактовые i импульсы подаются на счетный вход счетчика 17 аргумента и на тактовый вход формирователя 20 адреса, начиная цикл формирования кодов адреса.

Коды адреса вычисляются в формирователе 20 адреса (фиг. 4) без использования трудоемких операций умножения-деления. При этом по каждому i-му тактовому импульсу на первом входе осуществляется изменение содержимого накапливающего сумматора 37 и сумма- тора-вычитателя 38, выполняющего приведение кода адреса к первой четверти периода sin-функции, а блок 39 сравнения управляет изменением знака (Sgn Q) выходного сигнала при сравнении текущего кода адреса Ар- , с граничньм условием, определяемым кодом в сумматоре 35.

При первом режиме () в счетчике 34 частоты с второго выхода подан только один импульс - задано одно значение частоты сигнала, т.е. задан постоянный шаг ЛА (, 1 изменения аргу

713

мента, поэтому в сумматоре 37 i-й такт изменяет содержимое в соответствии с выражением Ад,- , АО(;.,,+ + лАоДля получения на выходе цифрового генератора, например, cos-сигнала вычисление кодов адресов для опроса бло блока 21 счетчиков осуществляется в формирователе 20 адреса.

В качестве первого граничного условия при этом используется код К

N т - AJJ, считываемый из регистра

28 коэффициента через открытый триггером 27 первый вход элемента 2И-ИЛИ 29 в сумматор 36 (по микрокоманде с выхода элемента ИЛИ 30). По микрокоманде в блоке 39 сравнения разрешается сравнение кодов с выхода сумматоров

35и 37, а в сумматоре-вычитателе 38 операция Вычитания кодов сумматоров

36и 37, так как содержимое сумматора 37 в начальном состоянии равно нулю, то код адреса на выходе |А|( |А(,( - К, т.е. через мультиплексор 22 на выход генератора считывается код

Q из К-го счетчика блока 21. Через интервал времени D, заданный элементом 33 задержки (меньше половины интервала между тактами i) в сумматор 37 из счетчика 34 записывается код ЛА.

По второму тактовому импульсу (i 2) на выходе сумматора-вычитателя 38 формируется код А - 4Aoi К - 1, а через интервал Cjjв сумматор 37 считывается код лА 1, формируя в нем новое значение суммы: ДАо2 1.

Процедура формирования адресов опроса блока 21 аналогичным образом продолжается до К-го такта, при кото

предьщущий знак - при

измененный знак - при

Причем в первом режиме значение , а во втором режиме ,2,...,N.

Таким образом, осуществляется формирование ряда К кодов в. блоке 21 счетчиков и их последовательное считывание через мультиплексор 22 на , выход генератора и изменение знака в соответствии с номером Р полупериода сигнала.

15

0

71

,д

с

30

648

ром в блоке 39 сравнения выполняется условие К Aj, вследствие чего на его выходе формируется импульс Р, характеризующий переход cos-функции через нулевой уровень, т.е. на сумматор. 23 по модулю два поступает микрокоманда (Sgn- Q) на изменение на отрицательный знака выходного.сигнала генератора.

Эта же микрокоманда поступает через элемент ИЛИ 30 на тактовый вход сумматора.36, разрешая формирование в нем нового граничного условия | А,| I А( К 2К, а через интервал вре- меЕш t микрокоманда с выхода элемента 31 задержки опрокидывает триггер 27, инверсный выход которого открывает второй вход элемента 2И-ИЛИ 29, через котсфый в сумматор 35 по микрокоманде с в -гхода элемента 32 задерж N

ки считывав- ся код --- 2К. Вследст вие этого в сумматоре 35 сформировано второе значение граничного условия /- N N , .T-+ 2 блока 39 сравнения.

CлeдyюD иe тактовые импульсы, поступающие на управляющий вход .блока 39 сравнения, разрешают сравнение текущих кодов 4 Ар; сумматора 37 с граничным условием (-- + -), а при

М

выполнении условия (-7 + -«-) 4А

на его выходе появляется импульс Р, характеризующий новое изменение знака cos-сигнала.

В общем виде процедура формирования кода адресов и изменений знака сигнала описывается выражениями:

. IP

, i 1,N,

N Р N

m X 1

N + Р N

Im X i

Во втором режиме генерируется ряд гармонических сигналов кратных частот, что необходимо, например, при синтезе ряда Фурье, описывающего 55 спектр входного сигнала,представленного рядом дискретных выборок U.

В этом режиме переключатель 24 подключен на вход 26, а на вход генератора поступает последовательность

5

10

91

кодов и, задающих амплитуды выходных сигналов генератора.

При поступлении первой выборки и на информационные входы регистров 1 и 2 числа на их управляющие входы подается импульс , являющийся мик рокомандой записи, после чего с выхода элемента 18 задержки поступает микрокоманда сдвига кода U в регистре 2 числа, а микрокоманда с элемента 19 задержки разрешает запись кода и, с выхода регистра 2 одновременно в (K-J) счетчиков блока 21, При этом с выхода преобразователя 11 код - частота начинает поступать поток импульсов пропорциональной частоты F , который через открытые входы групп элементов И 9 и 10 подается на счетные входы всех К счетчиков 20 блока 21.

Остальные процедуры формирования микрокоманд останова на выходах регистра 4, вычисления ( ) адресов считывания ординат cos-функции (с ша- 25 гом опроса /1А. m 1) выполняются аналогично первому режиму.

При поступлении кода второй выборки Uj также выполняются микрооперации записи, сдвига, формирования gg

кодов ординат выходного сигнала (U xcos U) t) в блоке 21 счетчиков, а коды адресов вычисляются с шагом m 2, т.е. из блока 21 счетчиков на выход мультиплексора 22 считываются N ординат сигнала из счетчиков с номерами к, (К-2), (К-4),...,2, ...,К, . . . . Благодаря этому выходной сигнал имеет частоту, в 2 раза большую, чем при m 1. Изменение знака (полярности) сигнала осуществляется при помощи -сумматора 23 по модулю два аналогично рассмотренному в соответствии с приведенными соотношениями . /

При поступлении тактового импульса на выход элемента И 1 б в счетчике 17 аргумента образуется импульс переполнения, который подается на входы обнуления формирователя 20 адреса (а именно сумматоров 35- 38), блока 21 счетчиков и через третий вход элемента ШШ 13 на управляющий вход двухразрядного регистра 3 сдвига. Благодаря этому все элемен- ть1 цифрового генератора установлены 55 в исходное состояние, а импульс в регистре 3 сдвига сдвигается из второго разряда (осуществляется обнуле34716410

ние), вследствие чего закрывается прохождение тактовых импульсов через элемент И 16.

Этой микрооперацией цифровой генератор подготовлен для генерирова- НИН гармонического сигнала следующей частоты (т+1) при новом значении его амплитуды и, . Генератор позволяет получать на выходе сигналы частот до m N, после чего счетчик 34 частоты (в формирователе 20) обнуляется, подготовив генератор к работе по

35

40

45

50

следующей последовательности кодов. Формула изобретения

1; Цифровой генератор, содержащий счетчик аргумента, блок К счетчиков, выходы которого подключены к соответствующим входам мультиплексора, формирователь адреса, сумматор по модулю два, блок синхронизации, переключатель, двухразрядный регистр сдвига, элемент ИЛИ, первый и второй элементы И, первая и вторая группы элементов И, при этом первый блока синхронизации подключен к первым входам первого и второго элементов И, второй выход соединен с первым входом переключателя, входом записи и через элемент ИЛИ - с тактовым вхо- дом двухразрядного регистра сдвига, первый и второй выходы которого подключены к вторым входам соответственно первого и второго элементов И, выход второго элемента И подключен к первому управляющему входу формирователя адреса и счетному входу счетчика аргумента, разряд переполнения которого объединен с входом обнуления и подключен к второму- входу элемента ШШ, входам обнуления блока К счетчиков и формирователя адреса, второй управляющий вход которого соединен с выходом переключателя, третий управляющий вход подключен к тре- .тьему входу элемента ИЛИ, управля- ющий выход соединен с первым входом сумматора по модулю два, а информационный выход подключен к адресному входу мультиплексора, причем второй вход переключателя является входом одиночного запуска генератора, а выходы мультиплексора и сумматора по модулю два являются соответственно кодовым и знаковым выходами генератора, отличающийся тем, что, с целью повышения быстродейст0

5

g

5

5

0

5

0

следующей последовательности кодов. Формула изобретения

1; Цифровой генератор, содержащий счетчик аргумента, блок К счетчиков, выходы которого подключены к соответствующим входам мультиплексора, формирователь адреса, сумматор по модулю два, блок синхронизации, переключатель, двухразрядный регистр сдвига, элемент ИЛИ, первый и второй элементы И, первая и вторая группы элементов И, при этом первый блока синхронизации подключен к первым входам первого и второго элементов И, второй выход соединен с первым входом переключателя, входом записи и через элемент ИЛИ - с тактовым вхо- дом двухразрядного регистра сдвига, первый и второй выходы которого подключены к вторым входам соответственно первого и второго элементов И, выход второго элемента И подключен к первому управляющему входу формирователя адреса и счетному входу счетчика аргумента, разряд переполнения которого объединен с входом обнуления и подключен к второму- входу элемента ШШ, входам обнуления блока К счетчиков и формирователя адреса, второй управляющий вход которого соединен с выходом переключателя, третий управляющий вход подключен к тре- .тьему входу элемента ИЛИ, управля- ющий выход соединен с первым входом сумматора по модулю два, а информационный выход подключен к адресному входу мультиплексора, причем второй вход переключателя является входом одиночного запуска генератора, а выходы мультиплексора и сумматора по модулю два являются соответственно кодовым и знаковым выходами генератора, отличающийся тем, что, с целью повышения быстродейст

111

ВИЯ, в него введены первый и второй регистры числа, преобразователь код частота, регистр микрокоманд останова, первый и второй регистры сдвига, первый и второй элементы задержки, второй, третий и четвертый элементы ИЛИ, причем вход записи регистра микрокоманд останова соединен с первым входом второго элемента ИЛИ, управ- ляюпщми входами первого и второго регистров числа и входами первого и второго элементов задержки и подклю- .чен к второму выходу блока синхронизации, выход первого элемента И чере второй вход второго элемента ИЛИ соединен с управляющим входом регистра микрокоманд останова, первая группа j выходов которого подключена к соответствующим входам третьего элемента ИЛИ, вторая группа K-j выходов подключена к соответствующим вх.одам четвертого элемента ИЛИ, выходы третьего и четвертого элементов ИЛИ соединены с объединенными входом записи и управляйщим входом соответственно первого и второго регистров сдвига, выходы которых подключены к инверсным входам соответственно первой и второй групп элементов И, вторые входы которых соединены с выходом преобразователя код - частота, выходы первой группы элементов И подключены к первым j счетным входам блока К счётчиков, выходы второй группы элементов И подключены к последним K-j счетным входам блока К счетчиков а соответствующие K-j кодовые входы блока К счетчиков соединены с выходом второго регистра числа, причем последний выход второго-регистра сдвига объединен с входами обнуления первого и второго регистров сдвига и подключен к входам обнуления первого и второго регистров числа и третьему управляющему входу формирова- теля адреса, выходы первого и второго элементов задержки соединены соответственно с вторым управляющим -входом второго регистра числа и управляющим входом блока К счетчиков, а ко- довый и знаковый выходы первого регистра числа соединены соответственно с входом преобразователя код - частота и вторым входом сумматора по модулю два, при этом кодовые входы

64

12

0

5

5 б 0 5

0

первого и второго регистр9в числа объединены и подключены к:входу задания амплитуды выходного сигнала.

2. Генератор по п. 1, о т л и - чающийся тем, что формирователь адреса содержит триггер, регистр коэффициента, элемент 2И-ИЛИ, элемент ИЛИ, три элемента задержки, счетчик частоты, три сумматора, сум- матор-вычитатель, блок сравнения, причем прямой выход триггера соединен с вторым входом элемента 2И-ИЛИ, второй вход которого соединен с пер- бым выходом регистра коэффициента, второй выход которого соединен с третьим входом элемента 2И-ИЛИ, четвертый вход которого соединен с инверсным входом триггера, вход пре - дустановки которого соединен с первым входом элемента ИЛИ и является третьим входом формирователя, вход установки триггера через первый элемент задержки соединен с вторым входом элемента ИЛИ и с выходом блока сравнения, являющимся управляющим выходом формирователя, выход элемента 2И-ИЛИ соединен с первыми входами первого, второго сумматоров, выход первого сумматора соединен со своим вторым входом и с первым входом блока сравнения, второй вход которого соединен с выходом третьего сумматора, его первым входом, с первым входом сумматора-вычитателя, второй . вход которого соединен с выходом и вторым входом второго сумматора, второй вход формирователя соединен со счетньм входом счетчика частоты, выход которого соединен с вторым входом третьего сумматора, выход элемента ИЛИ соединен с тактовым входом второго сумматора непосредственно, а через второй элемент задержки с тактовым входом первого сумматора, входы установки первого, второго, третьего сумматоров и сумматора-вычитателя -объединены и являются входом установки формирователя, первый вход формирователя соединен с тактовыми входами сумматора-вычитателя, блока сравнения непосредственно, с тактовыми входами третьего сумматора через третий элемент задержки, выход сумматора-вычитателя является информационным выходом формирователя.

2t1

r

m

-...

21j

т

Д Jm

--,u

JV

()

dl

f23.J..

Ф«г.5

| название | год | авторы | номер документа |

|---|---|---|---|

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Функциональный преобразователь | 1986 |

|

SU1352476A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2446454C1 |

| Устройство для деления | 1984 |

|

SU1259251A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 1997 |

|

RU2111528C1 |

| Программируемая линия задержки | 1986 |

|

SU1406753A1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2459241C1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| РАДИОЛОКАЦИОННАЯ СТАНЦИЯ | 1993 |

|

RU2037842C1 |

| ЦИФРОВОЕ ПРОГНОЗИРУЮЩЕЕ УСТРОЙСТВО | 2011 |

|

RU2477887C1 |

Изобретение относится к импульсной технике и может быть использовано в автоматизированных системах контроля и управления, а также для анализаторов и синтезаторов сигналов в радиофизике, океанологии, системах связи. Цель изобретения - повьшение г т 1Лп быстродействия достигается за счет введения нового процесса формирования кодов с уменьшением времени между микрокомандами останова. Цифровой генератор содержит регистры 1 и 2 числа, двухразрядный регистр 3 сдвига, регистр 4 микрокоманд останова, элементы ИЛИ 5, 6 и 13, 14, регистры 7 и 8 сдвига, первую группу элементов И 9 и 10, преобразователь 11 код - частота, блок 12 синхронизации, элементы И 15 и 16, счетчик 17 аргумента, элементы 18 и 19 задержки, формирователь 20 адреса, блок 21 К счетчиков, мультиплексор 22, сумма- тор 23 по модулю 2, переключатель 24 с входами 25 и 26. 1 з. П. ф-лы. 5 ил. (Л с 00 4; 1 а

V

Фиг.

)

Редактор В. Данко

5127/51

Тираж 899 ВНРШПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно

-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Составитель Ю. Сибиряк Техред И.Попович

Корректор А. Тяско

Подписное

| Цифровой генератор сигналов | 1984 |

|

SU1176442A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-10-23—Публикация

1986-02-14—Подача